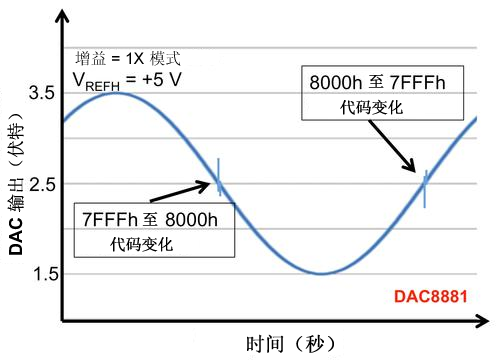

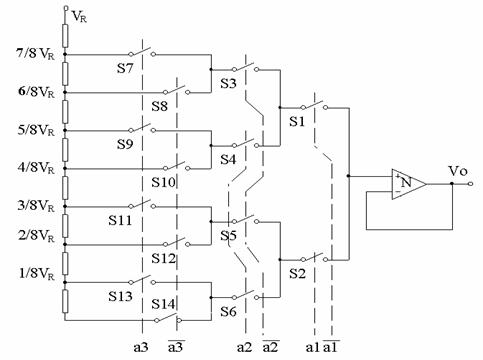

在电源电压超过±5V的R-2R DAC设计中,DAC的主要进位转换期间可能会出现较大的电压毛刺(高达1.5V)。这些毛刺会传播到输出缓冲放大器,并出现在输出端。控制顶部 (VREF+) 和底部 (VREF-) 单刀双掷开关(S0 至 SN)的电平转换器的回转会导致毛刺(图 1)。如果“反相”R-2R梯形图的每个开关都瞬间打开和/或关闭,则DAC输出(或输出缓冲放大器的输入)的毛刺幅度将很小。但是,开关不会瞬时切换;事实上,为了避免两个基准电压缓冲器的输出之间产生撬棍电流,开关采用先开后合连接。相关的时间延迟会在DAC代码转换期间产生非常大的毛刺,从而降低动态性能规格“毛刺脉冲能量”。

图1.简化的DAC电路。

降低毛刺能量的一种方法是在DAC输出和地之间连接一个大电容。R的低通滤波器组合代数转换器C降低毛刺的幅度。但是,为了显着减少毛刺,电容值必须很大。因此,这种方法大大增加了DAC的建立时间。

另一种去毛刺技术是在DAC输出之后使用外部采样保持(T/H)放大器。这种方法的一个优点是可以完全消除DAC输出的毛刺(原则上)。但是,除了T/H放大器之外,还需要外部单次和去毛刺时序控制逻辑。因此,DAC、去毛刺时序控制电路和T/H放大器之间的接口可能相当繁琐。

将 T/H 放大器与 DAC 集成在同一芯片上,可消除繁琐的接口(图 2)。去毛刺T/H放大器紧跟在缓冲DAC输出之后。利用这种技术,开发了一种智能去毛刺电路,在不增加建立时间的情况下显著降低了数模毛刺脉冲能量。

图2.集成 T/H 抗干扰架构。

智能DAC去毛刺电路

由于毛刺在DAC更新后立即发生,并在前几微秒内消失,如果DAC输出和输出缓冲放大器输入在DAC更新时去耦并保持去耦,直到毛刺消失,则毛刺将不会通过输出缓冲放大器。如图2所示,该解决方案使用T/H概念来消除毛刺。在更新DAC之前,开关SW1关闭。采样电容对先前DAC代码的直流电平进行采样。在数字代码转换期间,当DAC更新时,开关断开,电容(CH) 保持先前 DAC 代码的直流电平。发生毛刺时,放大器输出保持在此直流电平。故障消失后,开关再次关闭。与上一节讨论的低通滤波器技术不同,T/H电容的值可以小得多,因为该电容用于保持先前DAC代码的直流电平,而不是降低毛刺幅度。当T/H开关由于电荷共享和注入而打开或关闭时,仍会出现小毛刺,但相关的毛刺幅度要小得多。

实现技术

虽然将DAC输出放大器与T/H组合在直观上看起来很明显,但这在实际实现过程中带来了一些设计挑战。例如,在某些应用中,需要较大的DAC输出摆幅。因此,采样开关(SW1)必须在高压电位下工作。这一要求将T/H实现限制在少数具有所需高击穿电压MOS开关的工艺中。另一个挑战是,输出放大器双极性输入对的基极电流会在开关(SW1)上产生失调电压(IBASE×RSW)。最后,电荷注入和时钟馈通是需要考虑的其他T/H电路规格。

改进的去毛刺电路

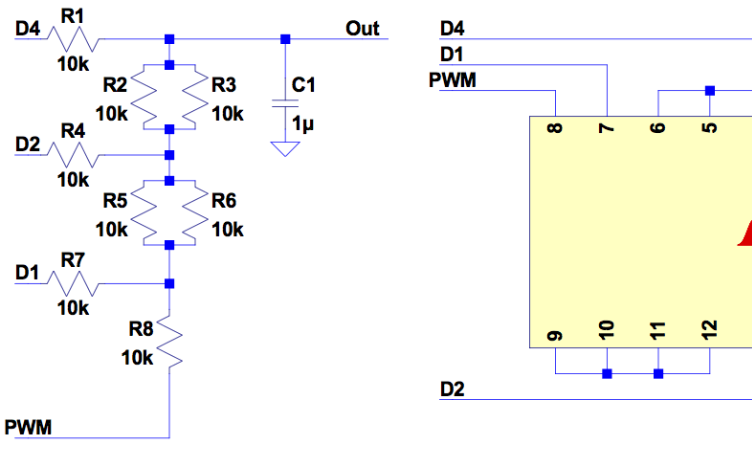

当DAC输出之后有一个单位增益缓冲放大器时,采样开关必须具有高击穿电压。但是,如果放大器的增益大于1(n>3),则所需的开关击穿电压将降低n倍。这有助于放宽与DAC和开关相关的工艺要求。图<>显示了该电路的架构。

图3.改进的去毛刺电路。

将 VSW 指定为控制采样开关的开关电压,过程击穿电压 (VBREAKDOWN) 限制了 VSW 的最大值。通过设置 n>Vout (最小值/最大值)/VVBREAKDOWN,可以缓解高压问题。

消除由非零基极电流引起的失调

为了消除采样开关的基极电流,可以使用差分电荷消除,如图4所示。

图4.差分电荷消除。

西 南部2等于软件1,并且两者都看到相同的阻抗。等效电阻等于R,等效电容等于CH.

这种架构提高了电路性能;然而,仍有一些问题需要解决。一、当软件1和软件2均开路,输出放大器没有反馈路径;放大器工作开环。其次,放大器反相输入端的保持电容会导致额外的相移,从而降低运算放大器的相位裕量(PM)。

用于去毛刺电路的零极点架构

只需稍微改变放大器反馈网络,电路就可以解决相移问题。如图5所示,开关SW1和SW2两侧的等效阻抗匹配。该电路有效地在放大器反馈网络中的极点位置增加了一个零点,以补偿增加的相移和图4所示的相裕量减小。

图5.完整的架构。

使用此配置时,V 没有相移外到 V店-.当软件2打开,C1和 C2保持负面反馈。对于极点零点消除,等效反馈网络如图6所示。

图6.反馈网络的等效电路。

从数学上讲,该电路的优点,即极点零点消除,推导如下:

测试结果

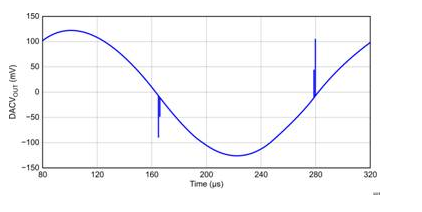

这种用于电压DAC技术的智能去毛刺电路目前用于MAX5839,这是一款13位、八通道、高压DAC。测试测量表明,数模毛刺能量比市场上其他器件小10倍。下图显示了测试结果。

图7.大进位转换期间的毛刺幅度。

结论

在去毛刺电路中使用T/H放大器技术,我们在主要进位转换期间在DAC输出端实现了非常小的毛刺(通常为10mV至20mV)。通过在RC反馈网络中实现极点零点消除,消除了保持电容引起的额外相移,并保持了输出放大器的稳定性。当采样开关断开时,仍然通过电容C1和C2采用负反馈。此外,基极电流消除消除了由于RSW×Ibase引起的电压失调。最后,通过正确选择输出放大器的增益“n”,我们可以使用工艺约束(否则可能会使设计复杂化)来发挥我们的优势。

审核编辑:郭婷

-

放大器

+关注

关注

143文章

13583浏览量

213363 -

转换器

+关注

关注

27文章

8694浏览量

147081 -

dac

+关注

关注

43文章

2291浏览量

190971

发布评论请先 登录

相关推荐

令人困扰的DAC输出短时毛刺脉冲干扰

利用PWM和小型R-2R梯形DAC达到减小纹波和提高分辨率的效果

将PWM与小型R-2R梯形结合可以改善两者。它可以显着降低PWM纹波并提高DAC的分辨率

电阻器梯形结构:R-2R DAC与MDAC架构

该设计可减少DAC R-2R架构干扰

使用FPGA驱动R-2R电路输出正弦波资料分享

乘法DAC-固定参考信号的波形发生应用

令人困扰的DAC输出毛刺消灭记

基于R/C滤波器DAC去干扰电路设计

实现DA转换器双极性电压输出的双R-2R电阻网络结构

两种非常相似的架构:R-2R DAC 与 MDAC

一文解析ADC/DAC架构

高压R-2R DAC的去毛刺技术

高压R-2R DAC的去毛刺技术

评论