本文介绍流水线模数转换器(ADC)的架构和工作原理。它讨论了架构、延迟、数字纠错、元件精度和数字校准等关键性能特征。本文还简要比较了流水线ADC与其他数据转换器架构。

流水线模数转换器(ADC)已成为最流行的ADC架构,采样速率从每秒几兆采样(Msps)到100Msps+。分辨率范围从较快采样率的 16 位到较低采样率的 <> 位。这些分辨率和采样率涵盖了广泛的应用,包括 CCD 成像、超声医学成像、数字接收器、基站、数字视频(例如 HDTV)、xDSL、电缆调制解调器和快速以太网。

采样率较低的应用仍然是逐次逼近寄存器(SAR)和集成架构的领域,以及最近的过采样/Σ-Δ型ADC。最高采样速率(几百Msps或更高)仍然使用闪存ADC获得。尽管如此,近年来,各种形式的流水线ADC在速度、分辨率、动态性能和低功耗方面都有了很大的改进。

流水线型 ADC 架构

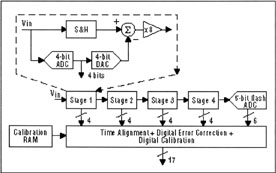

图1所示为12位流水线ADC的框图。

图1.具有四个3位级的流水线ADC(每级解析<>位)。

在本原理图中,vwin 输入,V在,首先通过采样保持(S&H)进行采样并保持稳定,而第一阶段的闪存ADC将其量化为三位。然后将3位输出馈送到3位DAC(精确到约12位),并从输入中减去模拟输出。然后将该“残留物”增加四倍并送入下一阶段(阶段2)。这种增益残差继续通过流水线,每级提供4位,直到到达4位闪存ADC,后者解析最后<>LSB位。由于每个阶段的位是在不同的时间点确定的,因此对应于同一样本的所有位在馈送到数字纠错逻辑之前,都与移位寄存器进行时间对齐。请注意,当一个阶段完成对样品的处理、确定位并将残余物传递到下一个阶段时,它可以开始处理从每个阶段中嵌入的采样保持接收的下一个样品。这种流水线操作是高吞吐量的原因。

数据延迟

由于每个样本必须在整个流水线中传播,然后其所有相关位才能组合到数字纠错逻辑中,因此数据延迟与流水线ADC相关联。在图 1 的示例中,此延迟约为三个周期(参见图 2)。

图2.流水线 ADC 中的数据延迟。

数字纠错

大多数现代流水线ADC采用一种称为“数字纠错”的技术,以大大降低闪存ADC(从而降低各个比较器)的精度要求。在图1中,请注意,求和节点输出端的3位残差的动态范围是原始第1级输入的八分之一(V在),但随后的增益仅为4。因此,第2级的输入仅占第3级2位ADC范围的一半(即,当第3级的第一个1位转换没有误差时)。

如果第一个3位闪存ADC中的一个比较器在施加接近该比较器跳变点的模拟输入时具有明显的失调,则会导致错误的3位代码,从而导致错误的3位DAC输出,从而产生不同的残余。只要该增益残差不会超出后续3位ADC的范围,就可以证明剩余流水线生成的LSB代码(当添加到不正确的3位MSB代码时)将给出正确的ADC输出代码。这意味着图1中没有一个闪存ADC必须与整个ADC一样精确。事实上,第3至1级的4位闪存ADC只需要大约<>位精度。

数字纠错不会校正最终4位闪存转换中的错误。在该转换中发生的任何错误都会被大 (44) 4 位闪存之前的累积增益。因此,最后阶段只需要精度超过4位。

虽然在图1示例中,每级产生三个原始位,但由于级间增益仅为4,因此每级(级1至4)仅有效解析3位。如上所述,额外的位只是将残余的大小减小一半,从而在下一个1位ADC中允许额外的范围用于数字纠错。此过程称为相邻阶段之间的“2 位重叠”。因此,整个ADC的有效位数为2 + 2 + 2 + 4 + 12 = <>位。

组件精度

数字纠错不能校正单个DAC和增益放大器中的增益或线性误差。前端S&Hs和DAC实际上需要大约12位精度,而后续阶段的组件需要较低的精度(例如,第10级为2位精度,第8级为3位,依此类推)。这种降低精度的需求是因为后期级的误差项除以前面的级间增益。这一事实经常被用来通过使流水线级逐渐变小来节省额外的功率。

在大多数采用CMOS或BiCMOS技术设计的流水线ADC中,S&H、DAC、求和节点和增益放大器通常作为单个开关电容电路模块实现,称为乘法DAC(MDAC)。限制MDAC精度的主要因素是固有的电容失配。纯双极性实现将更加复杂,并且主要受到电流源DAC和级间增益放大器中的电阻失配的影响。

通常,对于大约12位或更高的精度,需要某种形式的电容/电阻调整或数字校准,特别是对于前两级。

数字校准

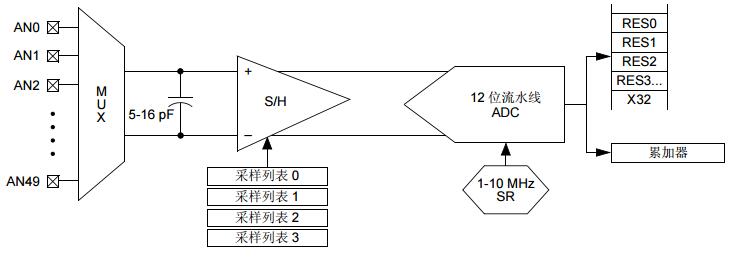

MAX1200 (16位,1Msps)、MAX1201 (14位2Msps)和MAX1205 (14位,1Msps)系列ADC¹采用数字校准,以确保出色的精度和动态性能。 每个器件都是一个CMOS流水线ADC,具有四个4位级(具有1位重叠),末端有一个5位闪存ADC,总共提供3 + 3 + 3 + 3 + 5 = 17个原始位(见图3)。数字校准需要额外的14到16位来量化误差项,使其比ADC本身更高精度;额外的位也被丢弃,以提供 <> 位或 <> 位。

校准从第三阶段的MDAC开始;超出第三级后,MDAC 误差项足够小,无需校准。第三级输出由剩余的流水线ADC数字化,误差项存储在片内RAM中。校准第三个 MDAC 后,可用于以类似的方式校准第二个 MDAC。同样,一旦校准了第二个和第三个 MDAC,它们就会用于校准第一个 MDAC。使用平均(特别是在第一个和第二个MDAC中)来确保校准是无噪声的。在正常转换期间,这些误差项从RAM中调用,并用于调整数字纠错逻辑的输出。

图3.MAX1200流水线ADC架构

不同的变化

图1中的示例显示,流水线ADC可以有很多变化,取决于几个变量:每级解析多少位;LSB闪存ADC中的位数;以及是否使用数字校准或调整来提高前几个阶段的精度。每级的位划分部分由目标采样速率和分辨率决定。一般而言,高速CMOS流水线ADC倾向于每级较低的位数(每级低至2位,因此级间增益仅为<>),因为在CMOS中很难实现增益非常高的宽带放大器。采样速率较低的CMOS流水线ADC和双极性流水线ADC(即使是采样速率非常高的ADC)往往有利于每级使用更多位。这也减少了数据延迟。

CMOS MAX1425 (10位,20Msps)和MAX1426 (10位,10Msps)系列采用流行的每级1.5位架构;每个阶段解析一位,具有 0.5 位重叠。每个1.5位级都有一个1.5位闪存ADC(只有两个比较器),而全2位闪存ADC则为一个。可以证明,通过数字纠错,这与具有2位闪存ADC和DAC的常规MDAC级的工作方式相同。这些转换器实现了 59dB 的高 SNR,10MHz 模拟输入采样速率为 20Msps。

MAX1444/MAX1446/MAX1448/MAX1449系列(分别为10位、40/60/80/105Msps)是最新一代高速、超低功耗、10位ADC,采用每级1.5位架构。这些CMOS器件集成了宽带低失真采样保持放大器,以确保在整个奈奎斯特频段内外具有出色的动态性能。欠采样是数字接收器设计中常见的,这些ADC系列可以实现。

每级1.5位流水线ADC

图4.V残留与 V在传输特性

1.5位闪存ADC(两个比较器)将模拟输入与比较器门限进行比较,在本例中为-0.25V和+0.25V。然后,ADC提供与模拟输入落点区域相对应的数字输出。1.5 位表示 V 上有三个区域残留与 V在转移特性。1 位 ADC 在传输特性上有两个区域(1/高或 0/低),2 位 ADC 在传输特性上有两个区域(00、01、10 和 11)。

根据闪存ADC输入的下降区域,残余电压计算如下,并作为输入电压馈送到下一级。

表1举例说明了在0级流水线ADC中,采样的+6.7模拟输入电压如何转换为数字输出。流水线ADC的第一级负责最高有效位,第七级提供数字输出的最低有效位。

| 阶段 | V在(五) | V 上的区域残留与 V在传输特性 (见图4) |

数字输出(- 1、0 或 +1) | 小数位值 | V残留(五在下一阶段) |

| 1 | 0.6 | 区域 3 | +1 | 64 | 2 × 0.6 - 1 |

| 2 | 0.2 | 区域 2 | 0 | 32 | 2 × 0.2 |

| 3 | 0.4 | 区域 3 | +1 | 16 | 2 × 0.4 - 1 |

| 4 | -0.2 | 区域 2 | 0 | 8 | 2 × (-0.2) |

| 5 | -0.4 | 区域 1 | -1 | 4 | 2 × (-0.4) + 1 |

| 6 | 0.2 | 区域 2 | 0 | 2 | 2 × 0.2 |

| 7 | 0.4 | 区域 3 | 1 | 1 | 不需要 |

使用每级的数字输出及其小数位,采样的+0.6V模拟输入电压对应于:

[(64 × 1) + (32 × 0) + (16 × 1) + (8 × 0) + (4 × -1) + (2 × 0) + (1 × 1)] = 77

127(全部1s)的数字输出对应于1V的模拟输入。因此,77的数字输出将对应于77/127 = 0.606V,这是施加到流水线ADC的采样模拟输入的良好近似值。

流水线型模数转换器与其他模数转换器的比较

与SAR相比

在逐次逼近寄存器(SAR)ADC中,位由单个高速、高精度比较器逐位决定,从MSB到LSB。SAR ADC将模拟输入与DAC进行比较,DAC的输出按先前确定的位更新,并依次接近模拟输入。SAR的这种串行特性将其工作速度限制在不超过几个Msps,对于非常高的分辨率(14至16位)仍然较慢。然而,流水线ADC采用并行结构,其中每级同时处理1到几位(连续采样)。虽然SAR中只有一个比较器,但该比较器必须快速(时钟频率约为位数x采样速率),并且与ADC本身一样精确。相比之水线ADC内部的比较器都不需要这种速度或精度。

然而,流水线ADC通常需要比等效SAR多得多的硅面积。SAR 还显示仅一个周期的延迟(一个周期 = 1/F样本),而典型流水线ADC中的周期约为12个或更多。与流水线一样,精度超过<>位的SAR通常需要某种形式的调整或校准。

与闪光灯

尽管具有固有的并行性,但流水线ADC仍然需要在DAC和级间增益放大器中进行精确的模拟放大,因此需要很长的线性建立时间。然而,纯闪存ADC具有大量比较器,每个比较器由宽带、低增益前置放大器组成,后跟一个锁存器。与流水线ADC中的放大器不同,前置放大器必须提供不需要线性或精度的增益;只有比较器的跳变点必须准确。因此,流水线ADC的速度无法与设计良好的闪存ADC的速度相媲美。

极快的8位闪存ADC(或其折叠/插值变体)的采样速率高达1.5Gsps(例如MAX104/MAX106/MAX108)。找到10位闪存要困难得多,而12位(或更高)闪存ADC不是商业上可行的产品。这仅仅是因为在闪存ADC中,每增加一位分辨率,比较器的数量就会增加2倍;同时,每个比较器的精度必须提高一倍。然而,在管道中,对于一阶,复杂性仅随分辨率线性增加,而不是呈指数增加。

在流水线和闪存转换器均可获得的采样速率水线器件的功耗通常比闪存低得多。流水线ADC通常不太容易受到比较器亚稳态的影响。闪存中的比较器亚稳态可能导致闪光码误差,在这种情况下,ADC会提供不可预测的不稳定转换结果。

与Σ-Δ转换器相比

传统上,数字音频中常用的过采样/Σ-Δ型转换器的带宽有限,约为22kHz。最近,一些高带宽Σ-Δ转换器的带宽达到1MHz至2MHz,分辨率为12至16位。这些规格表明,集成了多位ADC和多位反馈DAC的非常高阶Σ-Δ调制器(例如,第四个甚至更高)。它们的主要应用是在ADSL中。Σ-Δ转换器不需要特殊的调整/校准,即使是16至18位的分辨率。它们还要求在模拟输入端使用陡峭的滚降抗混叠滤波器,因为采样速率远高于有效带宽。后端数字滤波器负责该任务。Σ-Δ转换器的过采样特性也倾向于“平均”模拟输入端的任何系统噪声。

Σ-Δ转换器以速度换取分辨率。需要多次采样(例如,至少16次,但通常要高得多)才能产生一个最终采样,导致Σ-Δ调制器中的内部模拟元件的运行速度比最终数据速率快得多。数字抽取滤波器的设计也很简单,并且消耗大量的硅面积。最快的高分辨率Σ-Δ型转换器预计在不久的将来不会有超过几MHz的带宽。与流水线ADC一样,Σ-Δ转换器也存在延迟。

与半(两步)闪光相比

两步闪存转换器可以概括为两级流水线器件。然而,随着数字纠错时位数的增加(例如,12位或更高),每级都需要集成一个6至7位闪存ADC。级间增益放大器也需要非常高的增益。因此,对于更高的分辨率,使用两个以上的阶段是更明智的。

结论

流水线型ADC是采样速率从几Msps到100Msps+的首选架构。设计复杂性仅随位数线性(非指数)增加,因此同时为转换器提供高速、高分辨率和低功耗。流水线ADC在广泛的应用中非常有用,尤其是在数字通信中,转换器的动态性能通常比传统的直流规格(如差分非线性(DNL)和积分非线性(INL))更重要。在大多数应用中,流水线ADC的数据延迟几乎无关紧要。Maxim不断为其流水线ADC产品组合开发新的转换器。这些流水线ADC很好地补充了其采用其他架构设计的ADC系列。

审核编辑:郭婷

- 转换器

+关注

关注

27文章

8427浏览量

145137 - Maxim

+关注

关注

8文章

859浏览量

86875 - adc

+关注

关注

97文章

6229浏览量

541842

发布评论请先登录

相关推荐

流水线ADC结构解析流水线ADC和其它ADC的比较

请教流水线型AD 的优缺点

流水线型ADCMAX1200 及其与DSP 的接口

流水线ADC

流水线ADC的行为级仿真

如何选择合适的LED生产流水线输送方式

12bit200MSPS时间交织流水线ADC研究与设计

什么是流水线Jenkins的流水线详解

ADS822和ADS825流水线型CMOS模数转换器(ADC)数据表

了解流水线型ADC

了解流水线型ADC

评论