反激式 DC-DC 转换器拓扑结构可显著节省多个输出电源的成本和空间,这些电源具有高达 100W 的高输出电压。反激式拓扑使用变压器存储和传输能量,由于物理限制,变压器在开关周期内会导致较大的电压瞬态尖峰。本文概述了可用于抑制初级侧和次级侧的这些瞬变的耗散电压抑制电路(电压缓冲器)的设计。

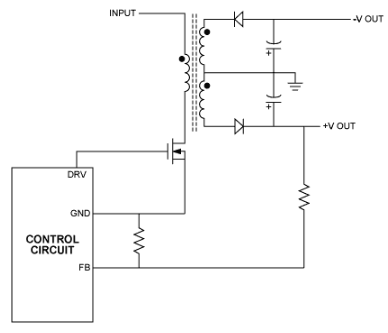

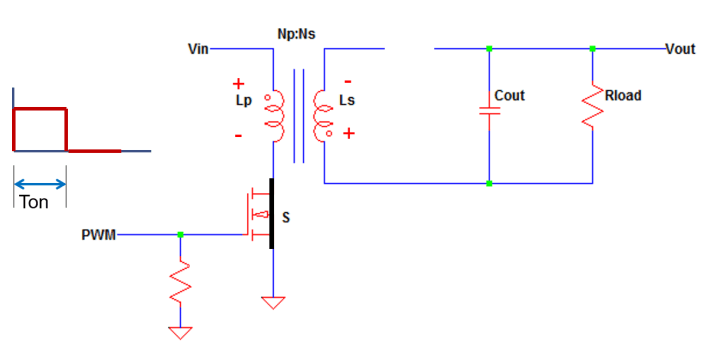

反激式拓扑(图 1A)可为具有高输出电压的多个输出电源节省大量成本和空间,功率水平高达 100W。这种拓扑使用变压器,变压器本质上是一个耦合电感器,在同一磁芯上有多个绕组。反激式拓扑的工作原理是在电源开关导通期间将能量存储在变压器中,并在关断期间将该能量传输到输出。能量存储在与变压器铁芯串联的非磁性间隙中。实际上,由于绕组之间的物理分离,多个绕组不能都同样很好地耦合到磁芯。少量能量也存储在这些绕组内部和之间。该能量在电路中表示为漏感(图 1B)。

图 1A.反激式电路的基本拓扑结构。

图 1B.等效变压器模型。

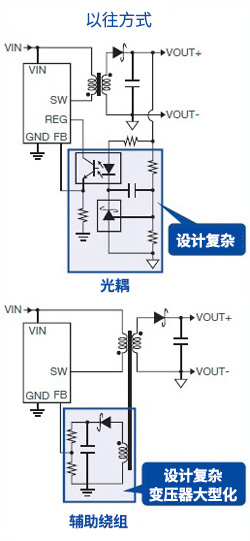

反激式拓扑对于多个输出电源很有吸引力,因为输出电压会随着线路和负载的变化而相互跟踪,并且向系统添加输出不需要额外的IC。尽管有其优点,但反激式的缺点是电源开关漏极和次级整流器处的瞬态电压尖峰较大。这些尖峰是反激式变压器漏感的函数。缓冲器控制漏感的影响,提高电源的可靠性。

缓冲器可以是被动网络,也可以是主动网络。无源缓冲器网络元件仅限于电阻器、电容器、电感器和二极管。无源缓冲器可以控制电压或电流,可以是耗散的,也可以是非耗散的。如果缓冲器中的能量在电阻元件中耗散,则将其归类为耗散缓冲器,但如果能量返回到输入或向前移动到输出,则将其归类为非耗散。本应用笔记概述了所使用的不同类型的无源耗散电压缓冲器、设计指南及其各种限制。特别是,讨论了用于减少开关应力和提高反激式拓扑效率的缓冲器。

第一部分列举了反激式转换器初级侧需要缓冲器。第二部分解释了输出侧需要缓冲器。接下来将讨论各种类型的耗散电压缓冲器。

初级漏感和 MOSFET 开关

初级漏感LLP在飞返中不参与一次到二次能量的转移,因此对效率有负面影响。由于漏感找不到开关导通期间积聚电流的路径,因此在MOSFET关断时会导致电压尖峰,并且还会延迟功率从初级到次级的传输。变压器和开关中的寄生元件决定了该电压尖峰的大小。在高输出电压下,电路寄生效应相对于输出功率量变大。

初级漏感,LLP,以及变压器中的初级绕组电容,CP,输出电容C开放源码软件,MOSFET形成寄生LC网络。峰值电压由下式给出:

VPEAK = IP (√(LLP/(CP+COSS))) + VIN + VOUT/N

其中IP是 MOSFET 关断时循环的电流电平,N 是次级匝数与初级匝数的比率,V在为输入电压,V外是输出电压。

上式中的平方根项表示寄生LC网络的特性阻抗。请注意,当切换最高电流水平时,会发生最高电压瞬变。这种电压过冲可能导致MOSFET中的功率耗散过大,即使它在器件的安全工作限值内,也会降低总效率。此外,由于瞬态电压尖峰导致 (dv/dt) 引起的 MOSFET 杂散导通,它可能会导致环路不稳定。

次级漏感和整流二极管

变压器次级漏感可能与反向恢复电流I娱乐的输出整流二极管在二极管关闭时引起振铃。变压器二次漏感LLS和电容CD的整流器确定此谐振频率。振铃可能会产生明显的辐射和传导噪声。谐振电路中的损耗通常很小,因此该网络在尖峰之后会导致许多振铃周期。因此,振铃会影响控制器在反激式配置中使用的电流检测信号。这种振铃引起的过冲可能会超过二极管额定电压并损坏二极管。整流器两端的最大正电压可以估算为

V峰值,S= I娱乐√(LLS/CD)+ V在× N

谐振电路的阻尼应进行优化,因为过度阻尼也会导致开关时间增加并导致损耗增加。

因此,可以使用缓冲器来箝位电压尖峰或抑制振铃,以降低系统中的噪声,或两者兼而有之。根据缓冲器执行的功能,它可以大致分为三类:

上升速率控制缓冲器

电压钳缓冲器

阻尼缓冲器

根据定义,阻尼缓冲器是耗散的。上升速率控制缓冲器和电压钳位缓冲器可以是耗散的,也可以是非耗散的。非耗散型缓冲器一般为谐振型缓冲器。缓冲器也可以分为极化或非极化,具体取决于能量是在开关边沿还是在两个开关边沿移入或移出缓冲器。极化缓冲器不太擅长阻尼,因为它在大部分周期中都不活跃。它通常提供上升速率控制或箝位。根据被控制的参数是电压还是电流,这些缓冲器可以进一步分类为电压或电流缓冲器。本应用笔记仅讨论耗散型电压缓冲器。

RCD 电压缓冲器

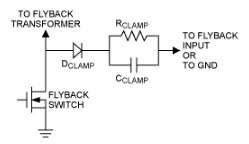

该缓冲器适用于上升速率电压控制和/或箝位。二极管在配置中的存在使其成为极化缓冲器。该电阻-电容-二极管(RCD)缓冲器的两种可能配置如图2所示。图2A所示的配置只能用作电压钳位。图2B所示的变化适用于上升速率控制或开关漏极电压的钳位。

图 2A.电压钳缓冲器。

图 2B.上升速率电压缓冲器。

RCD 夹具

在箝位模式下,缓冲器的目的是在MOSFET漏极关断期间箝位电压。并联RC电路可以返回到地或地以外的电压(即,如果漏极可以高于输入电压,则为输入电压),因为这将降低电阻中的功耗。MOSFET开关本身必须在关断期间维持峰值功耗。电容器的值,C钳和电阻器,R钳,基于寄生电感中存储的能量,因为该能量必须在每个周期内放电到RC网络中。电容器和电阻两端的电压设定箝位电压 V钳.MOSFET开关漏极处的关断波形如图3所示。

图3.带箝位的 MOSFET 关断波形。

这意味着关断时箝位中的功耗为

PCLAMP = (1/2) × VCLAMP × ICLAMP × Δt × f

其中,f是开关频率。

然而

Δt = (LLP × IP)/(VCLAMP - VOUT/N).

箝位中的功耗通过电阻。因此

RCLAMP = [2 × VCLAMP × (VCLAMP - VOUT/N)]/( LLP × IP2 × f)

重要的是最小化纹波,V脉动,叠加在 V 上钳使 MOSFET 漏极电压接近箝位电压。电容器的最小值 C钳,因此为 C钳= V钳/ (V脉动×·钳×f)。

电容器,C钳,应具有低ESR和低电感,以处理关断期间的高峰值电流。箝位的RC时间常数应选择远大于MOSFET的开关周期。箝位中使用的串联二极管应能够处理峰值电流,并且必须是快速导通型。

RC网络可以用一个可以处理额定电压和功耗的齐纳二极管代替。然而,由于齐纳二极管不是快速开关器件,因此可能仍需要与齐纳二极管并联的电容器来处理高频电流。请注意,此缓冲器不用于具有钳位感性负载的拓扑,因为它不会减少振铃。

上升速率控制RCD缓冲器

当RCD缓冲器用于控制MOSFET漏极的电压上升速率时,电容器必须在每个周期内完全充电和放电,以便能够控制漏极电压的上升速率。因此,缓冲器的RC时间常数应远小于开关周期(考虑占空比对脉冲宽度的影响)。通常,时间常数应约为 1/10千切换周期。当开关关闭时,电感电流通过缓冲二极管转移,将电容器充电至供电轨。届时,预计输出整流器将导通。

当开关导通时,缓冲电容器将通过缓冲电阻和开关放电。

电容值由IP = C (VC/ tr)

其中 VC= 电容器两端的电压和 tr= 电压的上升时间

然后根据所需的时间常数选择电阻器。RC时间常数远小于开关频率,因此,电阻中的功耗与其值无关。功耗由电容值和开关频率决定。由于只有一个通过电阻的转换(放电),电阻中的功耗由P = (CVC2f)/2.

简单的遥控缓冲器

这可能是使用最广泛的缓冲器,适用于上升速率控制和阻尼。在电感钳位拓扑中,仍然存在一些杂散电感,RC缓冲器可用于通过控制漏极电压的上升速率来降低开关中的峰值功耗。然而,RC缓冲器会在每次电压转换期间吸收能量,并可能降低效率。此外,RC 缓冲器还会降低 MOSFET 开关的开关速度。在选择 R 和 C 的值时必须小心,以优化总体性能。RC缓冲器的主要应用是抑制电路中的寄生振铃,因为反激式转换器等配置中的电感未箝位。在这些应用中,电阻值必须接近其要阻尼的寄生谐振电路的特性阻抗。选择要的缓冲电阻

R = √(Lres/Cres)

其中 L分辨率= 引起谐振的寄生电感,C分辨率= 引起谐振的寄生电容。

缓冲器的RC时间常数与开关周期相比应该很小,但与电压上升时间相比应该很长。缓冲电容必须大于寄生谐振电容,但要足够小,以尽量减少缓冲电阻中的耗散。缓冲电容通常选择至少为寄生谐振电容值的3至4倍。根据缓冲器电容,功耗可以估算为

P = C × (VC)2× f

其中C是缓冲电容,VC是缓冲电容两端的电压,f是开关频率。

注意缓冲器中使用的组件中的寄生效应非常重要,因为这些寄生效应可能导致缓冲器无效。缓冲器中使用的二极管应该能够处理较大的峰值电流,但平均电流相对较小。印刷电路板布局可能需要为这些二极管提供一些散热器面积。电容器具有串联电感,应将其最小化,以避免在电路中引入任何不必要的谐振。一些静电电容器(陶瓷和聚合物薄膜)提供极低的 ESR 和 ESL 值。电容器可以并联以降低电路电感。使用这种方法时必须小心。大电容的串联电感能够与与之并联的小电容谐振,产生的谐振电路将具有高Q值。

使用的电阻应具有非常低的电感,以避免过度的过冲和振铃。避免使用绕线电阻器。布局不应引入杂散电感,尤其是在高电流路径中。反激式转换器中使用的变压器应设计为降低漏感并最大限度地减少过冲和振铃。然而,变压器的实际设计超出了本应用笔记的范围,将在别处讨论。

电路中的开关通常是最容易受到抑制的设备。开关也位于反激电路的输入级。在实践中,最好的程序是从输入开始,然后在将缓冲器引入电路时进入输出级。一旦节点被证明需要缓冲器,则应在选择类型之前确定缓冲器的用途。

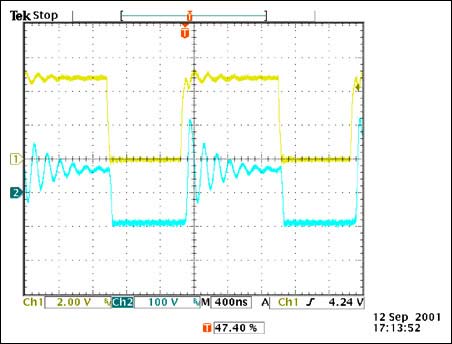

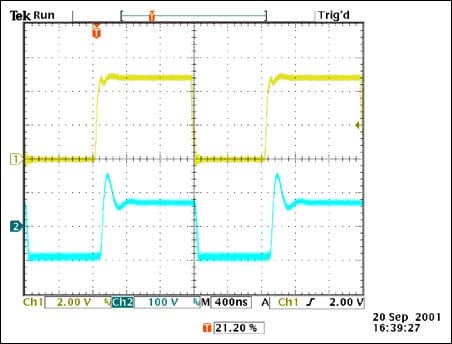

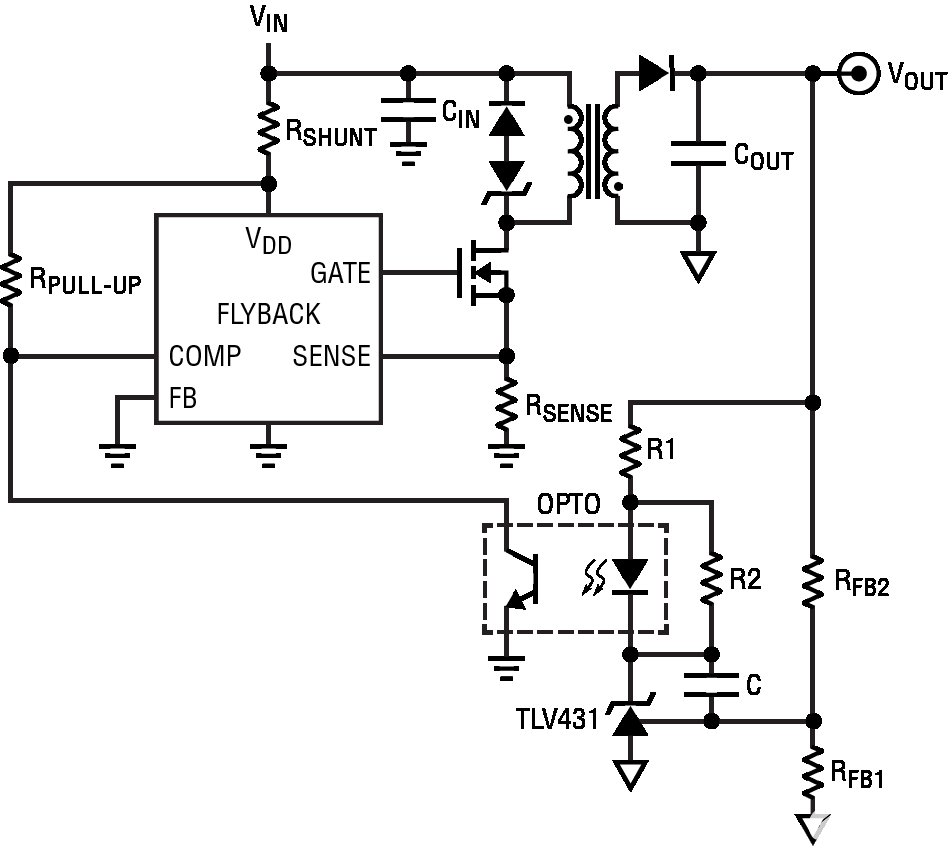

采用MAX1856的反激式拓扑应用电路如图4所示。这是将两个缓冲电路用于不同目标的示例。D3、C11 和 R11 形成一个箝位以限制漏极电压,R5 与 C10 形成一个 RC 缓冲器,以抑制次级整流器 (D2) 处的振铃。比较图5A和图5B中的波形,可以说明RC缓冲器在次级整流器上的影响。

图4.采用MAX1856的反激式应用电路

图 5A.D2整流器阴极的电压,不带缓冲器。(CH1 = MAX8分机/引脚1856处的电压波形;CH2=整流器D2的阴极)。

图 5B.带缓冲器的D2整流阴极电压(R5=150Ω;C10=330 pF)。(CH1 = MAX8分机/引脚1856处的电压波形;CH2=整流器D2的阴极)。

总之,本应用笔记讨论了无源电压缓冲器的使用,特别是反激式转换器拓扑。适当缓冲的电路更高效、更可靠,并且随着时间的推移,在温度和生产公差范围内表现良好。当需要控制开关电压瞬变时,了解和使用缓冲电路非常重要。

审核编辑:郭婷

-

转换器

+关注

关注

27文章

8694浏览量

147078 -

DC-DC

+关注

关注

30文章

1943浏览量

81603 -

变压器

+关注

关注

0文章

1126浏览量

4010

发布评论请先 登录

相关推荐

缓冲电路抑制多输出DC-DC反激式转换器电源中的电压瞬态尖峰

缓冲电路抑制多输出DC-DC反激式转换器电源中的电压瞬态尖峰

评论