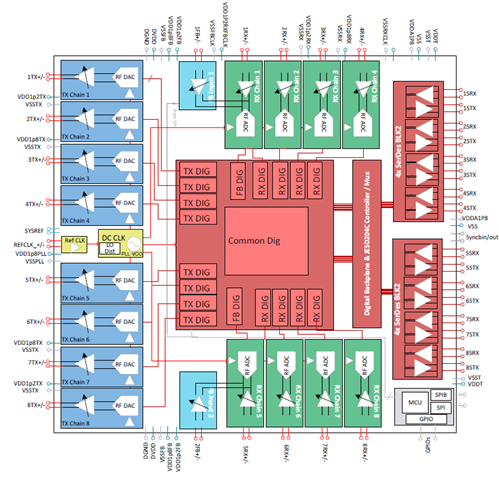

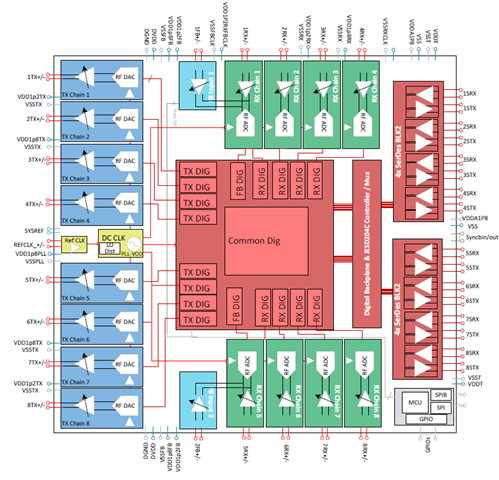

RF Transceiver芯片的集成度越来越高,AAU的射频链路的功能前移。AFE8092是TI高性能,大带宽的多通道射频收发器件,已经大规模在5G Massive MIMO射频TRX板上成功商用。它包括了8个发射通道,8个接收通道,2个反馈通道,所有通道均为射频直采架构。各个射频链路的大带宽,高性能使得AFE8092适用于大部分4G/5G基站TRX射频板应用场景。

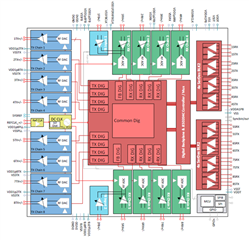

如图1所示,AFE8092的接收(RX)链路包含了4Gsps直采ADC,包含了DSA(Digital Step Attenuator)。每个接收通道数字部分包含功率监测,可以支持内部或外部的AGC控制,同时也包含RF overload功率监测,保证可靠性。发射(TX)链路包含了最高支持到12Gsps的射频直采DAC,包含DSA。也集成了功放保护(PAP)功能,防止突发大信号导致功放烧毁。同时,AFE8092支持的信号频率非常宽,可支持所有Sub 6GHz和部分高频应用。

图1 AFE8092内部模块架构框图

在5G Massive MIMO应用中,会存在下行的波束赋形及上行基于DOA(Direction of Arrival)估计的上行波束形成,这两种算法要求从基带到天线的增益及相位非常精确。但是,MIMO系统中,存在着由阵子位置、方向图等带来的增益/相位非时变误差,以及由温度、器件老化等因素带来的时变误差。因此,MIMO系统会在GP(Guard Period)时隙对上下行链路的增益及相位做周期性的校正。

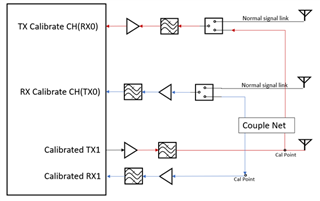

一般来说,在MIMO系统中天线校正功能的硬件连接都可以抽象为图2的结构。这里举个简单的例子:在对下行链路的增益和相位进行校正时,此时打开作为校正通道的RX链路,被校正的TX通道开始发射位于工作频点的校正信号,经由信号链路和校正网络进入校正通道,也就是RX通道,不同被校正通道发射的信号相位/频率不同,以便校正通道进行通道区分;对上行链路的增益和相位进行校正的过程和下行链路完全相反,打开作为校正通道的单个TX链路,由该链路发校正信号,由被校正的接收通道进行接收,该信号频率在RX通道频点上,以便对RX通道特性进行采集。如上的两个发射/接收校正信号行为会让系统得到链路增益/相位信息,因此可以在基带进行补偿。

图2 MIMO系统天线校正硬件单通道示意图

从上面对天线校正的简要介绍中可以看到,在天线校正过程中,是存在着业务通道临时切换成校正通道的过程的。举个例子,在正常业务场景下,TX Calibrate CH(RX0)作为业务通道,对来自天线的业务信号进行采样并送到基带进行处理。此时的DSA值在设计时未知,可能为默认值,也可能为其它的DSA值(被大信号触发了AGC),此时的接收NCO为1.8GHz。

一旦开始进行下行通道校正,该通道会作为校正通道接收来自其它发射通道发出的校正信号。此时我们希望预设一个DSA值,只有已知增益的校正链路才能用来作为整个校正系统的锚点。同时,在FDD系统中,上下行的中心频点是不一致的,我们假设这里的下行中心频点为1.9GHz,为了得到下行链路的特定频率特性,则被校正通道发射的校正信号需要落在1.9GHz,则此时要求校正通道将NCO切换到1.9GHz。

可以看到,在进行天线校正中,系统对Transceiver有4点需求:1. 使用外部触发控制Transceiver的TX/RX通道进行DSA切换;2. 使用外部触发控制Transceiver的TX/RX通道进行NCO切换;进行上面两个操作时,关闭特定射频通道进行节能;4. 使用外部触发恢复Transceiver被切换的DSA/NCO。

AFE80xx使用单个GPIO实现了DSA及NCO快速切换功能。AFE80xx使用TX_AC_EN和RX_AC_EN两个GPIO分别实现了上下行AC校正功能。下面举个例子对该功能进行说明,例子内涉及的API在后面进行细节说明。

器件初始化,下行DSA=0db, NCO=1.9G;上行DSA=3dB, NCO=1.8G。系统约定使用RX0通道作为下行校正通道,使用TX0通道作为上行校正通道。

对下行通道进行校准配置:

使用TI封装的API预设校准时需要切换的RX0 DSA=6dB, 对应的API为setRxDsaGainSwap(0,0x1, 0, 12).

使用TI封装的API预设校准时需要切换的RX0 NCO=1.9GHz,对应的API为updateRxNco(0,0x1, 0,1, 1900000,0).

使用以下三个API将TX_AC_EN的GPIO动作映射到特定通道动作上去:

CAFE.rxCalibrationTddEn(0,1)

CAFE.overrideRxGsw(0,0xfe,0,0)

CAFE.overrideRxNcoSel(0,0xfe,0,0)

对上行通道进行校准配置:

使用TI封装的API预设校准时需要切换的TX0 DSA=6dB, 对应的API为setTxDsaGainSwap(0,0x1, 0, 24).

使用TI封装的API预设校准时需要切换的TX0 NCO=1.8GHz,对应的API为updateTxNco(0,0x1, 0,1, 1800000,0).

使用以下三个API将RX_AC_EN的GPIO动作映射到特定通道动作上去:

CAFE.txCalibrationTddEn(0,1)

CAFE.overrideTxGsw(0,0xfe,0,0)

CAFE.overrideTxNcoSel(0,0xfe,0,0)

触发下行通道校准动作:

FPGA将TX_AC_EN拉高。此时,除了RX0以外的所有RX通道全部关闭,RX0的DSA被设置为6dB,NCO被设置为1.9GHz。

通道状态恢复为正常状态:

FPGA将TX_AC_EN拉低,RX0通道恢复为原始状态。

触发上行通道校准动作:

FPGA将RX_AC_EN拉高。此时,除了TX0以外的所有TX通道全部关闭,TX0的DSA被设置为6dB,NCO被设置为1.9GHz。

通道状态恢复为正常状态:

FPGA将RX_AC_EN拉低,TX0通道恢复为原始状态。

为了给客户提供更普适的配置方法,客户可以自行在初始化静态脚本中进行校正模式的配置,或者参考以下对API的说明,灵活进行配置。下表内进行说明的变量,用户可自行修改,不进行说明的变量,不建议用户自行修改。

表1. AC校正相关API注释说明

| NO | API | 说明 |

| 1 | CAFE.setRxDsaGainSwap(ID,(1< | ch - 十进制通道号,根据实际情况运算;DSA:单位为0.5dB |

| 2 | CAFE.updateRxNco(ID,0x1, 0,1, NCO,0) | NCO-NCO值,以kHz为单位 |

| 3 | CAFE.rxCalibrationTddEn(ID,(1< | ch-十进制通道号,根据实际情况运算; DSA:单位为0.125dB |

| 4 | CAFE.overrideRxGsw(ID,(0xff-(1< | |

| 5 | CAFE.overrideRxNcoSel(ID,(0xff-(1< | |

| 6 | CAFE.setTxDsaGainSwap(ID,(1< | |

| 7 | CAFE.updateTxNco(ID,0x1, 0,1, NCO,0) | NCO-NCO值,以kHz为单位 |

| 8 | CAFE.txCalibrationTddEn(ID,1) | |

| 9 | CAFE.overrideTxGsw(ID,(0xff-(1< | ch-十进制通道号,根据实际情况运算 |

| 10 | CAFE.overrideTxNcoSel(ID,(0xff-(1< |

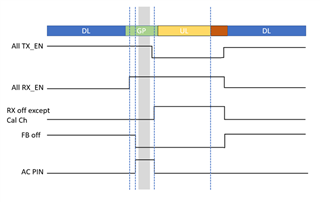

除了上文中提到的NCO和DSA值配置,在进行系统设计时,设计者也需要考虑其它通道和校正通道开关状态的配合。如下图所示,在进行下行天线校正时,我们需要确保几组通道的开关状态如下:

图3 天线校正通道时隙关系示意图

TX通道开关:全部打开,需要下行通道发射训练序列进行硬件通道特性获取

RX通道开关:全部打开,该通道开关仲裁优先级排在校正PIN以下。

FB通道开关:全部关闭,在AFE8092器件里,RX和FB通道开关状态互斥,关闭FB通道,防止RX无法打开。

AC PIN: 控制校正动作的TX_AC_EN在启用天线校正的时刻拉高。

在进行上行天线校正时,通道逻辑和下行校正类似,在此不再赘述。

审核编辑:郭婷

-

射频

+关注

关注

104文章

5573浏览量

167694 -

MIMO

+关注

关注

12文章

594浏览量

76824 -

RF

+关注

关注

65文章

3050浏览量

166958

发布评论请先 登录

相关推荐

三天线法校准方法解析

四天线接收分集的技术特点及注意问题

三天线法校准原理及系统组成

AFE8092 AGC功能中的帧同步特性详解

TI AFE8092 AFE8030 JESD204C配置及调试手册 Part B

TI AFE8092/AFE8030 JESD204C配置及调试手册 Part C

TI AFE8092 AFE8030 JESD204配置及调试手册- Part A

TI Transceiver芯片AFE8092的AGC控制方法

基于TI AFE8092的AAU TX射频链路设计分析

基于TI AFE8092的AAU RX射频链路预算分析

AFE8092天线校正功能配置方法

AFE8092天线校正功能配置方法

评论