逻辑电路主时钟

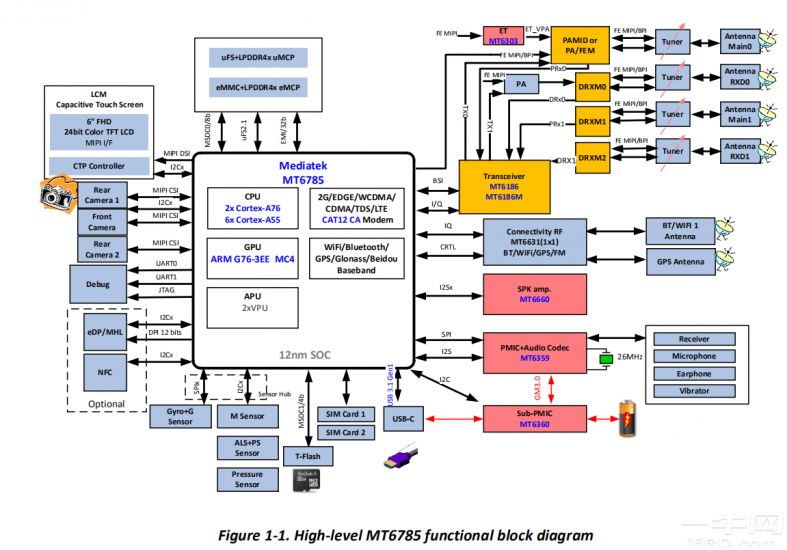

我们知道,不管哪一个平台, 要让CPU跑起来,就必须有一个主时钟,在MTK平台中,这个主时钟多为26 MHz,高通平台则为19.2MHz,其他平台,如ADI Marvel等多为13 Mhz,而在80C51系列单片机平台中,主时钟则多为11.0592 MHz。

在80C51系统中,CPU的工作频率就是11.0592 MHz,但我们知道,手机CPU的主频可不是26 MHz、19.2 MHz或者13 MHz这么低的频率。以目前的手机平台而言,CPU的主频动辄就在500MHz以上,很多甚至都已经超过1GHz。那么,CPU的主频时钟从何而来? 另外一方面,手机的RF信号,其频率高达1~2GHz左右,这些时钟又是从何而来的?

事实上,手机中的主时钟,更多的是用来作为PLL (Phase Lock Loop)电路中的参考信号的。利用PLL中的闭环负反馈原理,使得输出信号频率 与主时钟的频率构成一定关系, 如式下所示:

f out= Nf ref

f ref表示主时钟频率,fou表示PLL电路输出频率,N表示分频比(多为复数)。

对于某个确定的平台或模块,frer是 一定的,但只要对各个PLL电路设计不同的分频系数N,就会得到频率各不相同的fout。这便是在大多数手机平台中,通常只有一个fref, 却有不同fout的由来,如主时钟恒定为26 MHz,但RF TX频率却在1~2 GHz可配置。

另外,从式可以看出,只要主时钟的频率维持稳定,则输出信号频率也可以维持稳定,这也就是我们在PCB布局布线中特别重视主时钟信号隔离与保护的原因。

-

单片机

+关注

关注

6035文章

44554浏览量

634590 -

逻辑电路

+关注

关注

13文章

494浏览量

42609 -

cpu

+关注

关注

68文章

10854浏览量

211568 -

MTK

+关注

关注

2文章

182浏览量

48321 -

主时钟

+关注

关注

0文章

8浏览量

5997

发布评论请先 登录

相关推荐

异步时序逻辑电路

钟控传输门绝热逻辑电路和SRAM的设计

组合逻辑电路和时序逻辑电路比较_组合逻辑电路和时序逻辑电路有什么区别

时序逻辑电路分析有几个步骤(同步时序逻辑电路的分析方法)

什么是组合逻辑电路 如何使用verilog描述组合逻辑电路

逻辑电路主时钟的基本作用

逻辑电路主时钟的基本作用

评论