一、触发器基本概念

在电路中,触发器(Flip-flop)是一种组合逻辑电路,可以存储1个二进制位的信息。 触发器有两个稳定的状态:SET(置位)和RESET(复位)。 当输入信号满足某些条件时,触发器可以从一个状态转换到另一个状态。

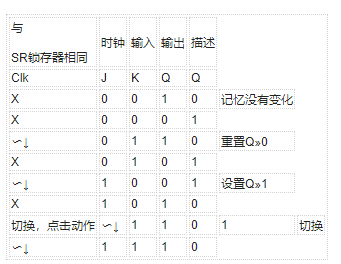

触发器通常用于存储电路中的状态或者时序信息,例如在计数器、时钟、存储器等电路中使用。 常见的触发器有SR触发器、D触发器、JK触发器和T触发器等。 不同类型的触发器有不同的输入端口和输出端口,以及不同的状态转换规则。

二、SR触发器

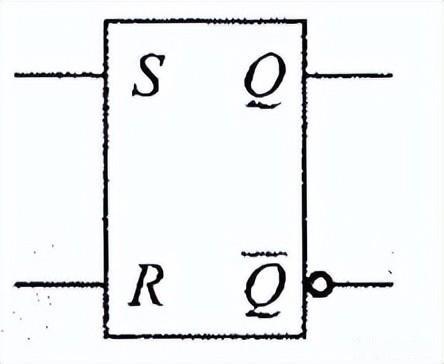

符号:

1. 基本概念

SR触发器是一种经典的数字电路元件,它的作用是将输入的信号转化为一个稳定的输出。

SR触发器是由两个互补的锁存器组成的,其中一个锁存器的输出连接到另一个锁存器的输入,反之亦然。

2. SR触发器作用

SR触发器的名称源于其两个输入端的名称:S表示“设置”(Set),R表示“复位”(Reset)。

当S和R均为低电平时,SR触发器处于稳定状态,并且输出不会改变。

当S或R的任一输入为高电平时,SR触发器会响应并产生一个输出。 在SR触发器中,输入信号可以从一个锁存器传输到另一个锁存器,实现了数据的存储和传输功能。

SR触发器常用于数字电路中的时序逻辑电路、计数器、频率分频器等电路中。 在时序逻辑电路中,SR触发器可以被用来存储上一个时钟周期的状态,从而实现状态机的设计。

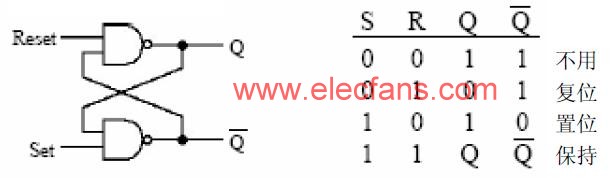

3. SR触发器的构成

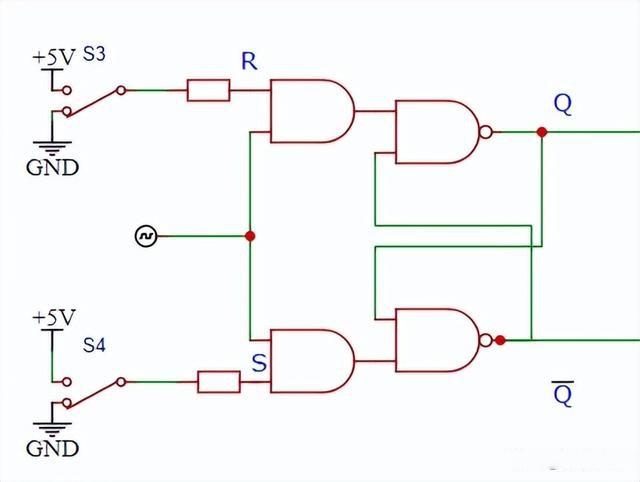

SR触发器通常由两个交叉连接的 NOR 门或两个交叉连接的 NAND 门组成。 其中一个门的输出被连接到另一个门的输入,同时该门的输入通过另一个门的输出进行反馈。

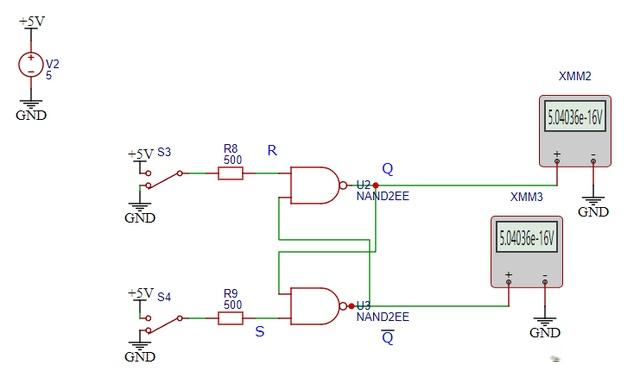

两个与门构成的SR触发器示例:

其中S称为设置位, R称为复位输入。

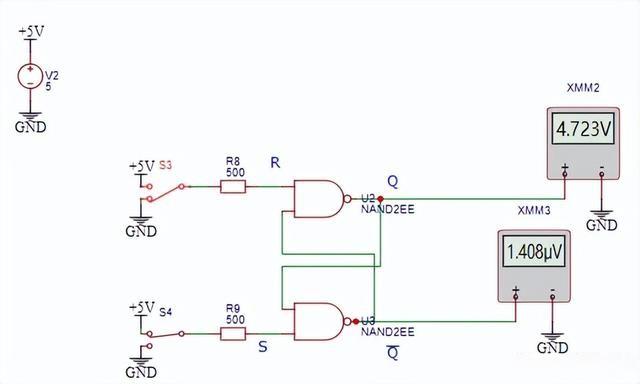

(1)S=1,R=0

这时设置位为1,输出 Q=1, Q’=0。

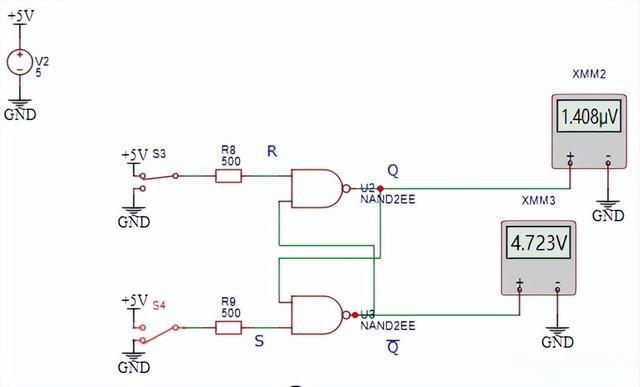

(2)S=0,R=1

这时重置位为1,Q输出被清零。

SET称为设置位,这时输出 Q=1, Q’=0。

(3)R=0,S=0

这个状态是保持状态,即在前一个状态时输出的值将保持不变。

(4)R=1,S=1

这时条件会导致输出不稳定或不可预测,是禁止条件。

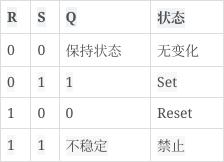

4. 真值表

三、时钟SR触发器

1. 概念

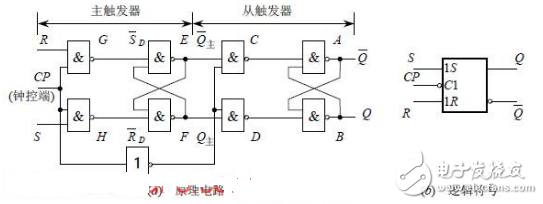

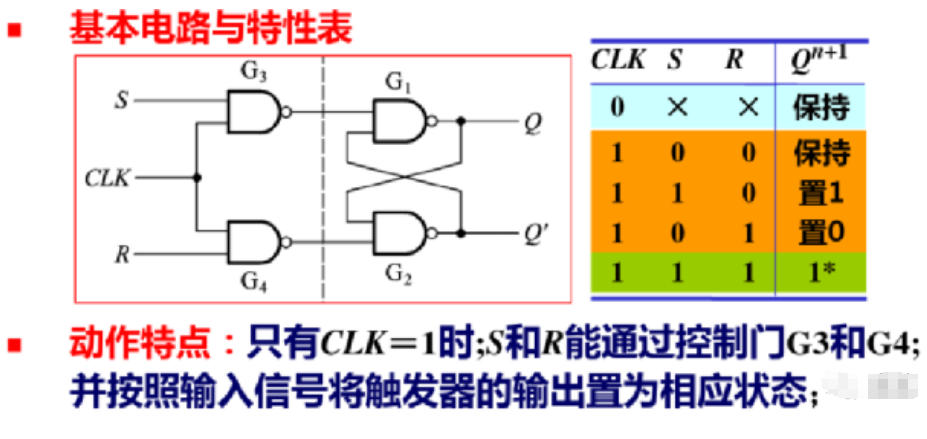

上面的简单SR触发器对控制信号的电平很敏感,一般会引入门控或时钟SR触发器。 通常所指的SR触发器,指的一般是时钟SR触发器。

时钟SR触发器(Clock SR Flip-Flop)作为数字电路中常见的触发器之一,也被称为锁存器。 它由两个交叉连接的NOR门或者两个交叉连接的NAND门构成。 该触发器的输入包括一个时钟信号(CLK)、一个复位信号(R)和一个置位信号(S)。 时钟信号 CLK 用于确定何时在输入信号改变后触发输出变化。

当CLK为高电平时,输入信号 S 和 R 的改变不会影响输出状态;

当CLK为下降沿时,此时的输入信号将会被锁定在输出中。

时钟SR触发器在数字电路中的应用非常广泛,可以用于实现存储器单元、状态机、计数器等电路。

2. NAND SR触发器原理图

时钟SR触发器一般也有基于NAND和NOR两种。 下面是构成NAND时钟SR触发器的电路示意图:

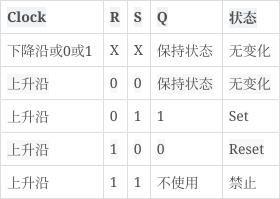

3. 真值表

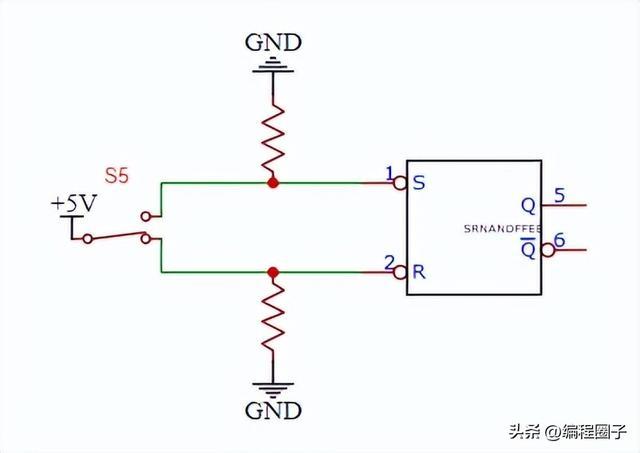

四、SR触发器应用示例

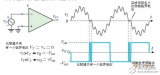

简单SR触发器常用于机械开关消抖。

该电路主要原理是,开关S触发后,如果有抖动脉冲,并不会导致输出变化,因为Q已经被置1。

只有当开关回到R,Q才被重置为0。

-

计数器

+关注

关注

32文章

2256浏览量

94476 -

时钟

+关注

关注

10文章

1733浏览量

131445 -

触发器

+关注

关注

14文章

2000浏览量

61129 -

SR触发器

+关注

关注

0文章

13浏览量

12631 -

组合逻辑电路

+关注

关注

6文章

70浏览量

14648

发布评论请先 登录

相关推荐

边沿触发SR触发器

施密特触发器电路及工作原理详解_施密特触发器特点_施密特触发器的作用

一文详解SR触发器

一文详解SR触发器

评论