R-S触发器又名复位-置位触发器(R-复位RESET,S-置位SET。),基本结构是由两个与非门(or或非门)的输入、输出端交叉连接而成。本人曾经做过一个项目,为半周期锁定的DLL(即锁相误差为π)。这个DLL使用R-S触发器当做鉴相器,来鉴别参考时钟和反馈时钟的相位差。

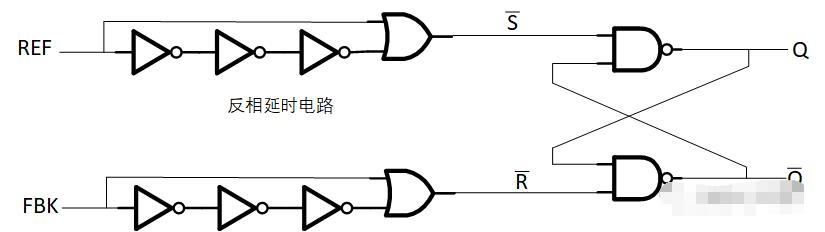

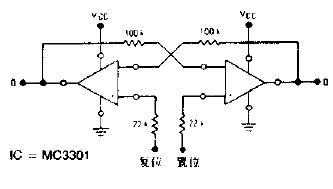

具体结构如下所示:

图1 鉴相器

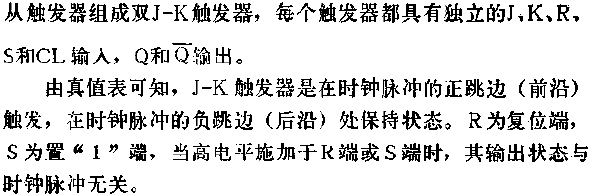

其中,R-S触发器真值表如下,置位信号和复位信号都是低有效。

| 置位端 | 复位端 | Q |

QN |

|

0 |

0 |

X |

X |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

|

1 |

1 |

保持不变 |

保持不变 |

Note:当置位端和复位端都为0,当同时撤掉0之后,输出状态是不确定的。

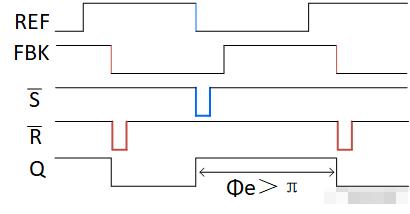

图1所示鉴相器电路。REF信号经过3级反相延时后的信号和初始信号进行逻辑或运算,得到R-S触发器的置位信号。另一边,FBK信号经过3级反相延时后的信号和初始信号进行逻辑或运算,得到R-S触发器的复位信号。R-S触发器在置位信号和复位信号控制下输出Q和QN。而Q和QN可以作为UP、DN信号驱动后级的电荷泵电路。

鉴相原理:

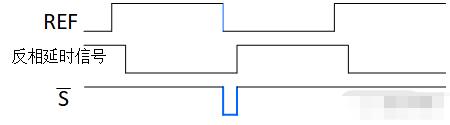

图2 :信号的边沿提取

如上图所示,以REF为例,可以看到置位信号在REF的下降沿处产生负脉冲,负脉冲的宽度约等于3级反相器的延时大小。同理,复位信号将在FBK下降沿处同样产生负脉冲。

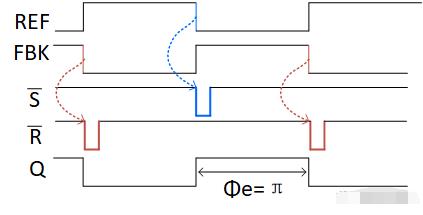

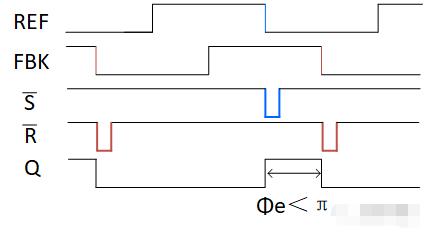

对于DLL而言,REF和FBK的频率相同,所不同的只是相位的差别。用上面提到的方法,REF和FBK所对应的每个下降沿处将产生负脉冲,因此两个负脉冲之间的宽度可以表示为相位误差。进一步利用R-S触发器的锁存特性,可以用Q的高电平宽度代表相位误差。这一点可以从下面的图片直观地表示出来。

图3:相位误差为π时

图4:相位误差<π时

图5:相位误差>π时

总结:

本文提到的鉴相器用在半周期锁定的DLL中,也就是说在半周期锁定的应用中,环路锁定状态下相位误差等于π。这一点和大多数的锁相电路不同。对于常规的DLL,一般都是整周期延时锁定,理论上锁定时的相位误差等于0。

-

dll

+关注

关注

0文章

115浏览量

45416 -

信号

+关注

关注

11文章

2789浏览量

76727 -

真值表

+关注

关注

0文章

25浏览量

15208 -

鉴相器

+关注

关注

1文章

60浏览量

23275 -

触发器

+关注

关注

14文章

2000浏览量

61130

发布评论请先 登录

相关推荐

R-S触发器的鉴相原理

R-S触发器的鉴相原理

评论