1 运行平台

硬件:CRD500数字信号处理板

系统:win7/64;win7/32;win10/64;win11/64

软件:Quartus/ModelSimSE/Verilog/Matlab

2 主要功能及性能指标

功能:

1)可产生基带码元数据

2)基带数据的成型滤波器电路

3)产生PSK调制数据

4)完成PSK解调(载波提取,相干解调)

性能:

调制端:

1)系统时钟:50MHz

2)基带数据速率:390.625kbps

3)基带成型滤波器成型系数:0.8

4) 载波频率:390.625kHz

解调端:

1)采样频率:3.125MHz

2)解调方式:Costas环提取载波,相干解调

3 程序结构框图说明

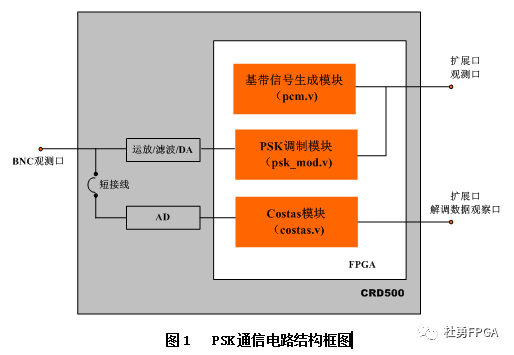

Psk调制解调电路程序主要由基带信号生成模块(pcm.v)、Psk调制模块(psk_mod.v)、Costas模块(Costas.v)组成。

基带信号生成模块(pcm.v)产生码率为390.625kbps的基带数据,送给CRD500扩展口观测的同时,送给PSK调制模块;PSK调制模块完成PSK信号调制,先对PCM基带数据进行成型滤波,控制传输频带,再与390.625kHz的载波进行相乘,完成PSK调制;PSK调制数据经CRD500板上的DA、滤波、运放模块送BNC测试口的同时,经板上短接线回至AD通道,经AD采样后回送至FPGA,由Costas模块完成相干载波提取的同时完成数据解调;解调后的数据送至CRD500的扩展口用于示波器观测。

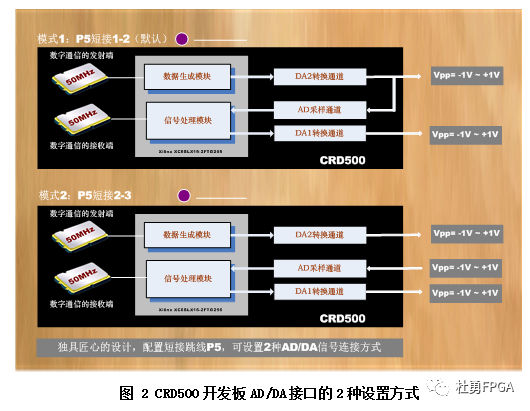

CRD500板上AD/DA接口有多种设置方式,如图2所示。

本次工程实例采用图2中的模式1连接方式。如果采用图2中的第2种模式,则需要采用双头BNC线将AD接口与DA接口连接起来。

4 测试说明

在测试过程中可以发现,上电后下载程序,输入信号及本地载波信号能够快速完成同步,数据解调正常。当按下key1键,使得costas环路无输入信号,则载波无法同步,无法解调正确,松开key1键后两路波形又自动完成同步且解调正确。

但如长时间按下key1键,偶尔会出现即使松开key1键后,两路信号仍不同步且解调不正确的情况,这是由于在环路没有输入信号时,始终处于搜索状态,环路可能出现“死循环”或“跑飞”的现象,这时只要按下复位键,则两路信号又会迅速同步,完成正常的解调。

本电路仅提供验证环路在上电或复位后完成同步锁定及解调的功能验证,不提供防止环路“跑飞”的功能程序,请用户自行完成防“跑飞”的功能程序。

审核编辑:刘清

- 滤波器

+关注

关注

158文章

7550浏览量

176252 - 示波器

+关注

关注

113文章

6044浏览量

183123 - PSK

+关注

关注

1文章

27浏览量

20931 - BNC接头

+关注

关注

0文章

12浏览量

7417

原文标题:PSK调制解调(Quartus/Verilog/CRD500)

文章出处:【微信号:杜勇FPGA,微信公众号:杜勇FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先登录

相关推荐

PSK调制解调知识简析

PSK调制解调知识简析

评论