随着各种应用场景的限制,芯片在运行时往往需要在不同的应用下切换不同的时钟源,例如低功耗和高性能模式就分别需要低频率和高频率的时钟。两个时钟源有可能是同源且频率比呈倍数关系,也有可能是不相关的。直接使用选择逻辑进行时钟切换大概率会导致分频时钟信号出现毛刺现象,所以时钟切换逻辑也需要进行特殊的处理。

时钟切换问题

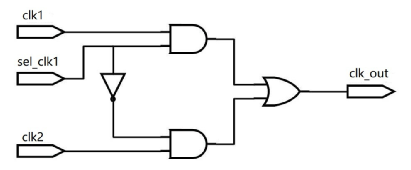

直接采用选择逻辑对时钟进行切换的电路图如下所示。

假如时钟选择信号 sel_clk1 与两个时钟都是异步的,那么时钟切换时刻就是任意的。假如时钟由 clk1 切换到 clk2,且切换时刻为 clk1 输出电平为高的时候,此时立即切换时钟就会导致输出时钟出现毛刺(glitch)。波形示意图如下:

时钟切换方案

在电平相反的时候切换时钟,肯定有毛刺;电平相同的时候,即使不产生毛刺,时钟切换后的第一个时钟的周期或占空比也不是理想的。所以,为避免毛刺的产生,需要在两个时钟都为低电平的时候进行时钟切换。

一种典型的时钟切换电路如下所示。

该电路利用时钟下降沿对时钟选择信号 sel_clk1 进行缓存。同时一个时钟选择信号对另一个时钟进行反馈控制,保证同一时刻只能有一路时钟有效。最后采用“或操作”将两路时钟合并,完成时钟切换的过程。

采用上述电路完成时钟切换(clk1->clk2)的波形示意图入戏所示。

由图可知,clk1 向 clk2 切换时,先回关闭 clk1, 然后打开 clk2。由于时钟选择信号被同步到时钟下降沿,所以切换过程中不会出现毛刺。

clk2 向 clk1 切换的波形示意图如下所示。

考虑到选择信号有可能是异步信号,需要在时钟选择信号的缓存触发器之前加两级触发器进行同步处理,来减少亚稳态的传播,结构图如下。该时钟切换电路更具有应用场景的普遍性。

时钟切换设计

普遍且安全的时钟切换逻辑描述如下。

module clk_switch(

input rstn ,

input clk1,

input clk2,

input sel_clk1 , // 1 clk1, 0 clk2

output clk_out

);

reg [2:0] sel_clk1_r ;

reg [1:0] sel_clk1_neg_r ;

reg [2:0] sel_clk2_r ;

reg [1:0] sel_clk2_neg_r ;

//使用3拍缓存,同步另一个时钟控制信号与本时钟控制信号的"与"逻辑操作

always @(posedge clk1 or negedge rstn) begin

if (!rstn) begin

sel_clk1_r <= 3'b111 ; //注意默认值

end

else begin

//sel clk1, and not sel clk2

sel_clk1_r <= {sel_clk1_r[1:0], sel_clk1 & (!sel_clk2_neg_r[1])} ;

end

end

//在下降沿,使用2拍缓存时钟选择信号

always @(negedge clk1 or negedge rstn) begin

if (!rstn) begin

sel_clk1_neg_r <= 2'b11 ; //注意默认值

end

else begin

sel_clk1_neg_r <= {sel_clk1_neg_r[0], sel_clk1_r[2]} ;

end

end

//使用3拍缓存,同步另一个时钟控制信号与本时钟控制信号的"与"逻辑操作

always @(posedge clk2 or negedge rstn) begin

if (!rstn) begin

sel_clk2_r <= 3'b0 ; //注意默认值

end

else begin

//sel clk2, and not sel clk1

sel_clk2_r <= {sel_clk2_r[1:0], !sel_clk1 & (!sel_clk1_neg_r[1])} ;

end

end

//在下降沿,使用2拍缓存时钟选择信号

always @(negedge clk2 or negedge rstn) begin

if (!rstn) begin

sel_clk2_neg_r <= 2'b0 ; //注意默认值

end

else begin

sel_clk2_neg_r <= {sel_clk2_neg_r[0], sel_clk2_r[2]} ;

end

end

//时钟逻辑运算时,一般使用特定的工艺单元库。

//这里用 Verilog 自带的逻辑门单元代替

wire clk1_gate, clk2_gate ;

and (clk1_gate, clk1, sel_clk1_neg_r[1]) ;

and (clk2_gate, clk2, sel_clk2_neg_r[1]) ;

or (clk_out, clk1_gate, clk2_gate) ;

endmodule

testbench 描述如下,主要产生异步的时钟选择信号。

`timescale 1ns/1ps

module test ;

reg clk_100mhz, clk_200mhz ;

reg rstn ;

reg sel ;

wire clk_out ;

always #(2.5) clk_200mhz = ~clk_200mhz ;

always @(posedge clk_200mhz)

clk_100mhz = #1 ~clk_100mhz ;

initial begin

clk_100mhz = 0 ;

clk_200mhz = 0 ;

rstn = 0 ;

sel = 1 ;

#11 rstn = 1 ;

#36.2 sel = ~sel ;

#119.7 sel = ~sel ;

end

clk_switch u_clk_switch(

.rstn (rstn),

.clk1 (clk_100mhz),

.clk2 (clk_200mhz),

.sel_clk1 (sel),

.clk_out (clk_out));

initial begin

forever begin

#100;

if ($time >= 10000) $finish ;

end

end

endmodule

仿真结果如下,可见时钟相互切换时没有产生毛刺,但是存在延迟。

-

电路设计

+关注

关注

6673文章

2451浏览量

204125 -

仿真

+关注

关注

50文章

4070浏览量

133550 -

信号

+关注

关注

11文章

2789浏览量

76727 -

时钟

+关注

关注

10文章

1733浏览量

131445 -

切换电路

+关注

关注

0文章

29浏览量

9408

发布评论请先 登录

相关推荐

时钟切换电路设计方案

时钟切换电路设计方案

评论