引言

反应离子蚀刻 (RIE)是一种干法蚀刻工艺,与半导体工业中使用的互补金属氧化物半导体(CMOS)方法兼容。在不希望湿法蚀刻造成金属污染或湿法蚀刻无法提供所需方向性的情况下,RIE通常用于从基板上去除硅。RIE使用与硅反应形成挥发性物质的活性气体,挥发性物质被抽走,从而去除硅。该反应是准各向同性的,因为硅的去除通常在所有方向几乎均等地发生。由于在创建纳米孔或沟槽等高纵横比结构时不希望出现各向同性,因此需要额外的步骤来使蚀刻工艺各向异性。

实验

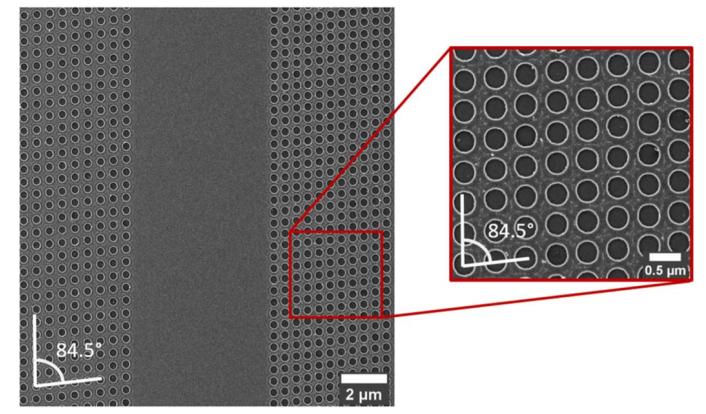

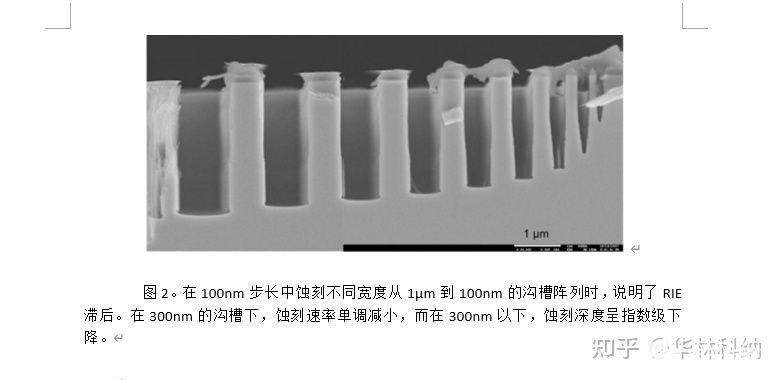

为了测试不同的蚀刻参数,蚀刻和分析了所谓的“easycleave”结构。如图1所示,Easycleave 是一块1 cm x 2 cm 的硅晶片,带有50 nm 厚的带有孔阵列的铬蚀刻掩模。孔径在原始晶格的轴之间以84.5°的角度排列。这种非 90° 角确保沿着晶圆晶面的切割总是会穿过一些孔隙,因此得名 easycleave。蚀刻掩模由11种不同直径的圆形孔阵列组成。对于每个直径,最多有7个不同孔间距的阵列。因此,easycleave掩模提供了广泛的结构参数来严格测试蚀刻程序和参数。(江苏英思特半导体科技有限公司)

图1。一个易切割样品的扫描电镜图像

由于蚀刻仪器专为使用4英寸晶圆而设计,因此有必要使用载体晶圆来固定易切割样品。载体晶圆(110,p掺杂硅,4 英寸,500 nm厚)涂有一层正光刻胶,该光刻胶以4000 rpm 的速度旋涂,并在 120 °C 下硬烘烤10分钟。光致抗蚀剂可防止载体晶圆被蚀刻,从而避免因高硅负载而产生的不必要的蚀刻现象,并确保晶圆的可重复使用性。

结果和讨论

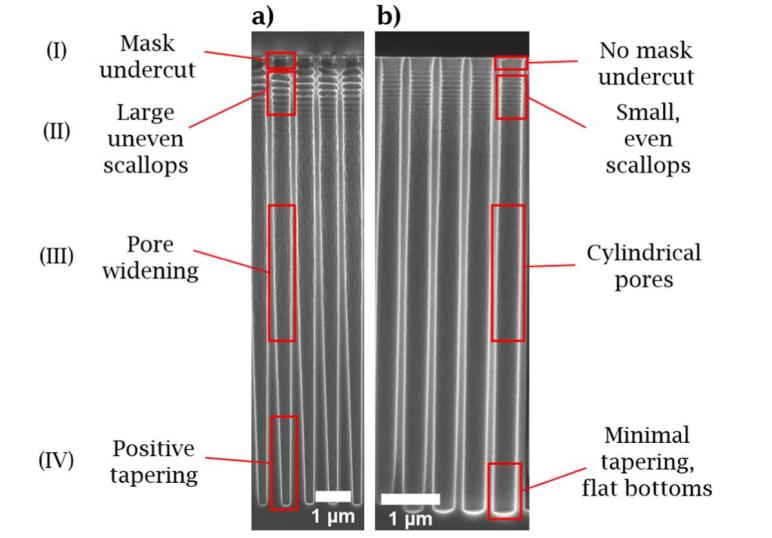

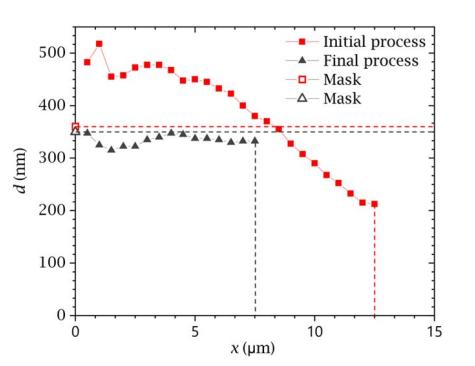

如图2(a)和3所示,孔变宽发生在纳米孔长度的中间部分,并且可能发生在没有掩模底切或锥形的纳米孔中。在较宽的纳米孔中,例如 500 nm 直径,这种现象主要表现为孔中间部分的粗糙外观,如图2(a) 中突出显示的那样。在较小直径的纳米孔中,这种粗糙度使孔的中间部分变宽,直径大于掩模的直径。这种粗糙度和加宽仅影响纳米孔的中间部分。(江苏英思特半导体科技有限公司)

在整个研究中观察到的所有情况下,扇贝都可以在孔的底部看到,并且通常直径已经恢复到面具的直径甚至更小。为了阐明在蚀刻过程中何时开始形成这种粗糙度,循环数从N= 200 逐渐减少,其中粗糙度在10到12个扇贝后开始,减少到N= 50。即使通过N= 50个循环,在10到12个扇贝之后,粗糙度遮盖了扇贝。这表明粗糙度不仅是由创建高纵横比结构所需的较长蚀刻时间引起的伪影,而且在蚀刻过程中相对较早地出现。

图2。(a)对d = 360 nm掩模直径的扫描电镜图像,(b)用d = 360 nm掩模直径测量的孔隙图像。

图3 纳米孔的直径d与纳米孔内的深度x的μm相比

结论

在这项工作中,研究并优化了蚀刻工艺以在硅中蚀刻圆柱形纳米孔,直径在280和500 nm之间,深度约为7 μ m,这些样品非常适合用于实现硅纳米光子学的纳米结构。

与完美圆柱体的剩余偏差在公差范围内以创建具有高反射率和明确定义的光子带隙的光子晶体。稍短的长度对于我们的应用来说仍然足够,并且可以通过增加循环次数来进一步改进,尽管这样做需要进一步优化。目前的优化是通过操纵多个蚀刻参数并将2步工艺转移到3步DREM Bosch工艺来实现的。在未来的工作中,可以通过使用对硅具有化学惰性的气体(例如氩气)来进一步改进三步法,以确保去除碳氟化合物,但不会对硅进行化学蚀刻,从而真正分离去除和蚀刻步骤。以指数方式而不是线性方式调整参数的能力也会提供更多的自由度。我们预见到转向4步DREAM(存款、移除)添加氧等离子体步骤以通过形成氧化硅层进一步保护壁,还可以提供更多途径来进一步改善和扩展纳米结构的 RIE。(江苏英思特半导体科技有限公司)

江苏英思特半导体科技有限公司主要从事湿法制程设备,晶圆清洁设备,RCA清洗机,KOH腐殖清洗机等设备的设计、生产和维护。

审核编辑黄宇

-

半导体

+关注

关注

334文章

27286浏览量

218049 -

蚀刻

+关注

关注

9文章

413浏览量

15368

发布评论请先 登录

相关推荐

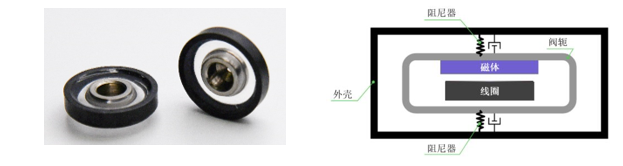

高频高精度圆柱形音圈电机

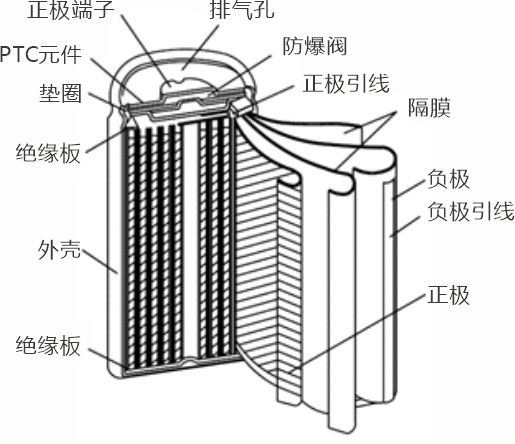

我国研制出超大容量圆柱形400Ah锂电池

《仿真分析小技巧9》---圆柱形器件的精确计算

反应离子蚀刻的实用方法报告

Mighty Mouse微型圆柱形连接器和电缆

4680圆柱形锂电池的优缺点

同茂圆柱形音圈电机中动磁式和动圈式怎么区分

光子晶体用硅中圆柱形纳米孔的深反应离子蚀刻

光子晶体用硅中圆柱形纳米孔的深反应离子蚀刻

评论