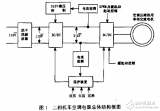

鉴相器作为环路的关键模块,主要鉴别参考频率和反馈信号的相位关系,对于环路精度和频率捕捉范围起到决定性作用。

01鉴相器基本原理

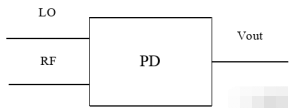

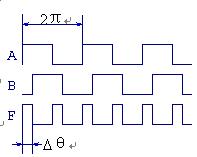

基本原理:把输入信号和锁相环的输出信号的相位进行比较,产生对应于两信号相位差ΔФ中的误差电压Vout,使锁相环系统能够稳定输出。

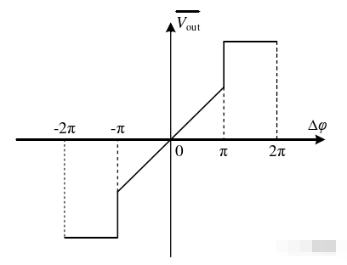

某种非线性鉴相特性曲线图

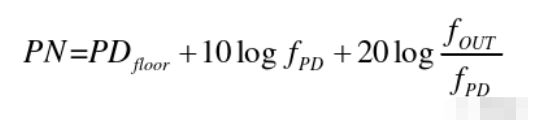

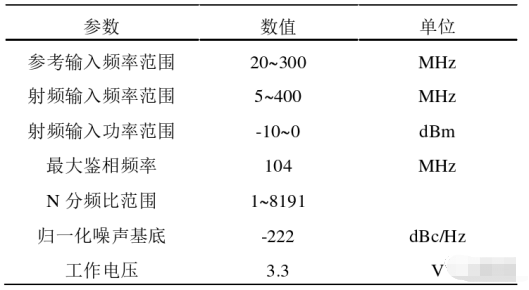

从频率源设计考虑:在鉴相器芯片选型时,不仅需要关注鉴相器噪声基底,鉴相频率还要关注鉴相器N分频器射频输入频率范围等。输出端信号带内相位噪声PN计算公式如下:

PDfloor为鉴相器的相位噪声基底,fPD为鉴相频率,fOUT为压控振荡器输出的频率。N为输出频率和鉴相频率的比值,当输出信号频率一定时,将鉴相频率增大为原来的10倍时,可编程分频器的分频比N将减小为原本的1/10。则基本单环锁相环输出信号总的相位噪声由于鉴相频率增大10倍会增加10dB,同时由于环路分频比N减小10倍而降低20dB。因此整体会使锁相环输出信号总的相位噪声改善10dB。由此可知,提高鉴相频率会改善系统的总相噪,同时还可以通过环路减小分频比N、使用归一化相位噪声更小的鉴相器等方法来减小环路系统输出总的相位噪声。

因此需根据相位噪声的指标要求,合理设计鉴相频率和分频比,并选满足指标的鉴相器。

设计鉴相器主要指标:鉴相灵敏度、鉴相范围-角度、死区、工作频率、噪声。

鉴相器也经常和电荷泵一起集成设计。

02稍微拓展

鉴相器又分:vwin 鉴相器和数字鉴相器两种

数字鉴相器

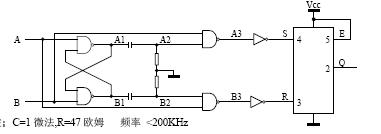

数字类鉴相器全部采用数字电路,工作速度快,但是工作频率较低并且存在鉴相死区的问题。该类鉴相器,其输入信号与输出信号不仅能频率相等,而且保持相位相同,使输出信号和输入信号保持完全同步,有的能同时鉴频鉴相。

数字鉴相器检测输入信号与反馈信号之间的频差或者相差,产生直流电压来控制电荷泵充放电,控制压控振荡器的输出频率。如果反馈的频率与输入频率不相等时,则鉴频鉴相器首先进行鉴频,通过比较反馈信号与输入的频差产生电压,作用在电荷泵,使环路滤波器的输出电压改变。通过电压的作用使输出频率向输入频率逐渐靠近,直到输出与输入频率相等时,鉴频鉴相器才会开始鉴相工作,比较输入频率与输出频率的相差,产生控制电压使两者的相位差恒定。

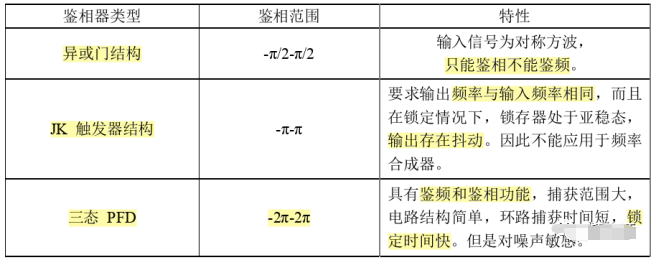

从数字鉴相器的结构分类:普通型边沿触发式PFD、预充电式PFD、TSPC和全差分边沿触发式PFD;从鉴相器的鉴相范围不同,可以分为以下三类:

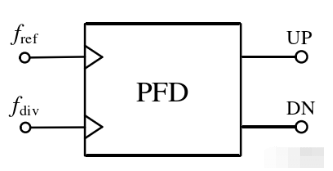

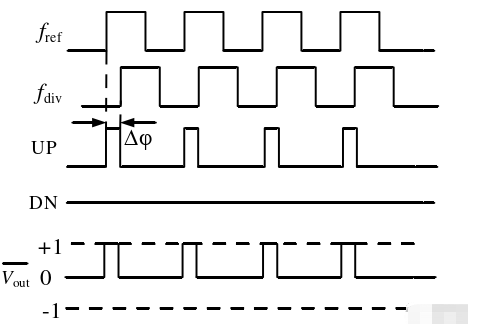

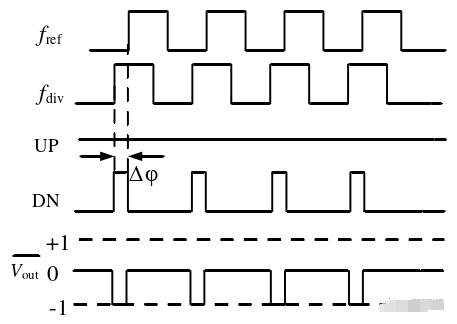

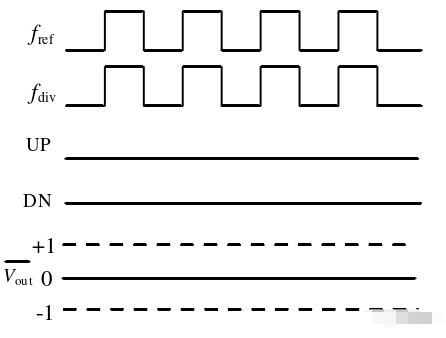

三态PFD三种不同的状态:在初始状态时、复位状态UP和DN均为0,表明此时fref和fdiv信号均没有上升沿到达,即fref和fdiv信号同时为高电平或同时为低电平;当PFD先检测到fref信号的上升沿时,参考fref信号相位超前,此时输出UP=1,DN=0;当PFD先检测到fdiv信号的上升沿时时,输出fdiv信号相位超前,此时输出UP=0,DN=1。

fref相位超前fdiv

fref相位滞后fdiv

fref与fdiv同频同相

模拟鉴相器

模拟类鉴相器工作频率较高,但是鉴相灵敏度低并且存在零点漂移的问题。

根据模拟鉴相器的电路结构不同,主要有以下几种类型:混频型鉴相器、一阶采样保持鉴相器和谐波采样鉴相器等。采样鉴相器的电路比混频型鉴相器要复杂,但是可以提供优于前两种的参考激励边带抑制和更低的噪声。

根据模拟鉴相器的混频器件不同分为:无源鉴相器,微带线功分鉴相器和平衡鉴相器;有源鉴相器,模拟乘法器为主,有源器件的增益较高和线性度较好等优点在信号处理电路中得到较高的应用。

根据模拟鉴相器中器件的线性度,大体上分为线性鉴相器和非线性鉴相器两种。线性,这种鉴相器的优点是鉴相增益高、端口隔离度好;缺点是鉴相范围较小,频率范围较低,用于处理较低频率的输入信号。非线性,此电路一般采用高频或微波二极管MESFET(金属-半导体场效应晶体管)及HEMT器件(高电子迁移率器件)来设计,其结构简单,处理频率较高,带宽较宽,但其增益和集成度较低,一般用于处理较高频率的输入信号。

模拟鉴相器根据鉴相波形和特性的不同,有正弦形特性、锯齿形特性和三角波特性等。常用的正弦鉴相器可用模拟相乘器与低通滤波器的相连作为简单模型。

-

锁相环

+关注

关注

35文章

584浏览量

87735 -

分频器

+关注

关注

43文章

447浏览量

49874 -

鉴相器

+关注

关注

1文章

60浏览量

23275 -

输入信号

+关注

关注

0文章

455浏览量

12547 -

反馈信号

+关注

关注

0文章

31浏览量

8218

发布评论请先 登录

相关推荐

鉴相器的基本原理和分类

鉴相器的基本原理和分类

评论