1 简述

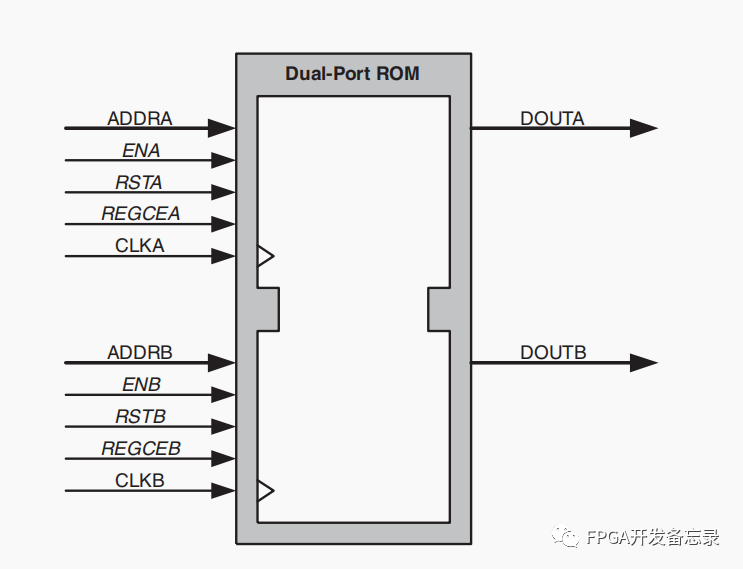

RAM :随机存取存储器(random access memory,RAM)又称作“随机存储器”。在FPGA开发过程中经常使用到,而所谓的双端口RAM就是有两组独立的端口对存储块进行读写操作,如下图所示。

一般在应用时,一个作为读端口,另一个作为写端口(也可以同时写和读)。

2 例化IP核

在开发过程中,常会用到双端口RAM,下面说一下FPGA中双端口RAM的常规使用方法,更多的使用方案可翻阅参考文献。

本次仿真采用Xilinx的 Block Memory Generator v8.4的IP核来进行例化,例化参数如下。

porta端口配置

portb端口配置

若以端口a作为写端口,b作为读端口,则写端口的数据位宽为128bit,深度为8192,则地址位宽为14bit,而读端口的数据位宽为32bit,深度为3276,则地址宽度为15bit。

3 端口描述

在写仿真激励之前,需要了解各端口在IP核中的功能,例化后的IP核如下图所示

各端口定义如下,端口b定义和a一样。

4 仿真激励编写

根据端口定义设计仿真激励,tb代码如下。

`timescale 1ns / 1ps

module tb_memory();

reg [12:0] addra;

reg clka ;

reg [127:0] dina ;

reg wea ;

reg ena ;

reg [14:0] addrb;

reg clkb ;

wire [31:0] doutb;

reg enb ;

reg web ;

initial begin

addra = 13'd0;

clka = 1'b0 ;

dina = 128'h40000000300000002000000010000000;

wea = 1'b1;

ena = 1'b1;

addrb = 15'd0;

clkb = 1'b0 ;

enb = 1'b1;

web = 1'b0;

end

always #10 clka = ~clka;//写时钟为50M

always #20 clkb = ~clkb;//读时钟为25M

reg [15:0] counta = 16'd0;

always @(posedge clka) begin;

if(wea==1'b1) begin

addra <= addra + 13'b1;

dina <= dina + 128'b1;

if (addra == 13'h3fff) begin

addra <= 13'h0;

end

end

end

reg [15:0] countb = 16'd0;

always @(posedge clkb) begin

if(enb==1'b1) begin

addrb <= addrb + 15'b1;

if (addrb == 15'h3fff) begin

addrb <= 15'h0;

end

end

end

design_1_wrapper tb_memory(

.BRAM_PORTA_0_addr(addra),

.BRAM_PORTA_0_clk (clka ),

.BRAM_PORTA_0_din (dina ),

.BRAM_PORTA_0_we (wea ),

.BRAM_PORTA_0_en (ena),

.BRAM_PORTB_0_addr(addrb),

.BRAM_PORTB_0_clk (clkb ),

.BRAM_PORTB_0_dout(doutb),

.BRAM_PORTB_0_we (web),

.BRAM_PORTB_0_en (enb)

);

endmodule

仿真结果如下图所示

由上图所示,由于写数据的位宽为128bit,读数据的位宽为32bit,因此需要读4次拼接起来才能恢复写入的数据。

-

存储器

+关注

关注

38文章

7484浏览量

163759 -

RAM

+关注

关注

8文章

1368浏览量

114639 -

FPGA开发

+关注

关注

1文章

43浏览量

14909 -

随机存取存储器

+关注

关注

0文章

44浏览量

8960

发布评论请先 登录

相关推荐

基于FPGA的双口RAM实现及应用

【FPGA开源教程连载】第十三章A 嵌入式RAM使用之双端口RAM

基于FPGA的双口RAM实现及应用

双端口RAM原理介绍及其应用

FPGA双端口RAM的使用简述

FPGA双端口RAM的使用简述

评论