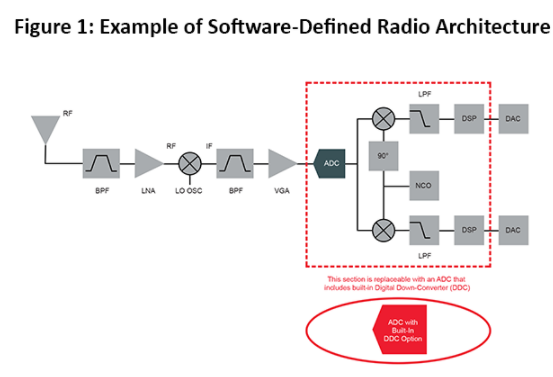

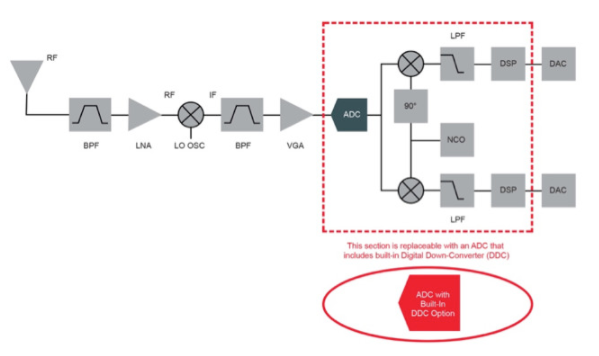

当今的数字无线电架构严重依赖先进的数字信号处理技术,例如用于同相和正交(I/Q)信号检测的数字下变频(DDC)和用于改善信噪比(SNR)的数字抽取滤波。DDC和许多其他数字处理功能通常由数字构建模块实现,这些构建模块需要使用现场可编程门阵列(FPGA)进行广泛的固件操作。图1显示了采用超外差双级转换架构的软件定义无线电接收器示例,这在射频(RF)通信系统和高速数据采集系统中非常常见。

对于大多数系统开发人员来说,数字信号处理(DSP)构建模块的固件开发是一项非常耗时的任务。FPGA也往往是许多系统中成本最高的组件。为了降低整体系统硬件要求、复杂性、开发时间和成本,内置数字信号后处理(DSPP)选项的数字增强型模数转换器(ADC)是满足当今严格设计要求的绝佳解决方案。

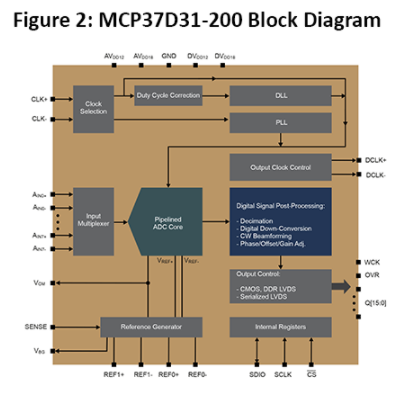

如图1所示,传统的ADC和DDC模块可以用数字增强型ADC代替,后者可以输出I/Q信号或上变频实数信号。MCP37Dx1-200/80 是数字增强型 16/14/12 位低功耗、8 通道多路复用器、200/80 Msps ADC,具有 SPI 串行接口,能够执行各种 DSPP 功能。使用数字增强型ADC,无需在低功耗无线应用中使用大量基于FPGA的逻辑。

Microchip的MCP37D1-200/80 ADC还具有内置抽取滤波器,用于改善各个通道的SNR、分数延迟恢复(FDR)、相位/失调和增益调整。此外,它们还具有内置的ADC线性度校准算法,如谐波失真校正(HDC)、DAC噪声消除(DNC)和动态元件匹配(DEM)。该系列流水线ADC提供12位、14位和16位版本,还提供业界功耗最低的器件。在200 Msps时的功耗在CMOS数字I/O时为436 mW,使用LVDS数字I/O时为490 mW,不使用数字I/O时为390 mW。

Microchip的高速流水线ADC系列非常适合各种应用,包括低功耗便携式仪器、蜂窝基站、超声和声纳成像等。

审核编辑:郭婷

-

FPGA

+关注

关注

1629文章

21729浏览量

602984 -

无线电

+关注

关注

59文章

2139浏览量

116431 -

DDC

+关注

关注

2文章

90浏览量

37088

发布评论请先 登录

相关推荐

增强型无线话筒电路图

Bondout、增强型Hooks芯片和标准产品芯片

【精选问答】TI 低功耗无线 MCU 对物联网的推动及应用

中等容量增强型,32位基于ARM核心的带64或128K字节闪存的微控制器 USB、CAN、7个定时器、2个ADC 、9个通信接口

接入HSDPA解决WCDMA问题 增强型无线技术浅析

基于增强型并行口的智能仪表与微机的高速通讯

高速低功耗数字光电耦合器(Avago)

增强型MOS晶体管,增强型MOS晶体管是什么意思

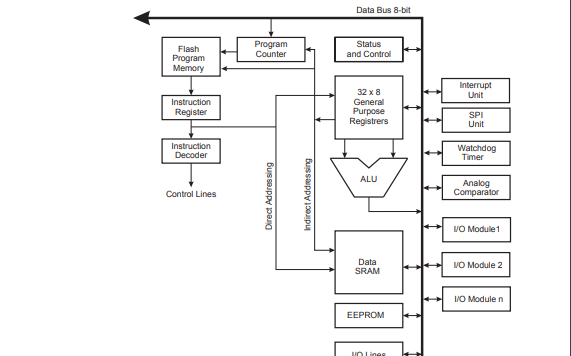

ATtiny2313 AVR增强型RISC架构的低功耗CMOS 8位微控制器的资料概述

数字增强型高速ADC用于低功耗无线应用

一款12位高速、低功耗的逐次逼近型ADC

EMC性能优异的ISO7710高速单通道增强型数字隔离器数据表

面向低功耗无线应用的数字增强型高速ADC

面向低功耗无线应用的数字增强型高速ADC

评论