晶圆键合技术正得到越来越多的关注。

先进封装大概可以分为两大类趋势:一个是小芯片(chiplet)。

小芯片将传统上较大型的集成电路分拆成许多较小的功能模组,先个别予以优化,再使用这些已优化的小芯片组织新的次系统。这样可以重复使用IP,大幅加速产品设计的速度以及降低设计成本。

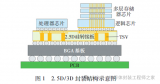

至于各个小芯片之间的连接,依靠底下中介层(interposer)内的金属连线。此连线的密度当然远高于传统的线路板或封装I/O所能支援的密度,大幅增加线路运作频宽(bandwidth)、增大平行运算的操作空间。

另一个方向自然是异构集成(heterogeneous integration)。

将不同制程或不同材料的芯片堆叠在一起,以整合方式提升、扩充组装元件的功能。除了已经商业化的方法外,基本上有芯片-晶圆(Chip-on-Wafer;CoW)及晶圆-晶圆(Wafer-on-Wafer;WoW)等两种键合形态。二者在键合后都需要再切割晶粒,但是也有例外。CoW程序较复杂,所以WoW可能早些普及。

晶圆间键合的技术又有很多种,现在已经进入商业化的技术之一是“铜-铜混合键合”(Cu-Cu hybrid bonding),这也是本文讨论的主题。

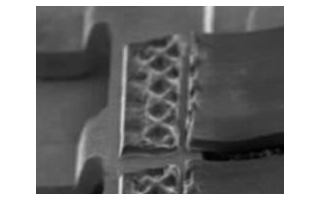

铜-铜混合键合技术是将两片欲键合在一起的晶圆,各自完成制程最后一步的金属连线层,此层上只有两种材质:铜及介电质。介电质可以是氧化硅或高分子材料,二者各有优缺点,使用何种物质依制程需要而定。由于晶圆键合时牵涉到铜及介电质两种材料介面,所以称之为混合键合。

两片晶圆面对面键合时是铜金属对铜金属、介电值对介电质,两边键合介面的形状、位置完全相同,晶粒大小形状也必须一样。所以使用混合键合先进封装技术的次系统产品各成分元件必须从产品设计、线路设计时就开始共同协作。

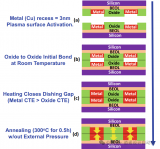

混合键合制造约略如下:两边晶圆在完成最上层的金属制造后,经化学机械研磨(Chemical-Mechanical Polishing;CMP)及清洗后,两片晶圆面对面对齐(alignment)。介电质先经离子活化(ion activation),两边介电质接触后产生共价键。两边铜的表面原先较介电质稍低,在退火(annealing)时因膨胀系数较介电质为大而增高接合,两边铜离子因相互扩散(diffusion)进入对方而形成密切的永久性接合。

晶圆平坦化(planarization)不足、残留粒子、对齐误差及金属介面孔隙(void)等均有可能影响元件特性或失效。

目前混合键合机台已有多家设备厂商投入量产。如EVG、SUSS MicroTech、TEL、AML等,典型机台如EVG的Gimini系列。由于现代设备厂商在销售机台时多附有机台相关之基础制程,混合键合制程的开发通常不算是严峻的挑战。

目前铜混合键合的封装制程良率已经可以到达一般后段封装的典型良率99%以上。一部分原因是于此技术的累积发展与已经商业化的机台设备同步,但是更重要的原因是两边芯片的设计团队期前的设计沟通,在重复单元区留下适度的冗余(redundancy),当键合时发生缺陷时,有足够的空间来使用。

混合键合的最大特色是芯片对外连接金属垫(metal pad)的尺度是“半导体制程级”的。相较于之前用于中介板的微凸块(microbump)间距40um,混合键合的键合间距可以小达1~2um,限制尺寸的原因主要来自于对齐的精确程度,还有进一步改善的空间。

这样的键合间距代表每平方公分芯片面积可以承担百万个连接,这比任何既存的封装方式都有几个数量级的提升。

连线键合数目愈多意味着两个芯片之间容许更高频宽的沟通,有利于平行运算,也容许较高电流。功能模组之间的连线也较寻常方式更短,所以速度快、噪音低、功耗也较小。另外混合键合本来就是异构集成、3D堆叠先进封装中的一种方法,所以二者的优点也自然都有。

商业应用混合键合的半导体产品,首先是Sony的CIS。CIS有几个组成部分:画素阵列(pixel array)、类比数位转换器(Analog-to-Digital Converter;ADC)、影像讯号处理器(Image Signal Processor;ISP)。画素阵列基本上是1层多晶硅(polysilicon)与5层金属的制造;ADC与ISP则是1层多晶硅与10层金属的制程,二者的制程差距甚远,符合“异质”特征,应该分别制造。二者的3D芯片堆叠还能缩小镜头尺寸,所以Sony早在2016年就将分别制造的画素阵列晶圆与ADC+ISP晶圆混合键合,替代原来在同一芯片的设计制造。

由于混合键合大幅增加金属连线密度,使得ADC可以平行处理画素,大幅提升画面处理的能力,譬如全域快门(global shutter)、影片的每秒帧数(frame per second)等。目前的设计趋势是向每个画素都有独立的ADC方向迈进。

进一步的工作是将DRAM也加入CIS的3D堆叠,做为画素处理的缓冲存储器(buffer memory)。Sony和三星电子(Samsung Electronics)都有此设计,只是DRAM堆叠位置不一。影像在车辆的应用,譬如用来侦测前方物体距离的时差测距(Time of Flight;ToF)的单光子雪崩探测器(Single Photon Avalanche Detector;SPAD);或在工业的应用,譬如机器视觉(machine vision),都可能需要再加入能执行边缘计算(edge computing)芯片。CIS启动混合键合的商业应用,历史较长,较长远的应用规划也渐入视野。

另外一个也进入商业量产的应用是3D NAND。平面NAND的存储器细胞阵列(memory cell array)与其他逻辑线路-包括微控制器(microcontroller)、位址寄存器(address register)等,是放在同一芯片上的。

3D NAND 的存储器细胞阵列持续往3D方向堆叠,但是逻辑线路上方却空无一物,严重浪费珍贵的芯片内部空间(real estate)。

所以长江储存首先以XtackingTM技术将逻辑线路部分以混合金键合方式置于存储器细胞阵列之下,大幅提高芯片内部面积使用效率。其他公司后来也采取类似方法。不过在此例中,金属垫的密度不需要特别地高。

混合键合技术的新应用中,最引人注目的当属高效能计算(High Performance Computing;HPC)。HPC在晶圆代工的产能中占据最显著的分量。

HPC架构主体主要含处理器和存储器。处理器通常以最先进的逻辑制程制造,但是存储器(DRAM)的制程进展较逻辑制程缓慢,这个就产生落差。

两者之间沟通落差限制整体表现,而且制程也截然不同,属于“异质”。

解决两者之间效能落差的方法之一是利用平行处理。现在的处理器通常具有多个数量的内核(cores),每个内核需要支援其运作的个别存储器。数量如此多的内核-存储器之间的连线需要多个I/O节点以及高频宽,这就是十年前开始出现高频宽存储器(High Bandwidth Memory;HBM)需求的驱动原因。

HBM是用2.5D封装技术将CPU与超过8个DRAM堆叠封装,其处理器与存储器之间的连接是透过芯片的微键(microbond)连接底下中介层的金属线至另外的芯片,如此一来I/O与连线的密度都可以大幅增加。

对于常用于AI常用的GPU芯片,其内核的功能比较专一,所以每个内核的面积较小,一个芯片里内核的数目动辄上千。每个内核所需要对应存储器容量不需要很大,但是因为内核与存储器的数目有数量级的提升,连线及I/O的数目要求更高,此时铜混合键合就能提供其所需要的效能。

这个应用也是目前多家代工厂、DRAM厂的技术及业务能力扩展方向。

2022年3月Graphcore发布于台积电造的Bow IPU号称是世界第一个3D WoW处理器,利用到的是混合键合的另一种优势。两片晶圆一边是AI处理器及其协作的存储器,主要包括1,47两个IPU(Intelligent Processor Unit,Graphcore为其处理器的命名)以及与各IPU协作的独立900MB的分散式SRAM;另一个芯片负责提供电源。如此结构设计,Graphcore宣称可以提升效能40%以及节省功耗16%。

AMD最近的Ryzen系列也因为不同的原因采取混合键合技术,虽然使用的是CoW的技术,而非WoW。AMD将CPU中面积较大的L3 cache单独拿出并扩增容量、单独生产,在不增加CPU系统面积的情况下,增加可用的SRAM容量,减少一般数据处理必须传送到DRAM的需求,因而提升速度、减少功耗。

其他混合键合的应用现在可预见的还包括无线通信、AIoT、PMIC等。在混合键合的制造成本下降后,应用领域还有可能延拓得更广泛。从芯片异质整合、效能提升、减少功耗、缩小面积等的几个优点考量,只要混合键合的成本下降至各优点的价值临界点后,技术的采用将会一一浮现。学习已经商业化的、正在酝酿中的应用并且分析其得失,是寻找新应用的必要学习过程。

晶圆键合是近十几年快速发展起来的新兴半导体加工技术,在MEMS,CIS和存储芯片等领域有着重要的应用,得到越来越多的关注。

审核编辑 :李倩

-

处理器

+关注

关注

68文章

19259浏览量

229647 -

芯片

+关注

关注

455文章

50714浏览量

423113 -

晶圆

+关注

关注

52文章

4890浏览量

127930

原文标题:铜混合键合的发展与应用

文章出处:【微信号:ICViews,微信公众号:半导体产业纵横】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

三维堆叠封装新突破:混合键合技术揭秘!

铜混合键合的发展与应用

铜混合键合的发展与应用

评论