我们以一个简单的加法器为例,来看下如何用vcs+verdi仿真Verilog文件并查看波形。

源文件内容如下:

//adder.v moduleadder( inputclk, inputrst, input[9:0]A, input[9:0]B, outputreg[10:0]C ); always@(posedgeclk)begin if(rst) C<= #`FFD 'b0; else C <= #`FFD A + B; end endmodule

我们再定义一个宏定义的文件:

//macro_define.sv `defineFFD1ns

我们需要再定义一个testbench文件:

//test.sv moduletest; regclk; regrst; reg[9:0]A; reg[9:0]B; wire[10:0]C; initialbegin rst=1; A=0; B=0; #1us; rst=0; #1us; A=10'd100; B=10'd200; #1us; A=10'd300; B=10'd400; #20us; $finish; end initialbegin clk=0; forever#10nsclk<= ~clk; end adder add_inst( .clk(clk), .rst(rst), .A(A), .B(B), .C(C) ); `ifdef DUMP_FSDB initial begin $fsdbDumpfile("tb.fsdb"); $fsdbDumpvars("+all"); //string testname; //if($value$plusargs("TESTNAME=%s", testname)) begin // $fsdbDumpfile({testname, "_sim_dir/", testname, ".fsdb"}); //end else begin // $fsdbDumpfile("tb.fsdb"); //end end `endif endmodule

再定义一个filelist文件:dut.f

./macro_define.sv ./adder.v ./test.sv

最后就是需要一个Makefile文件了:

#!/bin/make all:compsimcomp: vcs-full64-timescale=1ns/1ps-V-R-sverilog -debug_access+all+vc+v2k-kdb -lvcs.log -fdut.f+define+DUMP_FSDB=1 -toptest sim: ./simv-lsimv.log clean: rm-rf*~corecsrcsimv*vc_hdrs.hucli.keyurg**.lognovas.**.fsdb*verdiLog64*DVEfiles*.vpd

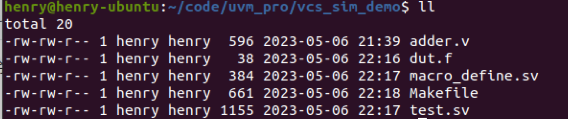

总的文件如下:

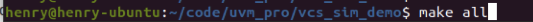

执行make all:

跑完后如下:

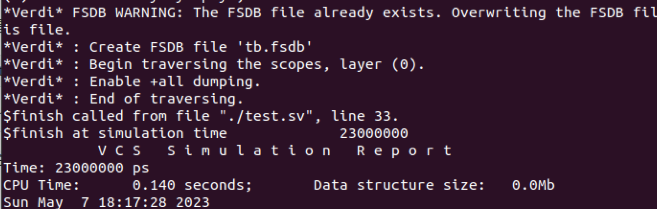

生成的文件如下:

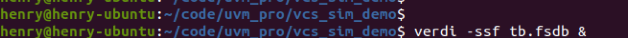

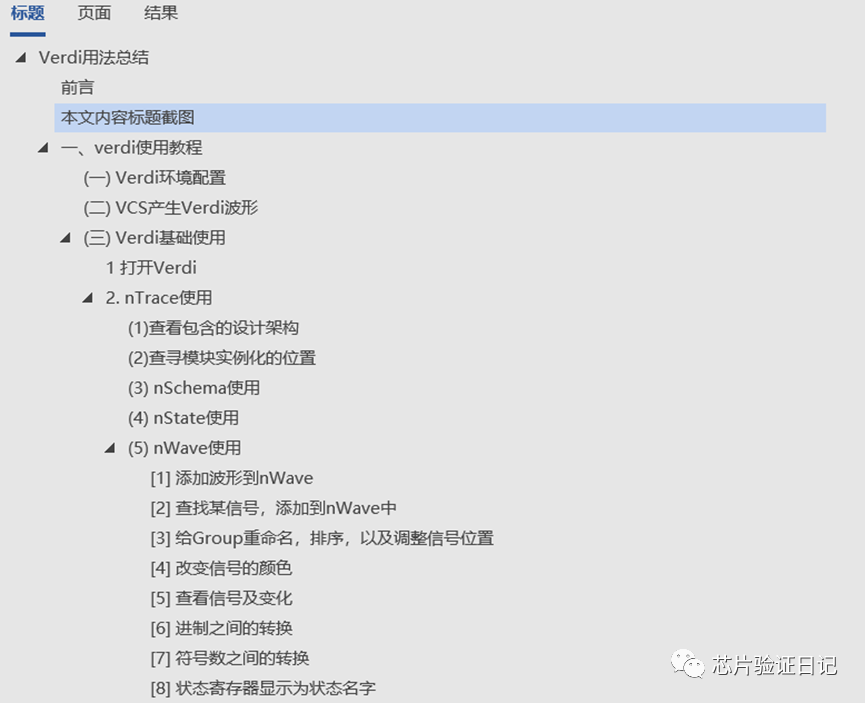

用verdi打开波形:verdi -ssf tb.fsdb

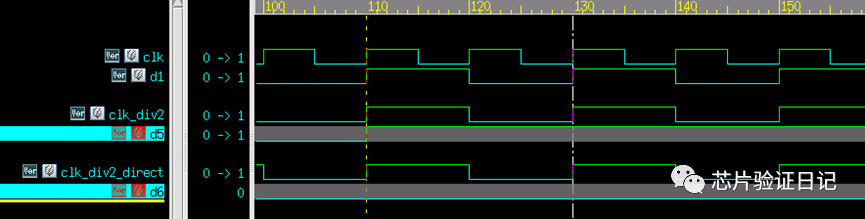

可以看到波形如下:

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网 网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- Verilog

+关注

关注

28文章

1330浏览量

109613 - 加法器

+关注

关注

6文章

181浏览量

29898 - VCS

+关注

关注

0文章

78浏览量

9530

原文标题:vcs+verdi仿真Verilog代码

文章出处:【微信号:傅里叶的猫,微信公众号:傅里叶的猫】欢迎添加关注!文章转载请注明出处。

发布评论请先登录

相关推荐

请教VCS和verdi怎么联合使用

最近要用到

VCS

仿真后生成FSDB

文件,然后在

Verdi中进行自动侦错,请问我怎么安装

Verdi这个软件以及如何启动license,并且怎么

发表于01-22 14:53

VCS仿真卡住,为什么无法生成verdi波形文件呢?

在make com编译成功后,terminal卡住了一直没有反应,这是什么情况有大佬知道吗?

VCS

仿真卡住,为什么无法生成

verdi

波形

文件

发表于06-21 08:14

基于linux系统的VCS使用及仿真说明

代码如下:顶层模块代码:波特率产生模块接收模块代码:发送数据模块一、

VCS

仿真下面开始进行

VCS

仿真。

VCS要使用图形化界面,必须得先编译得

发表于07-18 16:18

在Linux上用vcs+verdi对demo_nice进行仿真没有成功的原因?

请教大神,我在Linux上用

vcs+verdi对demo_nice进行

仿真,但是没有成功 我是用hibrd.sdk把demo_nice编译成.

verilog

文件的,其内容如下 另

发表于08-12 08:07

vcs和verdi的调试及联合仿真案例

若想用

Verdi观察

波形,需要在

仿真时生成fsdb

文件,而fsdb在

vcs或者modelsim中的生成是通过两个系统调用$fsdbDumpf

如何通过自动化脚本实现Questasim和Verdi的联合仿真

Verdi是用来

仿真以及debug

波形的工具,但它不能够用来编译

verilog和systemverilog

文件,所以需要借助第三方EDA工具

如何使用IcarusVerilog+GTKWave来进行verilog文件的编译和仿真

Windows+Linux+MacOS,并且源代码开源。通过tb

文件可以生成对应的

仿真

波形数据文件,通过GTKWave可以

查看

仿真

利用vcs+verdi仿真工具蜂鸟E200系列处理器仿真分析

开源RISC-V Hummingbird E203(蜂鸟E203)的

仿真工具是开源的iverilog,这里利用

vcs+verdi

仿真工具进行

仿真;

全网最实用的Verdi教程1

Verdi是一个功能强大的debug工具,可以配合不同的

仿真软件进行debug,很多企业常用

VCS+Verdi或者Xcelium/xrun+

Verdi的方式进行代码的

全网最实用的Verdi教程2

Verdi是一个功能强大的debug工具,可以配合不同的

仿真软件进行debug,很多企业常用

VCS+Verdi或者Xcelium/xrun+

Verdi的方式进行代码的

全网最实用的Verdi教程3

Verdi是一个功能强大的debug工具,可以配合不同的

仿真软件进行debug,很多企业常用

VCS+Verdi或者Xcelium/xrun+

Verdi的方式进行代码的

Verdi环境配置、生成波形的方法

Verdi是一个功能强大的debug工具,可以配合不同的

仿真软件进行debug,很多企业常用的就是

VCS+Verdi或或者Xcelium(xrun)+

Verdi的方式进行代码的

如何用vcs+verdi仿真Verilog文件并查看波形呢?

如何用vcs+verdi仿真Verilog文件并查看波形呢?

评论