编者注:我在很多场合讲过从仿真到测量这个话题,最近我也看到了一些调研数据。这个问题现在在国内来讲应该算是处于起步阶段,但是我相信未来会越来越好。

数据中心利用发射系统和接收系统之间的通道,可以准确有效地传递有价值的信息。如果通道性能不佳,就可能会导致信号完整性问题,并且影响所传数据的正确解读。因此,在开发通道设备和互连产品时,确保高度的信号完整性非常关键。测试、识别和解决导致设备信号完整性问题的根源,就成了工程师面临的巨大挑战。本文介绍了一些仿真和测量建议,旨在帮助您设计出具有优异信号完整性的设备。

中央处理器(CPU)可将信息发送到发光二极管显示器,它是一个典型的数字通信通道示例。该通道 — CPU 与显示器之间的所有介质 — 包括互连设备,例如显卡、线缆和板载视频处理器。每台设备以及它们在通道中的 连接都会干扰 CPU 的数据传输。

信号完整性问题可能包括串扰、时延、振铃和电磁干扰。尽早解决信号完整性问题,可以让工程师开发出可靠性更高的高性能的产品,也有助于降低成本。

通道仿真

工程师通常会用电子设计自动化软件来创建电路仿真。设计自动化软件则是采用逐位和统计仿真技术,用以提供快速而准确的通道仿真。算法建模接口是设计软件所使用的一种标准, 它可以轻松仿真从发射到接收的多千兆位串行链路。

除了仿真软件以外,工程师还使用眼图、混合模式 S 参数、时域反射测量之类的信号分析工具。在仿真从发射机到接收机的数据传输时,示波器上显示的眼图可以作为分析参数,帮助评估通道性能。

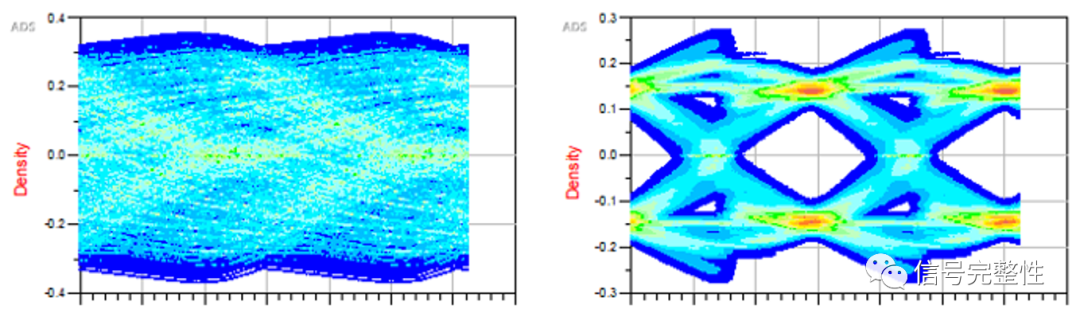

眼图的宽度和高度是信号失真的关键指标。宽大的眼图意味着数据传输良好。闭合的眼图表示信号完整性大幅降低。如果发射机处的眼图是开眼,接收机处是闭眼,下一步就需要确定通道中的哪些设备或互连导致了信号衰减。工程师可以直接查看发射机输出端的眼图,通过每个互连追溯到接收机,从中确定导致信号衰减的组件。

图 1:闭合的眼图和正常的眼图的示例

确定信号衰减的根本原因

描述给定设备的频率特性时,工程师可以使用 S 参数作为标准。互连的 S 参数(无论是在时域还是在频域中进行测量)代表了互连的特征模型。该参数涵盖了信号从进入一个端口到离开另一个端口时的所有特性信息。

为了确定信号衰减的根本原因,重要的是先要确定您对 S 参数的期望值。将期望值与测量值进行比较,有助于识别导致信号完整性衰减的通道区域。

接下来,您需要更深入地研究被测设备和设备之间的连接,以便确定根本原因。对于差分通道,可以使用混合模式 S 参数进行分析。最常见的 S 参数是与电磁干扰有关的差分回波损耗(SDD11)、差分插入损耗(SDD21)和差分至共模转换(SCD21)。

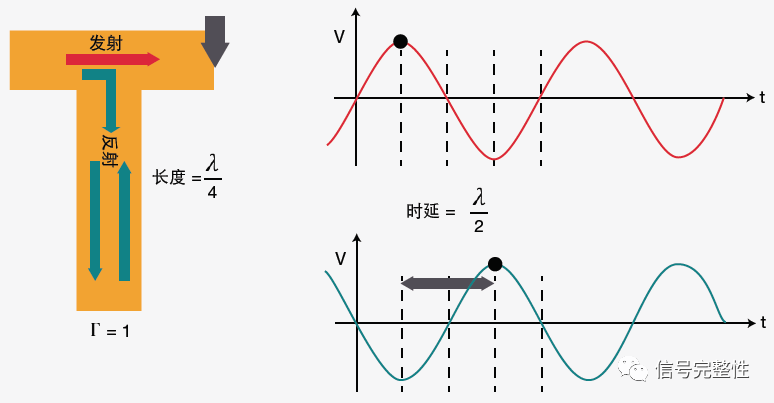

在分析传输质量时,还需要重点考虑反射因素。每当出现瞬时阻抗变化时,信号就会被反射。反射会使返回的原始信号出现延迟(如下图 2 所示),并与原始信号结合而产生干扰。

图 2:反射对信号质量的影响

探索和设计信号完整性解决方案

初步找到信号衰减的根本原因之后,您就需要研究并确定最佳的解决方案。首先,要执行去除设计缺陷后的仿真测试,以验证您确实找到了信号完整性衰减的根本原因。我们的建议是,与其将删除有问题的区域作为解决方案,不如试着在接收机上添加均衡,例如添加决策反馈均衡

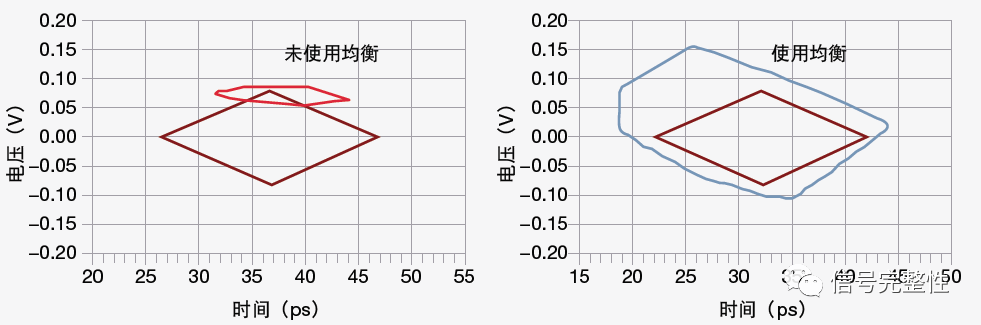

(DFE)、频域中的连续时间线性均衡或时域中的发射机前馈均衡。同样,您也可以通过仿真来 添加均衡,通过在示波器上实时观察眼图的变化,即可测试该均衡是否已经解决了信号完整性衰减的问题。

如图 3 所示,另一个测试选项就是将眼图模板应用于添加均衡之前和之后。在添加均衡之前,图像相交,表示眼图闭合。在添加均衡之后,图像不再相交,表示眼图打开。

图 3:使用 DFE 前后的眼图模板比较

信号完整性分析

当产品设计从仿真阶段进展到硬件环节时,您需要使用矢量网络分析仪(VNA)来测试高速数字 互连。首先,您需要对通道、物理层设备、连接器、电缆、背板或印刷电路板的预期测量结果有所了解。在获得实际测量结果之后,再将实际结果与这个预期结果进行比较。我们的目标是,通过软件和硬件来建立可靠的信号完整性工作流程。硬件测量步骤包括仪器测量设置,获取通道数据,以及分析通道性能。

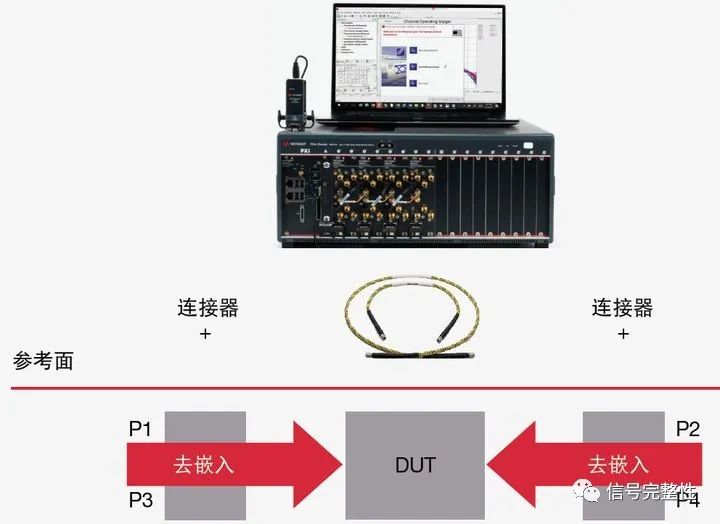

对于矢量网络分析仪(VNA)等高动态范围的仪器,您需要全面了解误差校正,才能确保最准确的 S 参数测量。误差校正包括校准(测量前误差校正)和去嵌入(测量后误差校正)。通过调整校准和去嵌入的参考点检查通道中除了 DUT 之外的所有节点项目。以下内容介绍了校准和去嵌入误差校正之间的差异以及二者的使用方法。

信号校准

默认情况下,当矢量网络分析仪(VNA)开启时,其参考平面位于前面板。将电缆连接到被测设备时,校准参考必须使用短路-开路-负载-直通法(SOLT)、直通反射线或直通反射匹配参考结构。SOLT 是最常见的方法。

电缆可以直接连接到 DUT 或夹具。夹具安装在电缆和 DUT 之间,有助于兼容不同类型的连接器,例如 HDMI、显示端口、串行 ATA 和 PCI Express。在本示例中,校准参考面包括电缆,而去嵌入参考面包括夹具。将校准误差校正和去嵌入相结合时,必须包括通道中与 DUT 的所有互连。连接 DUT 后,您就可以进行测量,并执行测量后(去嵌入)误差校正。

图 4:使用参考面进行校准的测试设置

去嵌入

完成测量,在 DUT 的输入和输出端设置去嵌入参考点,以便移除测试夹具。移除测试夹具之后,也就去除了引入到系统中的损耗和反射,最终得到 DUT 的准确 S 参数测量和表征结果。

通过将两层校正(校准和去嵌入)的 S 参数结果与预期结果进行比较,您可以进行模型调整以便匹配实际测量值,然后继续进行设备开发。

图 5:使用参考面进行去嵌入的测试设置

克服信号完整性问题

随着数据传输速度的提高,信号完整性对于通道设备和互连产品越来越重要。为了确保您的设备具有出色的信号完整性,首先您要确定好希望获得的仿真结果,然后再将其与实际测量结果进行比较。

接下来,结合信号分析技术(例如在示波器上显示的眼图)和仿真软件,即可找到导致信号衰减的根本原因。下一步就是确定合适的解决方案,使用软件和硬件来建立可靠的信号完整性工作流程。

必须使用高质量的矢量网络分析仪(VNA),设置校准参考面以执行 S 参数测量,设置去嵌入参考面以正确移除夹具。测量结果将会包括准确的 S 参数和可靠的 DUT 特性。尽早解决信号完整性问题,您就可以优化电路设计,保证优异的设备性能和出色的价格优势。

审核编辑:刘清

-

示波器

+关注

关注

113文章

6240浏览量

184792 -

接收机

+关注

关注

8文章

1180浏览量

53451 -

信号完整性

+关注

关注

68文章

1404浏览量

95456 -

中央处理器

+关注

关注

1文章

124浏览量

16516

原文标题:从仿真到测量的信号完整性

文章出处:【微信号:SI_PI_EMC,微信公众号:信号完整性】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何设计出具有优异信号完整性的设备?

如何设计出具有优异信号完整性的设备?

评论