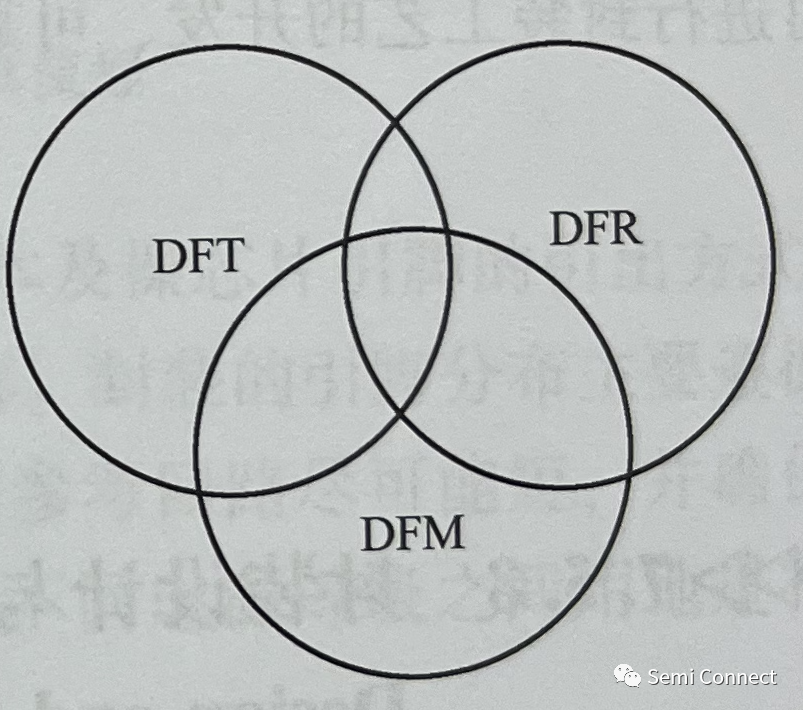

可制造性设计 (Design for Manufacturabiity, DFM)、可靠性设计 (Designfor Reliability, DFR)与可测试性设计 (Design for Testability, DFT)互相交叠密不可分,需要综合考虑,以实现设计与工艺的迭代优化。DFM/DFR/DFT 协同设计示意图如图所示。

(1) DFM:可制造性设计的目的是基于先进封装工艺能力,综合封装性能需求,实现设计与制造工艺的紧密结合。封装设计首先应考虑封装工艺的能力,要以大规模生产所需的工艺设计淮则来确定电气、散热性能及封装结构设计,并允许在特殊需求下调整和优化工艺。例如,为了提高散热性能,QFN 封装底部中央位置有一个大面积裸露焊盘用于导热,根据工艺和芯片情况可实现单芯片或多芯片的集成;为满足高频应用的需求,可通过优化 OFN封装工艺缩短引线长度,以此提供射频(甚至毫米波)信号的传输。

芯片堆蚕是一种典型3D封装形式,芯片堆香工艺对芯片尺寸、引线键合的引脚位置都有限制,为提高堆叠芯片的数量,需要进行芯片滅薄和低弧度键合工艺的优化。这类由应用需求引起的结构/材料优化和工艺优化需要考虑可靠性性能,因此需要 DFM 与DFR 之间的协同设计。

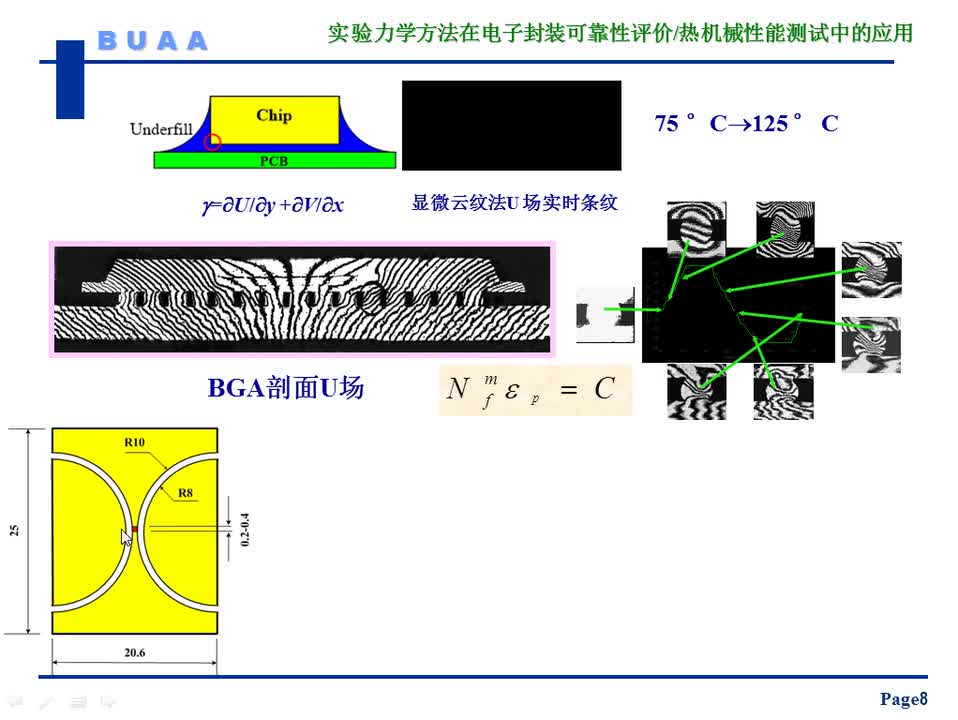

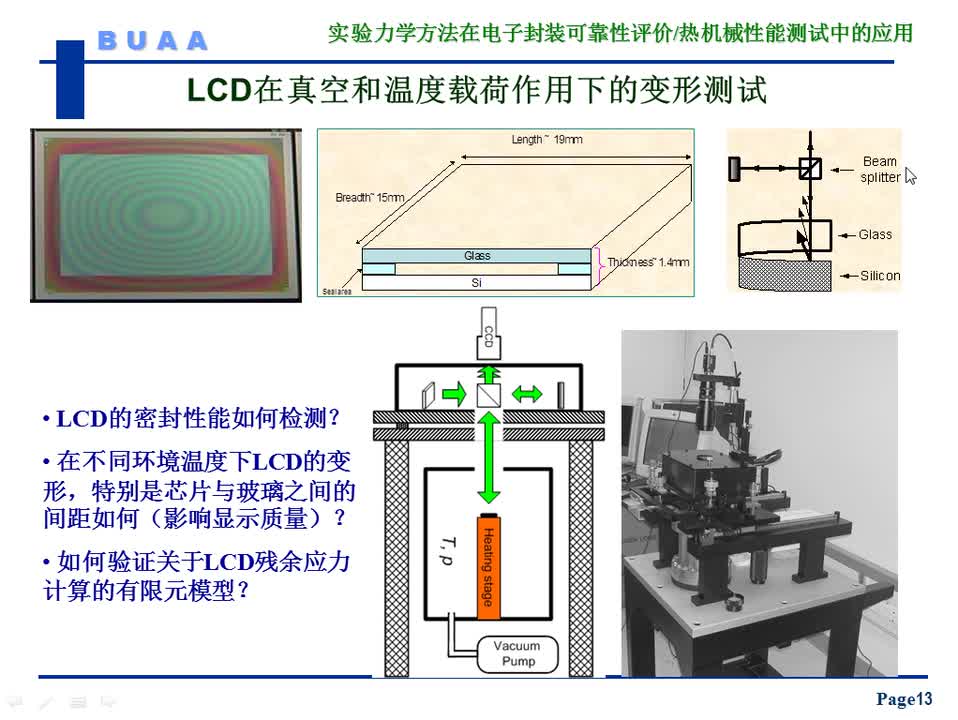

(2) DFR:可靠性设计的目的是为了采用 DOE试验设计方法实现结构和材料设计的迭代优化,消除可靠性隐患。在设计之初,通过对材料和结构体系的优化,采用份真vwin 、理论分析和实验验证相结合的方式,对封装的热应力/应变、热疲劳、电迁移等可靠性相关问题进行研究和优化。由于热应力源自不同封装材料之间的热失配,所以设计时应尽量采用对称的封装结构,选择热膨账系数匹配、玻璃化温度(Tg)合适的封装材料,也可以通过添加底部填料来提高封装和装配的可靠性。芯片-封装交互作用 ( Chip Package Interaction, CPI)也是DFR 的重要内容。

(3)DFT:通常意义上的可测性设计,是指在设计系统和电路的同时,通过增加一定的硬件开销,从而获得最大可测性的设计过程,其目的是用于检测生产故障。例如,数字电路常见的可测性设计方法有扫描测试(SCAN)、内建自测试(Built-In Self-Test, BIST)、边界扫描测试(Boundary Scan Test)等。这些DFT方法都可应用于常规的封装形式,如QFN 封装、BGA封装等。

对于2.5D 类复杂封装,在封装制备过程中也要进行可测性设计。为了检测TSV 中介转接层的成品率,除了直接用探针进行接触式测量,也可设计 TSV 测试电路并配合软件来进行测试。对于有特殊需求的封装,如高频/高速封装、大功率封装等,还需制定单项性能测试方案。例如,设计可测性高速测试线路样品,可对封装体内典型的互连结构的电学性能进行测量;设计可测性热阻测试样品,可事先对封装体内的结温和热阻进行测量;设计基于菊花链的测试样品可进行封装工艺的开发、可靠性性能的评估等。

审核编辑:汤梓红

-

封装

+关注

关注

126文章

7872浏览量

142890 -

可制造性

+关注

关注

0文章

22浏览量

6922 -

可靠性

+关注

关注

4文章

265浏览量

26735 -

DFM

+关注

关注

8文章

463浏览量

28189 -

DFR

+关注

关注

0文章

4浏览量

2898

原文标题:可制造性、可靠性和可测性协同设计,可製造性、可靠性和可測性協同設計,DFM/DFR/DFT Co-design

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

可制造性、可靠性和可测性协同设计

可制造性、可靠性和可测性协同设计

评论