当将SoC的代码分割到多片FPGA的任务完成,并且所有FPGA的资源利用都很平衡,在建议的范围50%到70%左右。此外,每个FPGA中被分配到的RTL设计的IO最小化,也就是说分割边界的IO数量是最小的,但在如此好的工作之后,仍然有可能没有足够的FPGA引脚可用于连接所有设计IO,或者更准确地说,一些FPGA之间没有足够的板载trace迹线。那这个时候的解决方案是在所用的FPGA之间复用设计信号。多路复用意味着多个兼容的设计信号通过相同的板载trace迹线被组装和串行化,然后在接收FPGA处被解复用。可以简单理解为根据时钟先按照并行转换串行的方式,将多路信号通过单路传输到另一接收的FPGA端,然后在接收的那一端转换成并行信号与此FPGA中的设计相连接,形成完整的SoC系统功能。

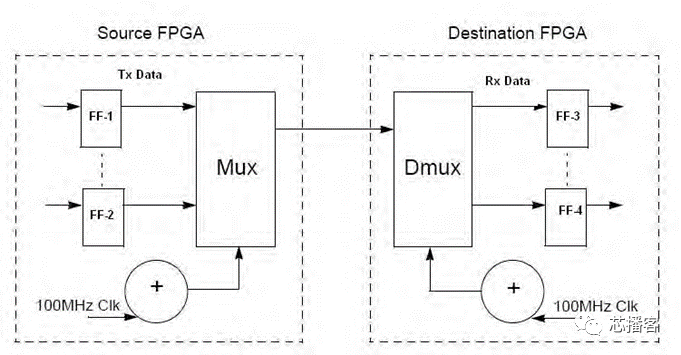

FPGA之间的两个多路复用信号需要许多组件,包括多路复用器(mux)、解复用器(dmux)、时钟源和保持所有这些相互同步的方法。

如果我们可以自由更改RTL,那么理论上,可以在每个FPGA边界手动添加这些元素。我们需要在分区之后添加复用元素,或者从一开始就将元素添加到RTL中,因此预先假设分区边界的位置。在这两种情况下,SoC团队的其他成员可能会认为这与最初的SoC的RTL相距太远,并引入了太多错误机会。

大多数团队不会考虑对SoC RTL进行如此广泛的更改,而是依赖于自动化的方式来添加复用,通过脚本化的直接编辑合成后网表,或者根据分区过程给出的方向在合成过程中进行推断。

无论采用何种方法引入多路复用,该方案的基本要求是在一个设计时钟内将IO数据值从一个FPGA传输到另一个FPGA。为了实现这一点,串行传输时钟(也称为多路复用时钟或快速时钟)必须比设计时钟更快地对这些数据值进行采样,以确保在下一个活动设计时钟边缘之前接收FPGA中的所有数据都可用。

例如,假设我们有四个IO数据值要在两个FPGA之间传输,这两个FPGA在单个板上连接上复用,即复用率为4:1。如果设计的这一部分以20MHz运行,那么,为了在设计时钟周期内传输四个设计IO,我们需要比设计时钟快至少四倍的传输时钟。因此,传输时钟必须至少为80MHz。实际上,对于4:1的多路复用,它需要快四倍以上,因为我们需要确保在数据到达传输时钟,然后在设计时钟上锁存到下游逻辑之间满足设置和保持时间。

在使用多路复用的大多数情况下,它会降低设计的总体速度,并且通常是整个系统速度的控制因素。串行传输速度受到通过FPGA IO的最大速度和通过板载轨迹的互连线的传输时间的限制。因此,由于这些物理限制,需要优化复用方案,以允许原型以最大速度运行。

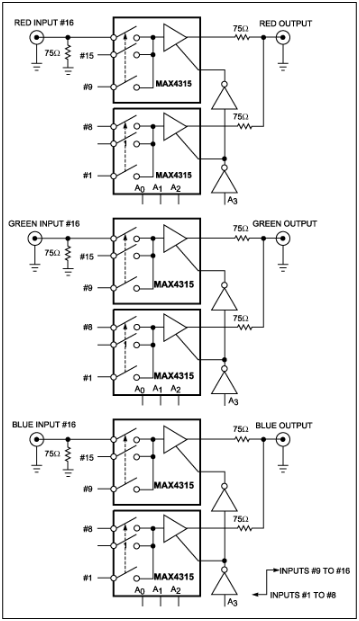

多路复用通常由插入多路复用器和多路复用器元件并用合适的信号填充分区工具支持。例如,有两种不同类型的方案,采用LVDS传输或高速时域复用(HSTDM)。

根据传输时钟和设计时钟的关系,我们可以区分两种类型的复用。异步复用,其中传输时钟与设计时钟没有相位关系,以及同步复用,其中,传输时钟相位与设计时钟对齐,甚至可能从中导出。

-

FPGA

+关注

关注

1629文章

21729浏览量

602960 -

时钟

+关注

关注

10文章

1733浏览量

131445 -

复用器

+关注

关注

1文章

707浏览量

28308

原文标题:多片FPGA原型系统:多路复用(TDM)科普

文章出处:【微信号:于博士Jacky,微信公众号:于博士Jacky】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

多路复用ICSP引脚如何控制开关?

如何在Mx1051的FlexCAN1中配置简单信号多路复用和扩展信号多路复用?

多路复用与数字复接

非多路复用与多路复用总线转换桥的设计与实现

基于多片FPGA多路复用(TDM)科普

基于多片FPGA多路复用(TDM)科普

评论