PVD篇

PVD是通过溅射或蒸发靶材材料来产生金属蒸汽,然后将金属蒸汽冷凝在晶圆表面上的过程。应用材料公司在 PVD 技术开发方面拥有 25 年以上的丰富经验,是这一领域无可争议的市场领导者。

PVD 沉积工艺在半导体制造中用于为各种逻辑器件和存储器件制作超薄、超纯金属和过渡金属氮化物薄膜。最常见的 PVD 应用是铝板和焊盘金属化、钛和氮化钛衬垫层、阻挡层沉积和用于互连金属化的铜阻挡层种子沉积。

PVD 薄膜沉积工艺需要一个高真空的平台,在这个平台上,将 PVD 沉积工艺与脱气和表面预处理技术相集成,以获得最佳的界面和薄膜质量。应用材料公司的 Endura 平台是当前 PVD 金属化的业界黄金标准。

EnduraPVD

当前 200mm 物理气相沉积 (PVD) 面临的挑战在于,要能够沉积更厚的高度均匀低温兼容性薄膜。在功率器件市场中,能够高速切换且形状系数和空间占用小的器件,正推动对先进散热技术的需求,如厚度范围为 4µm 到超过 100µm 的 Al 层。

微机电系统 (MEMS)、CMOS 图像传感器和封装技术(如硅通孔 (TSV))领域的新兴应用,正在推动氮化铝 (AlN)、氧化铟锡 (ITO)、氧化铝 (Al2O3) 和锗 (Ge) 等薄膜的 PVD 发展。

Endura PVD 200mm

应用材料公司的 Endura 平台是半导体行业有史以来最成功的金属化系统。凭借跨越前段金属化(如钴、钨、铝和铜互连)以及凸点下金属化等封装应用的沉积功能,过去 20 年制造的大多数微芯片均由 Endura 系统生产,目前,Endura 系统在全球的销量已超过 4,500 套。

Endura 能够以严格的薄膜厚度控制、出色的底部覆盖率和高共形性沉积多种超纯薄膜,这一能力是制造尖端器件的关键。该系统最多可容纳九个工艺腔室,从而能够混搭腔室,以创建集成的多步工艺序列。高度可配置的 Endura 平台支持两个可去除原生氧化物的预清洁腔室、多达六个 PVD 腔室以及两个 MOCVD 腔室(可选),以确保满足客户薄膜沉积和器件性能要求。

升级

目前有数千台 Endura 已投入使用,其中许多还是采用原始配置,因此我们提供了很多产品改进方案,可用于提升工艺性能和提高设备生产效率。例如,可通过将腔室 A 从流通腔室转换为冷却腔室,消除冷却腔室的产能瓶颈。通过 EZ LCF 可避免晶圆放置错误,同时通过严格的边缘排除来提升夹紧工艺的性能,并消除与多腔室工艺序列有关的层叠错误。此外,腔室升级可用于包括 TxZ 在内的许多腔室,以提升在片均匀性和减少维护工作。

EnduraVenturaPVD

随着二维 (2D) 器件微缩达到物理和电气极限,TSV 技术成为了一种向紧凑型、三维 (3D) 架构过渡的方法,在当前激增的移动技术中,该架构能够以较低的功耗实现更快的性能和更强大的功能。TSV 技术使产品设计师能够创建 3D 互连,通过连接堆叠芯片或晶圆的垂直路径将各个节点的电路元件相集成。

应用材料公司的 Endura Ventura PVD 系统专为 TSV 金属化而设计,是公司在物理气相沉积(PVD) 领域的最新创新,使客户能够将其 2D 镶嵌集成基础设施和专门技术扩展到深宽比 ≥10:1 的 TSV 和 2.5D 中介层应用。它也是首个面向 TSV 的 PVD 系统,可实现具有量产价值的钛阻挡层沉积。面向后段制程 (BEOL) 应用的现有 PVD 系统并不是专为此类高深宽比 (HAR) 特征而设计,这些系统需要高沉积率,以满足生产效率的要求,并实现无孔洞间隙填充和良好的可靠性。为确保间隙填充和器件可靠性所必需的连续阶梯覆盖,这些系统必须沉积相对较厚的层。除了成本更高以外,厚薄膜增加了可能降低最终良率的应力缺陷风险。

Ventura 系统可应对这些 TSV 挑战,显著降低了大规模采用这一技术的技术与成本障碍。该系统采用了改进的离子密度、方向性和可调能量,以便在 HAR TSV 内部沉积比 BEOL 系统中的层薄 50% 的连续钽或钛阻挡层和铜种子层,并大大降低了生产成本。较薄的薄膜与较高的沉积速率使 Ventura 系统的产能超过现有的 BEOL PVD 系统的一倍以上。

该系统使我们的客户能够加工他们所选择的材料。尽管应用材料公司并不出售这些材料,但 Ventura 腔室可在 Endura 平台上与铜种子层工艺相集成,灵活处理钽和钛阻挡层。这两种材料都展现出了高可靠性,但钛具有更高的成本效益。

EnduraVersaXLR2 W PVD

随着集成电路及其组件继续微缩,组件之间的金属互联线和接触件的尺寸也在缩小。其中一个结果为,这些连接器中的电阻越来越高。为生产更紧凑、更快速的电子器件,必须最大限度地降低电阻,以便能够进一步地微缩。

这种更高的电阻所造成的慢化效应通常被称做阻容延迟(或 RC 延迟),并以多种方式影响着电路。除这种不良效应以外,RC 延迟还会降低通过位线从 DRAM 结构读写数据的速度。此外,更高的电阻还会引起更高的功耗,这会为移动技术带来不良的副作用。

降低线电阻的最简单方法是增加导电金属的体积,即使导线更宽和更高。但是,更宽的导线会限制微缩,更高的导线会增加电容,并带来更大的刻蚀挑战。因此,降低尖端器件的导线电阻侧重于提升导电材料(DRAM 位线采用钨 (W))的性能。

导体电阻是电子在穿过导体时所遇散射点密度的函数。薄膜中的杂质、晶粒边界和表面粗糙度是减缓电子移动速度的某些障碍。Versa XLR2 W PVD 腔通过沉积更纯净和更光滑的钨膜来降低互联电阻,该钨膜比使用当前技术所沉积的钨的电阻率低 10-15%。

新系统借助关键硬件组件的创新实现了这一质量增强,如微波源磁控管、新颖的工艺化学和等离子体特征调制。Versa XLR2 W 系统所生产的电阻率更低的钨是微缩的促成者,它将扩展作为位线金属的钨在用于 1xnm 节点的 DRAM 技术中的用途。以下动画解释该系统的出色薄膜如何提升器件的性能。

RC 延迟举足轻重,因为这可能成为继续向下微缩逻辑和存储器设备的重大障碍,而该项技术对于提升当前的多功能、移动消费电子设备的性能至关重要。

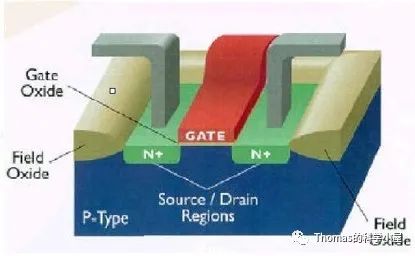

逻辑和存储芯片中的有源器件(晶体管)均通过金属线以电气方式连接彼此或芯片的其他区域。这些导线通过不导电(绝缘)介电层彼此分离。在逻辑和存储芯片中,互联线的作用为将信号从芯片的一个区域传输到另一个区域。能尽快完成信号传输,并能最大限度地降低几何尺寸缩小所造成的信号损失,这一点对器件微缩至关重要。在逻辑芯片中,微缩是指面积缩小,即借助于材料和设计创新,在更小的面积中封装越来越多的电路。在对价格敏感的 DRAM 制造领域,必须大幅控制成本,所以微缩侧重于从现有的材料和设计中获得逐步增强的性能。总之,逻辑和存储器导线中的信号传输速度受相同的基本原理支配,并取决于电阻和电容 (RC) 的乘积。同时降低电阻和电容是理想的方法。但是,对于存储器制造商而言,开发电容较低的绝缘材料并将其集成到制造流中的成本特别高。因此,降低电阻成为保证微缩后的性能的首选方法。根据电荷是垂直穿过不同的布线层,还是沿导体的长度横向通过,需要使用各种解决方案来应对 RC 挑战。尽管,无论对于哪种情况,其目标都在于最大限度地降低金属线的电阻。在垂直尺寸中,解决方案旨在最大限度地减小界面电阻。电接触件将有源区连接到第一级金属布线层。半导体-金属界面(或欧姆接触层)形成了有源区和金属接触层之间的接面。其目标在于,确保电荷能够从有源区通过接触件前往上层布线层,然后返回。为在欧姆接触层之间实现最快速和最大化的电荷传输,应形成低电阻率材料层。低电阻率硅化钴已作为此用途的行业标准被采用,其有效性依赖于能否沉积均匀的一层,以形成坚固的欧姆接触层。

EnduraiLBPVD/ALD

随着器件尺寸缩小,而集成式衬垫/阻挡层 (iLB) 厚度消耗更多的钨插头体积,接触电阻在不断增加,造成相应的困难;应用材料公司配备 Centinel沉积室的 Endura iLB PVD/ALD 系统解决了这一难题。

该系统以低成本高效的方式利用 ALD(原子层沉积)技术,通过 90% 以上覆盖超薄、均匀、优质的阻挡膜,将客户现有的 iLB PVD/CVD 安装基础扩展至 32nm 及之上。它在沉积 TiN 膜时将等离子损伤或高介电材料属性不利变化的风险降到最小,从而支持先进的内存应用。

Centinel 技术通过 RE-ALD 室(经原子团增强的原子层沉积室)增强了 Endura iLB 集成式 PVD/CVD(物理气相沉积/化学气相沉积)工艺平台,通过实现 32nm 以下逻辑器件中更小的接触电阻而优化钨体积。它也设计用于 4X 节点嵌入式 DRAM、DRAM 电极和掩埋字线应用。

Centinel 工艺实现的出色阶梯覆盖能使阻挡层厚度最小化,从而优化均匀沉积的内部特性。除了使钨填充可用的体积最大化之外,阻挡层的极限厚度减少了加工每枚硅片所需的时间,并有助于提高生产率。由于不发生背面沉积,生产率不受背面清洁的不利影响。另一项好处是沉积室工作的加工温度更低,从而减少对高介电材料的再结晶损害。

PikaPVD

应用材料公司的 Pika PVD 系统是当今业界体积最小、速度最快的单晶圆 PVD 设备,设计用于以较低的拥有成本开展高性能研发和小批量生产。该系统设计紧凑 (1657mm x 755mm x 1822mm),包含脱气、预清洁和溅射沉积模块,并配备高真空机械手传送室和完整的盒对盒自动化功能。它具有很高的可靠性,正常运行时间超过 92%。

该设备支持选择各种 PVD 溅射源,包括直流电、脉冲直流电、射频溅射,其金属或反应性溅射工艺能够共溅射金属和氧化物的合金。D 源磁控管技术的工艺流程经过验证,可在硅、玻璃、有机材料、金属和砷化镓或其他 III-V 化合物的衬底上沉积各种单层膜和多层膜。Pika 系统的即插即用设计可最大程度地减少设置时间。

TopazPVD

应用材料公司的 Applied Topaz PVD 系统可满足市场对 PLP (面板级封装)不断增长的需求,凭借领先的技术能力,可处理最大尺寸为 600mm x 600mm 的衬底。市场需要更低成本、更高性能的电子产品,而这种需求促使半导体行业从 WLP (晶圆级封装)转向 PLP。在标准化固定成本支出上,PLP 不到晶圆级封装的一半。

针对扇出型晶圆级封装(FOWLP)、LCD 和印刷电路板所开发的制程技术和设备的融合,使扇出型封装技术变得非常实惠。成本的降低将使该技术能够广泛应用于移动电子设备(例如,系统级封装、处理器、射频和电源管理)、汽车和物联网等多种半导体封装应用中。

除了 PLP,Topaz 系统还可以处理玻璃和有机中介层以及在衬底中嵌入裸片等应用。它独特的模块化架构可实现低接触电阻;将最小所需粘合强度加倍;低压力;更低的衬底温度 (<120C°);在刻蚀或激光钻孔中形成具有极佳侧壁覆盖率的共形种子层。

Axcela PVD

在过去十年的应用中,堪称同类最佳的 应用材料公司 Axcela PVD 系统已证明了其工艺优越性和稳定性,非均匀度小于 2% 1σ。每个溅射腔室在设计上都尽量降低设备拥有成本,方便保养维护,可形成厚达 8µm 的厚膜,标配沉积三种不同材料的能力,并且可以选择共溅射以提高沉积速率。该系统结构紧凑,可采用 150、200、300 或 330mm 等多种组合配置。系统包括脱气、预清洁和 PVD 腔室模块,可满足多种应用需求,以及最优的工艺和产量要求。这种简单易行的系统配置能力,使客户可为特定的应用来选择最理想的配置。

Axcela 系统的小批量集群架构使这种高度可靠的 PVD 工具成为大多数金属化应用(包括 EMI 屏蔽、背面金属化、MEMS、TSV、UBM 和 RDL)的绝佳选择。它可以严格控制薄膜的沉积厚度,从而帮助工艺和制造工程师以满足苛刻的设计要求。

D 源磁控管可通过全面腐蚀来提高标靶利用率。腔室和靶材的架构,使其可以最大效率收集从靶材溅射出来的原子,而不是将其浪费在屏蔽罩上。磁控管和屏蔽罩的设计方便了系统的超低颗粒计数。

200mm 和 300mm 腔室中带封装的 EMI 环

ChargerUBM PVD

应用材料公司的 Charger UBM PVD 系统在芯片封装金属沉积工艺的生产效率和可靠性方面树立了新的标准。Charger 系统专为 UBM、RDL 和 CMOS 影像传感器应用而设计,它采用线性架构,其晶圆产量是其他同类设备的两倍以上,达到市面上最高的生产效率。此外,系统集成最新的 Volaris预清洗技术,在两次保养间隔期内可处理更多的晶圆,达到极长的无故障运行时间,并实现目前最低的单位晶圆成本。

Volaris 预清洗腔室在设计上能最大程度减少有机膜除气所带来的污染物,与传统的电感耦合等离子体溅镀反应腔室相比,可将传统应用中的同类最佳接触电阻性能扩展到最先进的技术节点。这种独特的原位清洗技术延长了工艺套件的使用寿命,降低了预防性维护保养的频率,从而降低了生产成本,提高了产量,最大程度减少了客户的封装沉积系统拥有成本。

优良的磁控和 PVD 反应腔室经过改进,对于 UBM 和 RDL 应用中使用的各种金属(如 Ti、TiW、Cu 和 NiV),可满足严格的薄膜沉积均匀性规格。

Charger 系统模组架构增强了配置灵活性,可在极短的停机时间内,将紧凑的三反应腔室配置轻松扩展为五反应腔室的大规模量产制造系统。

EnduraALPSPVD (ALPS Co & Ni)

应用材料公司的 Endura ALPS(先进低压源)Cobalt PVD(物理气相沉积)系统为高深宽比结构的栅极和接触孔应用提供简单的高性能金属硅化物解决方案。ALPS 技术将钴延伸至 90nm 技术节点以下,可提供优良的钴底部覆盖,且不会对器件造成等离子损伤,缺陷数量极少。Endura ALPS Co 提供出色的电阻率、低漏电流和热稳定性,解决了钛凝聚、接触孔电阻变化和掺杂物吸出等难题。

对于 65nm/55nm 及以下节点的逻辑和存储应用,钴的硅消耗和硅化钴/硅界面的粗糙度变得更加关键。Endura ALPS Ni PVD 系统可沉积稳定的硅化镍薄膜,使硅消耗量减少 2 倍,薄膜界面更平滑,电阻率更低。ALPS Ni 可实现 100Å 底部覆盖,不对器件造成等离子损伤,同时还能最大程度减少微粒数量。

应用材料公司的 Endura ALPS Ni PVD 系统采用单腔室 Siconi Preclean 界面处理技术,解决了硅化镍 (NiSi) 沉积前硅表面清洗准备的难题。Siconi Preclean 可提供高选择比清洗 (>20:1 SiO2:Si, >5:1 SiO2:SiN),无需传统 HF 清洗工艺所必需的清洗与镍沉积之间的严格等候时间控制。通过远程等离子源生成刻蚀剂,可减少对衬底的损坏,最大程度减少对氮化硅间隔层和硅栅等结构的刻蚀。此外,器件研究表明,与传统 HF 浸洗法相比,Siconi Preclean 能减少 NiSi2尖峰缺陷,改善结漏电。

EnduraAmberPVD

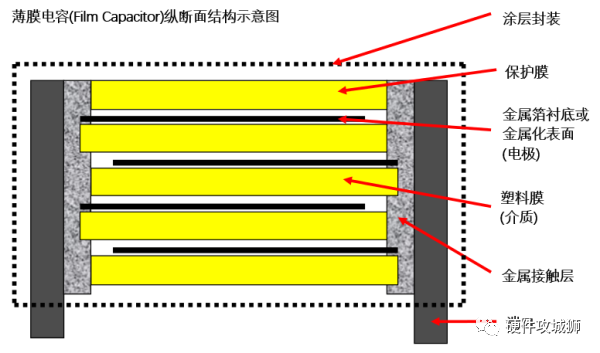

可靠及完整地用铜填充互连沟槽和通孔结构,对于微电子制造的器件可靠性非常重要。该工艺的必要步骤为沉积阻挡层(防止铜扩散至周围绝缘材料)和铜种子层[方便随后的电化学沉积(或电镀)],使其不会出现孔洞和缝隙。

迄今为止,电离物理气相沉积 (PVD)已能在所有电镀表面达到所需的覆盖厚度和连续性。但是,当节点小于 2xnm 时,即使采用最优化的阻挡层/种子层工艺,覆盖完好无任何凸悬,也无法控制特征深宽比来满足电镀要求。

独特的 Endura Amber PVD 系统通过成熟的集成化方法,将冷沉积工艺与高温热铜回流工艺相结合,取代了 EnCoRe II RFX 铜晶种技术,一举解决了这一难题。在 1xnm 技术节点下,超小通孔开口周围会出现铜凸悬,使得无法采用常规的 PVD 工艺达到最佳电镀所需的侧壁和种子层覆盖。新系统扩展了当前技术的应用,通过铜回流,增强了 PVD 沉积工艺,实现自底向上的填充。这个两步骤工艺通过减少通孔的有效深宽比(应用一次)或完全填充通孔(重复应用),简化了电镀过程,使无孔洞填充更有保障,从而确保器件的可靠性。沉积/回流工艺中的每一步都能独立控制温度,可灵活地与各种衬垫材料结合使用。

这一创新的铜晶种技术与预清洁和 EnCoRe II Ta(N) 阻挡层技术在高度真空条件下整合至 Endura 平台,在量产中可达到高的器件良率。

EnduraAvenirRF PVD

对于高纵横比 Ni(Pt) 逻辑接触硅化,该系统在高压电容耦合等离子体模式下运行,可产生更高的金属电离密度,从而实现更好的底部覆盖。

随着器件尺寸缩减,特征变得更加脆弱,深宽比不断增加,使当前的 PVD(物理气相沉积)技术在填充较深的狭窄结构、避免等离子损伤方面的难度升高。使用基于 RF 的低功率等离子体可最大限度地减轻损伤风险,并取得更均匀的等离子体密度分布,从而能够实现更好的底部覆盖和更高的均匀度。

Endura Avenir 系统的 RF PVD 解决了 22nm 及以下节点的高 K / 金属栅极应用以及逻辑接触硅化物问题。

对于高 K / 金属晶体管,Avenir 系统为前栅极和后栅极集成方案提供了各种解决方案,从而使芯片制造商能够在这两种方法之间轻松转换。对于前栅极,RF PVD 技术能够实现可控的高均匀度连续薄膜沉积 (<10Å)。对于后栅极,高压力电容耦合等离子体操作可用于确保良好的底部覆盖率和最小的悬突。该系统的 RF PVD 技术不仅可以沉积超薄覆盖层和金属栅极薄膜,还可以最大限度地降低损伤风险,从而形成无电荷陷阱的突变界面。该系统的调优能力能够实现精确的 TiN 薄膜化学计量控制,以便在不牺牲薄膜均匀度的前提下实现整体 Vt 控制。就有效功函数而言,该需求可转换为 <4.2eV(对于 NMOS)和>5.0eV(对于 PMOS),以便实现高性能。对于NMOS和> 5.0eV用于高性能的PMOS。

对于高深宽比的 Ni(Pt) 逻辑接触硅化物,该系统在高压力电容耦合等离子体模式下运行,以便实现更高的金属电离密度和底部覆盖率。

RF PVD 硅化腔室所实现的底部覆盖率比传统的 PVD Ni(Pt) 工艺高一倍,它可以在深宽比为 5:1 的特征层底部实现大于 70% 的场厚度,并在特征层之内以及晶圆的中心到边缘之间实现一致的底部覆盖率。一致的底部覆盖率 (3%, 1σ) 可转化为一致的电阻和更低的泄漏率,而高铂组分均匀度可转化为高器件成品率。相比传统的 PVD Ni(Pt) 技术,该系统在提供这一性能的同时将耗材成本降低了 30%。

在生产中久经考验的 Endura 平台可为高 K / 金属栅极和逻辑接触硅化物应用提供了独特的集成能力。对于栅极应用,它提供了全套 PVD、CVD 和 ALD 技术。对于接触层,它将 Siconi 预清洁、硅化和氮化钛覆盖工艺结合在一起。

EnduraCirrusHT CO PVD

随着集成电路及其组件继续微缩,组件之间的金属互联线和接触件的尺寸也在缩小。其中一个结果为,这些连接器中的电阻越来越高。为生产更紧凑、更快速的电子器件,必须最大限度地降低电阻,以便能够进一步地微缩。

这种更高的电阻所造成的慢化效应通常被称做阻容延迟(或 RC 延迟),并以多种方式影响着电路。除这种不良效应以外,RC 延迟还会降低通过位线从 DRAM 结构读写数据的速度。此外,更高的电阻还会引起更高的功耗,这会为移动技术带来不良的副作用。

微缩的另一个副作用为,深宽比随着先进电路中的特征密度增加而增加。结果,以足够的底部覆盖率沉积薄膜变得越来越具挑战,而足够的覆盖率是最终器件达到适当的电气性能所必需的。DRAM 结构中尤为重要的是有源区和第一级金属互联层之间的半导体-金属界面。为在这些界面之间实现最快速和最大化的电荷传输,应使用低电阻率材料(硅化钴),其有效性取决于适当的沉积厚度和均匀的界面层。

Endura Cirrus HT Co PVD 系统可通过增强功能来实现所需的硅化物覆盖率,以应对缩小的接触面积和增加的深宽比所带来的挑战。相比其他来源技术,使用高频 RF 源可产生金属离子浓度更高的等离子体,该系统可在高深宽比特征层的底部实现出色的厚度和一致性。晶圆上的负电压用于将正金属离子引入窄孔中,由于存在更多的金属离子,所以高深宽比接触孔底部的覆盖度比当前技术所实现的覆盖度厚两倍或三倍。因此,形成了坚固的硅化钴层,以降低电荷在金属和半导体之间的传输壁垒。

该系统将 Siconi 硅化物预清洁与用于 DRAM 外围电路中的直接接触应用的 PVD 钴和氮化钛盖帽沉积结合在一起。

欧姆接触层的挑战

在存储设备中,欧姆接触层(半导体-金属界面)将有源区与金属布线层连接在一起。随着存储器继续微缩,节点之间的欧姆接触层面积缩小了约 70%,特征层中的深宽比增加,在特征层中必须沉积低电阻率硅化物,以形成该接触层。在 1xnm DRAM 中,这两个因素使形成足够厚的硅化钴层日益困难,而足够的厚度是为了确保电荷能够快速、可靠地从有源区通过接触件前往上层布线层,然后返回。

以下动画阐明了欧姆接触层的概念以及 Endura Cirrus HT Co PVD 系统所产生的厚硅化物覆盖层对设备性能的有利影响。

RC 延迟举足轻重,因为这可能成为继续向下微缩逻辑和存储器设备的重大障碍,而该项技术对于提升当前的多功能、移动消费电子设备的性能至关重要。

逻辑和存储芯片中的有源器件(晶体管)均通过金属线以电气方式连接彼此或芯片的其他区域。这些导线通过不导电(绝缘)介电层彼此分离。在逻辑和存储芯片中,互联线的作用为将信号从芯片的一个区域传输到另一个区域。能尽快完成信号传输,并能最大限度地降低几何尺寸缩小所造成的信号损失,这一点对器件微缩至关重要。在逻辑芯片中,微缩是指面积缩小,即借助于材料和设计创新,在更小的面积中封装越来越多的电路。在对价格敏感的 DRAM 制造领域,必须大幅控制成本,所以微缩侧重于从现有的材料和设计中获得逐步增强的性能。总之,逻辑和存储器导线中的信号传输速度受相同的基本原理支配,并取决于电阻和电容 (RC) 的乘积。同时降低电阻和电容是理想的方法。但是,对于存储器制造商而言,开发电容较低的绝缘材料并将其集成到制造流中的成本特别高。因此,降低电阻成为保证微缩后的性能的首选方法。根据电荷是垂直穿过不同的布线层,还是沿导体的长度横向通过,需要使用各种解决方案来应对 RC 挑战。尽管,无论对于哪种情况,其目标都在于最大限度地降低金属线的电阻。在垂直尺寸中,解决方案旨在最大限度地减小界面电阻。电接触件将有源区连接到第一级金属布线层。半导体-金属界面(或欧姆接触层)形成了有源区和金属接触层之间的接面。其目标在于,确保电荷能够从有源区通过接触件前往上层布线层,然后返回。为在欧姆接触层之间实现最快速和最大化的电荷传输,应形成低电阻率材料层。低电阻率硅化钴已作为此用途的行业标准被采用,其有效性依赖于能否沉积均匀的一层,以形成坚固的欧姆接触层。在横向尺寸中,解决方案旨在优化导线金属材料的导电性。所谓的线性电阻表示导线尺寸(宽、高、长)与导线制备材料(通常为钨或铜)的特定性能的函数。降低线电阻的最简单方法是增加导电金属的体积,即使导线更宽和更高。但是,更宽的导线会限制微缩,更高的导线会增加电容,并带来更大的刻蚀挑战。因此,降低尖端器件的导线电阻侧重于提升导电材料的性能。

EnduraCirrusHTX PVD

通过革新用于氮化钛 (TiN) 薄膜的物理气相沉积 (PVD) 技术,Endura Cirrus HTX TiN 解决了下一代设备的硬掩膜可扩展性挑战。随着芯片特征尺寸的进一步缩小,硬掩膜创新对于更复杂微小互连结构的精确图形化至关重要。借助在 PVD 领域多年的专门技术,新系统可生产能够在 10nm 以下的节点中确保图案保真度的突破性硬掩膜。

随着芯片设计的发展,芯片的特征尺寸逐渐变小、深宽比变得更高、封装越来越密集,以便生产先进的集成电路。结果,在创建电路(或互联线)时,用于定义刻蚀的和金属化的图形的材料对保持这些图形的完整性极其重要。轻微的缺陷可能造成无法适当地金属化器件,使其不可靠或无功能。

在互连线制造工艺中,氮化钛 (TiN) 一直是低 K 介电质图形化的标准硬掩膜材料。然而,在先进节点,为降低器件电容,将介电质逐渐制作得更加多孔,使其变得更脆弱,并且在叠加的 TiN 掩膜的压缩应力影响下,容易在刻蚀后变形(线路弯曲和图形坍塌)。尽管消除这一自然压缩应力会降低薄膜密度,但这对耐受刻蚀工艺是必须的。

在一项重大突破中,Endura Cirrus HTX PVD 系统采用了频率极高的 RF 源,以产生便于修改薄膜的结晶定向的高度电离化等离子体,从而解决了应力和密度之间的棘手权衡。最终形成的 TiN 达到了抗张应力性与高密度的理想结合,从而带来极佳的刻蚀选择比、出色的 CD 线宽控制和通孔堆叠对准,以及密集复杂图形的高保真度。出色的薄膜厚度均匀性与低缺陷率使新系统能够减少变异性和产生非常精确的图形。

EnduraCloverMRAM PVD

应用材料公司的 Endura Clover MRAM PVD s系统是用于磁性随机存取存储器 (MRAM) 器件大规模量产 (HVM) 的首款具有生产价值的集成材料解决方案(Integrated Materials Solution)。闪存基于电荷的运行特性使其面临着缩放限制;MRAM 最有望成为其替代品,因为其基于电阻的运行更具可缩放性,同时还提供了存储器半导体应具备的关键特性:非易失性、随机访问和强大的耐用性。

EnduraCuBS RFX PVD

应用材料公司的 Endura CuBS(铜阻挡层/种子层)RF XT PVD 系统用于 3x/2x 及更先进节点的逻辑和存储器件应用。SIP(自离子化等离子体)EnCoRe II Ta(N) 阻挡层和 EnCoRe II RFX 铜晶种层处理室采用高电离 PVD 技术,该技术能够以最小的悬突和光滑的形态实现完全覆盖的低温薄膜沉积。

EnCoRe II Ta(N) 腔的厚度调优功能使客户能够降低阻挡层的厚度,以便将线性电阻微缩到 3x/2x 节点的水平,同时通过出色的底部和侧壁覆盖层减少电迁移和应力迁移。对于铜晶种层,EnCoRe II RF XT Cu 腔采用了创新的磁控运动、磁通量控制和高再溅射比机制,以进一步增强同形覆盖。

这些技术缓解了会降低金属空隙填充品质的问题,如晶圆边缘的线端孔隙或 CMP 处理后的缺陷。

为解决随几何尺寸缩小而日益重要的界面问题,应用材料公司提供了各种预清洁技术,以便在不影响关键尺寸或材料特性的前提下,确保界面完整性。Endura CuBS RF XT 系统采用了新型 Aktiv Preclean [腔体或工艺] 方法,该方法提供了突破性的预清洁技术,以便有效地去除聚合物残留和减少 CuO,同时保护多孔的低 k 级间介电薄膜,如Black Diamond II。和传统的反应性预清洁方法不同的是,Aktiv Preclean 工艺不会明显改变 k 值,所以这便于向下一代低 k 介电层过渡。

应用材料公司的 Endura CuBS RF XT PVD 系统在高真空条件下依次沉积 Ta(N)/Ta 阻挡层,然后沉积铜种子层。通过在 Endura 平台上整合全系产品(包括新型 Aktiv Preclean),可确保出色的膜层附着力和无氧化物界面,同时保持 k 值完整性,以实现低通孔电阻和高器件可靠性。

EnduraImpulsePCRAM PVD

应用材料公司的EnduraImpulsePVD系统是用于相变随机存取存储器 (PCRAM) 和电阻式随机存取存储器 (ReRAM) 器件大规模量产 (HVM) 且具有生产价值的集成材料解决方案(Integrated Materials Solution)。PCRAM 和 ReRAM 是新兴的非易失性存储器,可填补 DRAM(用于数据处理)和 NAND(用于数据存储)之间不断扩大的性价比差距。PCRAM 和 ReRAM 可以提高存储和检索的速度、用电效率和可靠性,即使在断电时也能保留软件和数据。

EnduraIoniqW PVD

随着集成电路及其组件不断微缩,组件之间的金属互联线和导线的尺寸也在缩小。由此带来的一个结果是,这些互连结构的电阻越来越高。

这种高电阻会造成慢化效应,通常称为阻容延迟(或 RC 延迟),它会降低传导速度,增加功耗,从而影响芯片性能。为了制造结构更紧凑、速度更快的电子器件,必须最大限度降低这些连接结构的电阻,使其能进一步微缩。

应用材料公司新推出的 Endura Ioniq PVD 系统是一种 Integrated Materials Solution(集成材料解决方案),它在一个高度真空的平台上将先进的制造工艺与 CVD 技术和预处理腔室相结合,可在各种导线应用中实现纯钨(W)材料金属化。它取代了需要多台设备来完成的、具有高电阻的单一的氮化钛衬底、钨成核层和大块钨填充物,代而采用融合 CVD 大块钨填充物的单一 PVD 钨层。Ioniq PVD 腔室增强的电离功能和定向流量控制打造出极佳的均匀阶梯式覆盖纯钨膜,用作低电阻的阻隔层和衬垫层。持续的高真空环境可保持薄膜的完整性,进一步提高了金属界面的纯度和电导率。

应用材料公司的 Endura Ioniq PVD 系统将钨(W)在逻辑应用中的关键导线处的使用扩展到了 5 纳米以下,同时也为 DRAM 和 NAND 器件的低电阻连接提供了一种独特的金属化方法,有助于进一步推进器件微缩。

-

晶圆

+关注

关注

52文章

4890浏览量

127930 -

逻辑器件

+关注

关注

0文章

88浏览量

20099 -

PVD

+关注

关注

4文章

49浏览量

16969

原文标题:Applied Materials产品库----PVD篇

文章出处:【微信号:半导体设备与材料,微信公众号:半导体设备与材料】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

浅谈薄膜沉积

第三代半导体热潮“带货”沉积设备需求,供应链与服务本地化成关键考量

芯片薄膜工艺是什么

物理气相沉积及溅射工艺(PVD and Sputtering)

半导体设备行业跟踪报告:ALD技术进行薄膜沉积工艺优势

韫茂科技获数亿元融资,加快薄膜沉积设备量产

沉积氮化硅薄膜的重要制备工艺——PECVD镀膜

基于PVD 薄膜沉积工艺

基于PVD 薄膜沉积工艺

评论