端口

端口是模块与外界交互的接口,对外部环境而言,模块内部是不可见的,对模块的调用只能通过端口连接进行

端口基本语法约定如下:

端口必须被声明

端口声明不可重复

端口声明既可在端口列表内也可在列表外

模块间的数据只能通过端口进行

端口声明

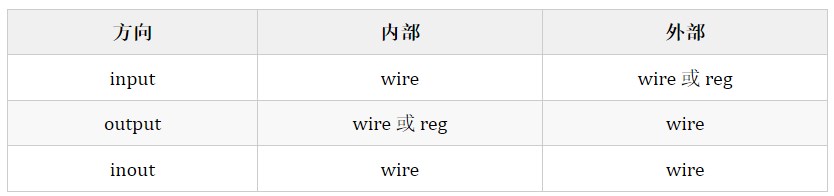

根据端口的方向,端口类型有3种:输入(input)、输出(output)和双向端口(inout)

- input 和 output 只能是

wire型 - output 既可以是

wire也可以是reg- 需要保存数值时,用

reg - 不需要保存数值时,用

wire

- 需要保存数值时,用

reg类型是用于保存数值的,而输入端只能反映与其相连的外部信号的变化,并不能保存这些信号的值

端口连接规则

对于inpu和output我是这样理解的,内部是reg外部就应该是wire

就比如input这一端,外部是reg,内部是wire,在这个一端,已经有一个reg类型可以用来保存数据,不需要用到两个reg来保存数值

端口连接方式

端口连接的方式有两种:按位置连接 和 按名称连接

- 按位置连接

调用模块的端口名必须与被调用模块端口列表中的位置保持一致//调用模块 module name(……); //端口定义 //端口描述 /*a, b, c, d分别对用调用模块 中的in1, in2, sel, dout*/ mux u1(a, b, c, d); endmodule //调用模块 module mux (in1, in2, sel, dout); //端口定义 //端口描述 //逻辑描述 endmodule - 按名称连接

格式为:模块名 模块实例化名 (.被调用模块端口名(调用模块端口名));

其中,模块实例化名是自己随意定的一个名字,方便记忆就好//调用模块 module name(……); //端口定义 //端口描述 //模块调用,也叫实例化 //对应方式和上一个相同 mux u1(.in1(a), .in2(b), .sel(c), .dout(d)); endmodule //被调用模块 module mux(in1, in2, sel, dout); //端口定义 //端口描述 //逻辑描述 endmodule

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网

网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Verilog设计

+关注

关注

0文章

20浏览量

6517 -

verilog接口

+关注

关注

0文章

2浏览量

4494

发布评论请先 登录

相关推荐

使用Verilog/SystemVerilog硬件描述语言练习数字硬件设计

在实例化模块时,使用Verilog时有两种常用的方式来进行模块端口的信号连接:按端口顺序以及按端口名称连

SDI_OUT端口与屏幕连接后显示噪音该怎么办?

mvisdi_viodc_2VP7.bit从'viodc_sdi_verilog \ Bit Files'目录复制到fpga芯片。但它不起作用。板的SDI-IN端口与视频信号连接,SDI_OUT

发表于 08-14 07:15

Verilog 模块与端口

:输入、输出端口可以采用向量的方式表示,例如:4输入端a0,a1,a2,a3,与4输入端b0,b1,b2,b3, 一一对应相与,其结果赋给对应的c0,c1,c2,3;Verilog 的描述如下

发表于 07-23 23:08

Verilog代码命名六大黄金规则

德赢Vwin官网

网核心提示: 关于Verilog代码中命名的六大黄金规则。 1. 系统级信号的命名。 系统级信号指复位信号,置位信号,时钟信号等需要输送到各个模块的全局信号;系统信号以字

发表于 09-04 14:40

•6140次阅读

Verilog HDL的基础知识详细说明

硬件描述语言基本语法和实践

(1)VHDL 和Verilog HDL的各自特点和应用范围

(2)Verilog HDL基本结构语言要素与语法规则

(3) Verilog HDL组

发表于 07-03 17:36

•54次下载

Verilog系统函数和边沿检测

“ 本文主要分享了在Verilog设计过程中一些经验与知识点,主要包括Verilog仿真时常用的系统任务、双向端口的使用(inout)、边沿检测”

System Verilog的概念以及与Verilog的对比

Verilog模块之间的连接是通过模块端口进行的。 为了给组成设计的各个模块定义端口,我们必须对期望的硬件设计有一个详细的认识。 不幸的是,在设计的早期,我们很难把握设计的细节。 而且

verilog双向端口的使用

在Verilog硬件描述语言中,端口是指连接模块(Module)与其他模块、寄存器或是物理设备的输入或输出接口。单向端口可以作为输入或输出使用,而双向

verilog调用模块端口对应方式

Verilog是一种硬件描述语言(HDL),广泛应用于数字电路设计和硬件验证。在Verilog中,模块是构建电路的基本单元,而模块端口对应方式则用于描述模块之间信号传递的方式。本文将介绍

verilog中端口类型有哪三种

在 Verilog 中,端口类型有三种:输入端口(input)、输出端口(output)和双向端口(inout)。 输入

Verilog表达式的位宽确定规则

很多时候,Verilog中表达式的位宽都是被隐式确定的,即使你自己设计了位宽,它也是根据规则先确定位宽后,再扩展到你的设计位宽,这常常会导致结果产生意想不到的错误。

Verilog端口连接规则

Verilog端口连接规则

评论