来源:碳化硅研习社

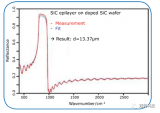

外延层是在晶圆的基础上,经过外延工艺生长出特定单晶薄膜,衬底晶圆和外延薄膜合称外延片。其中在导电型碳化硅衬底上生长碳化硅外延层制得碳化硅同质外延片,可进一步制成肖特基二极管、MOSFET、 IGBT 等功率器件,其中应用最多的是4H-SiC 型衬底。

由于碳化硅功率器件与传统硅功率器件制作工艺不同,不能直接制作在碳化硅单晶材料上,必须在导通型单晶衬底上额外生长高质量的外延材料,并在外延层上制造各类器件,所以外延的质量对器件的性能是影响非常大。不同的功率器,它的性能的提高也对外延层的厚度、掺杂浓度以及缺陷提出了更高要求。

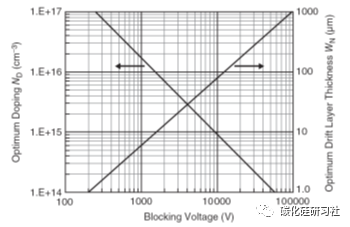

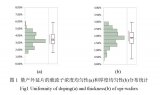

图1.单极型器件外延层的掺杂浓度和厚度与阻断电压关系曲线

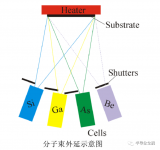

碳化硅外延层的制备方法主要有:蒸发生长法;液相外延生长(LPE);分子束外延生长(MBE);化学气相沉积(CVD)。

这里对这几种制备方法做了一个基本的总结,见表1。化学气相沉积(CVD)法是目前工厂大批量生产用的主要方法。

| 制备方法 | 工艺的优点 | 工艺的缺点 |

| 液相外延生长 (LPE) | 设备需求简单并且成本较低的生长方法。 | 很难控制好外延层的表面形貌。设备不能同时外延多片晶圆,限制了批量生产。 |

| 分子束外延生长(MBE) | 可以在低生长温度下生长不同的 SiC 晶型外延层 | 设备真空要求度很高,成本高昂。生长外延层速率慢 |

| 化学气相沉积(CVD) | 工厂批量生产最主要的方法。生长厚外延层时能够对生长速率精确控制 | SiC 外延层仍然存在各种缺陷,从而对器件特性造成影响,所以针对 SiC 的外延生长工艺需要进行不断的优化 |

| 蒸发生长法 | 使用和SiC拉晶同样的设备,工艺和拉晶稍微有区别。设备成熟,成本低 | SiC 的蒸发不均匀,很难利用其蒸发生长出较高质量的外延层 |

表1. 外延层主要制备方法的比较

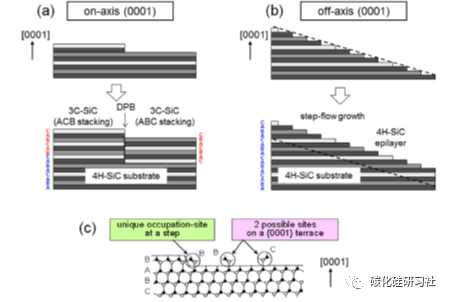

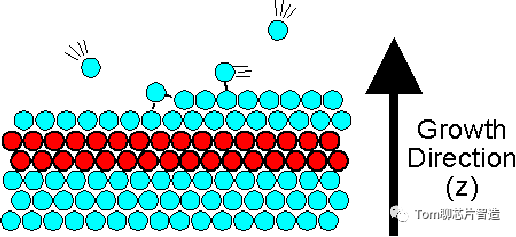

在有一定倾斜角度的偏轴{0001}衬底上,如图2(b)示意图,台阶面的密度很大而且台阶面很小,晶体成核不容易在台阶面上发生,多发生在台阶的并入点出,这里只存在一种成核键位。所以外延层可以完美地复制衬底的堆垛次序,消除多型体共存的问题。

图2. 4H-SiC台阶控制外延法的物理过程示意图

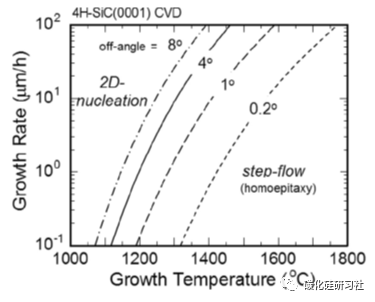

图3. 4H-SiC台阶控制外延法CVD生长临界条件

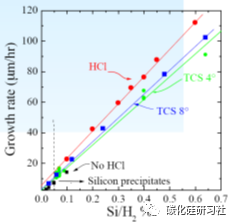

图4. 4H-SiC外延中不同硅源下的生长速率比较

目前在中低压应用领域(比如1200伏器件),碳化硅外延的技术相对成熟。它的厚度均匀性、掺杂浓度均匀性以及缺陷分布可以做到相对较优的水平,基本可以满足中低压 SBD、MOS、JBS 等器件需求。

但在高压领域,目前外延片需要攻克的难关还很多。比如10000伏的器件需要的外延层厚度为100μm左右,该外延层的厚度和掺杂浓度均匀性比低压器件的外延层差很多,尤其是掺杂浓度的均匀性,同时它的三角缺陷也破坏了器件的整体性能。在高压应用领域,器件的类型趋向于使用双极器件,对外延层的的少子寿命要求比较高,也需要优化工艺来提高少子寿命。

当前国内外延主要以 4 英寸和 6 英寸为主,大尺寸碳化硅外延片占比逐年递增。碳化硅外延尺寸主要受制于碳化硅衬底尺寸,当前 6 英寸碳化硅衬底已经实现商用,因此碳化硅衬底外延也逐渐从 4 英寸向 6 英寸过渡。

随着碳化硅衬底制备技术的提升及产能扩张,碳化硅衬底价格正在逐步降低。在外延片价格构成中,衬底占据了外延 50%以上的成本,随着衬底价格的下降,碳化硅外延价格也有望降低。

审核编辑:汤梓红

-

MOSFET

+关注

关注

147文章

7156浏览量

213126 -

晶圆

+关注

关注

52文章

4890浏览量

127929 -

工艺

+关注

关注

4文章

592浏览量

28779 -

SiC

+关注

关注

29文章

2804浏览量

62603 -

碳化硅

+关注

关注

25文章

2748浏览量

49014

原文标题:SiC外延工艺基本介绍

文章出处:【微信号:汽车半导体情报局,微信公众号:汽车半导体情报局】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

半导体制造之外延工艺详解

启用PowerFill外延硅工艺的电源设备

采用PowerFill外延硅工艺的电源器件

沟槽型SiC MOSFET工艺流程及SiC离子注入

氮化镓外延片工艺介绍 氮化镓外延片的应用

氮化镓外延片工艺流程介绍 外延片与晶圆的区别

SiC外延片是SiC产业链条的核心环节吗?

SiC外延片测试需要哪些分析

分子束外延(MBE)工艺及设备原理介绍

SiGe外延工艺及其在外延生长、应变硅应用及GAA结构中的作用

SiC外延工艺基本介绍

SiC外延工艺基本介绍

评论