编者按

中国科学院大学集成电路学院是国家首批支持建设的示范性微电子学院。为了提高学生对先进光刻技术的理解,本学期集成电路学院开设了《集成电路先进光刻技术与版图设计优化》研讨课。在授课过程中,除教师系统地讲授外,学生还就感兴趣的课题做深入调研。师生共同讨论调研报告,实现教学互动。调研的内容涉及光刻工艺、光刻成像理论、SMO、OPC和DTCO技术。

考虑到这些内容也是目前业界关注的实用技术,征得教师和学生的同意,本公众号将陆续展示一些学生的调研结果。这些报告还很初步,甚至有少许谬误之处,请业界专家批评指正。

以下为报告PPT:

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网

网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

集成电路

+关注

关注

5387文章

11530浏览量

361627 -

NAND

+关注

关注

16文章

1681浏览量

136118 -

3D

+关注

关注

9文章

2875浏览量

107480 -

光刻技术

+关注

关注

1文章

146浏览量

15817 -

刻蚀工艺

+关注

关注

2文章

37浏览量

8414

原文标题:【Study】3D NAND刻蚀工艺的挑战及特点

文章出处:【微信号:光刻人的世界,微信公众号:光刻人的世界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

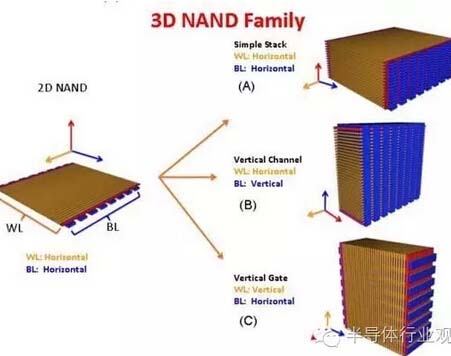

干货!一文看懂3D NAND Flash

目前3D NAND仅由三星电子独家量产。而进入了最近两个月,先有东芝(Toshiba)杀入敌营,如今美光(Micron)也宣布研发出3D NAND 芯片,而且已经送样,三星一家独大的情

发表于 08-11 13:58

•4.3w次阅读

3D NAND良率是NAND Flash市场最大变数

据海外媒体报道,去年下半年以来NAND Flash市场供不应求,主要关键在于上游原厂全力调拨2D NAND Flash产能转进3D NAND

发表于 02-27 09:21

•1482次阅读

【半导体存储】关于NAND Flash的一些小知识

NAND就是高楼大厦,建筑面积成倍扩增,理论上可以无限堆叠,可以摆脱对先进制程工艺的束缚,同时也不依赖于极紫外光刻(EUV)技术。

[]()

与2D NAND缩小Cell提高存储

发表于 12-17 17:34

3D NAND技术工艺发展与主流内存标准探讨

本文为您讲述ROM存储介质3D NAND技术工艺的发展,现阶段主流的内存标准,包括传统eMMC,三星和苹果提出的UFC标准和NVMe标准。

发表于 10-12 15:54

•3420次阅读

3D工艺的转型步伐较慢,NAND闪存依然处于供给吃紧的状态

今年第三季度,NAND闪存依然处于供给吃紧的状态,主要是颗粒厂面向3D工艺的转型步伐较慢,低于预期。

发表于 09-16 10:38

•599次阅读

半导体行业3D NAND Flash

,以致于达到某个点之后制程工艺已经无法带来优势了。相比之下,3D NAND解决问题的思路就不一样了,为了提高NAND的容量、降低成本,厂商不需要费劲心思去提高制程

发表于 10-08 15:52

•525次阅读

美光发布176层3D NAND闪存

存储器厂商美光宣布,其第五代3D NAND闪存技术达到创纪录的176层堆叠。预计通过美光全新推出的176层3D NAND闪存技术以及架构,可以大幅度提升数据中心、智能边缘计算以及智能手

未来的3D NAND将如何发展?

NAND 应运而生,可以支持在更小的空间内容纳更高的存储容量,在需要存储海量数据的时代有着重大价值。 依托于先进工艺的 3D NAND,氧化层越来越薄,面临可靠性和稳定性的难题,未来

未来的3D NAND将如何发展?如何正确判断一款3D NAND的总体效率?

依托于先进工艺的 3D NAND,氧化层越来越薄,面临可靠性和稳定性的难题,未来的 3D NAND 将如何发展?如何正确判断一款

不要过于关注3D NAND闪存层数

NAND应运而生,可以支持在更小的空间内容纳更高的存储容量,在需要存储海量数据的时代有着重大价值。 依托于先进工艺的3D NAND,氧化层越来越薄,面临可靠性和稳定性的

什么是3D NAND闪存?

我们之前见过的闪存多属于Planar NAND平面闪存,也叫有2D NAND或者直接不提2D的,而3D 闪存,顾名思义,就是它是立体堆叠的,

3D NAND刻蚀工艺的挑战及特点

3D NAND刻蚀工艺的挑战及特点

评论