本文转自半导体行业观察

过去50多年来,半导体行业一直沿着摩尔定律的步伐前行,晶体管的密度不断增加,逐渐来到百亿级别,这就带来了密度和成本上的极大挑战。随着摩尔定律逼近极限,传统的单片半导体器件已不再能够满足某些计算密集型、工作负载重的应用程序的性能或功能需求。如何进一步有效提高芯片性能同时把成本控制在设计公司可承受的范围内,成为了半导体产业链一致的难题。

对此,新思科技提出了一个新的设计理念——“SysMoore”。“Sys”取自System(系统),指的是要在系统层面提升芯片的性能,而不仅仅是在晶圆中集成更多的晶体管数量。在SysMoore的时代,Multi-Die系统正在成为超越摩尔定律和解决系统复杂性挑战的解决方案,它能实现以经济高效的方式更快地扩展系统功能、降低风险、缩短产品上市时间、以更低的功耗实现更高的吞吐量,以及快速打造新的产品类别。而戈登·摩尔本人也预言道,“事实可能证明,用较小的分别封装并相互连接的功能构建大型系统更经济。”

图1:我们正迈入“SysMoore”时代

将多个die(或小芯片)放在一个封装下的Multi-Die系统,有诸多优势:

-

以具有成本效益的价格加速扩展系统功能(>2X reticle limits)

-

通过重复使用经过验证的设计/die,降低了风险和上市时间

-

在降低系统功耗的同时提高吞吐量,最高可达30%

-

为灵活的投资组合管理快速创建新的产品变体

那么哪些市场会比较青睐于采用Multi-Die系统呢?据新思科技对采用Multi-Die系统设计的调查,从应用领域来看,服务器/AI占主导地位,网卡/交换机也比较常用,智能手机/图形/PC领域上的采用主要是一些专用芯片,再就是一些光电共封和汽车领域正在向Multi-Die发展;从制程节点来看,5nm工艺采用Multi-Die的比例最大,再就是7nm和3nm。

随着2.5D、3D这样先进封装技术的进步,Multi-Die系统的实现也越来越成为可能。目前业内已有多个Multi-Die的商业实例,不仅仅是传统的芯片制造商在向Multi-Die发展,超大规模数据中心厂商、自动驾驶汽车厂商、网络公司等也都在设计自己的芯片,并以多种方式推动Multi-Die架构的转变,譬如AMD 的3D V-Cache、苹果的M2、英特尔Meteor Lake处理器、索尼的CIS、Lightmatter、特斯拉等。这些厂商对性能、安全和可靠性有着特殊的要求,Multi-Die则可以满足他们在特定领域下的这些需求。

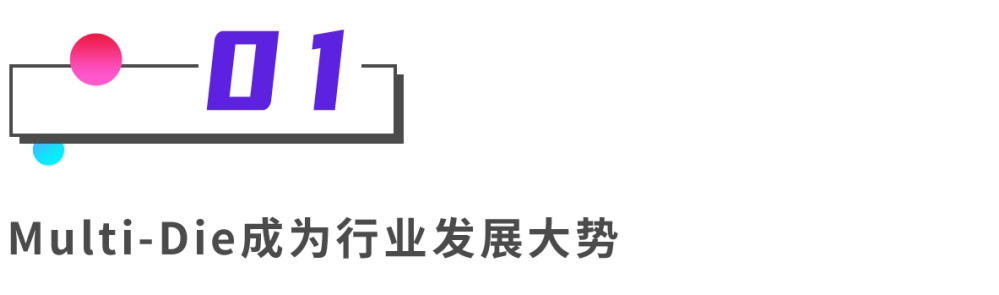

但是从单片SoC到Multi-Die系统的迁移也不是易事。从单片SoC向Multi-Die系统迁移带来了必须从整体上解决的独特挑战:例如异构系统集成、功耗和热管理、系统设计规划、Die-to-Die连接、软件开发和建模、系统验证能力/性能、系统签核分析、分层测试和修复、可靠性和安全性、系统良率、内存利用率和一致性等等。在做每一个选择和决定时,都应考虑到方方面面及其对设计总体PPA目标的影响。

图2:从单片SoC迁移到Multi-Die系统过程中的诸多挑战

所以此时就需要EDA和IP产品的介入,来帮助客户从系统规划到实现和固件/硬件/软件联合开发,助力Multi-Die系统更好的实现。

那么,要设计Multi-Die系统,从整个系统的角度来看,有哪些重要的步骤和需要考量的点呢?

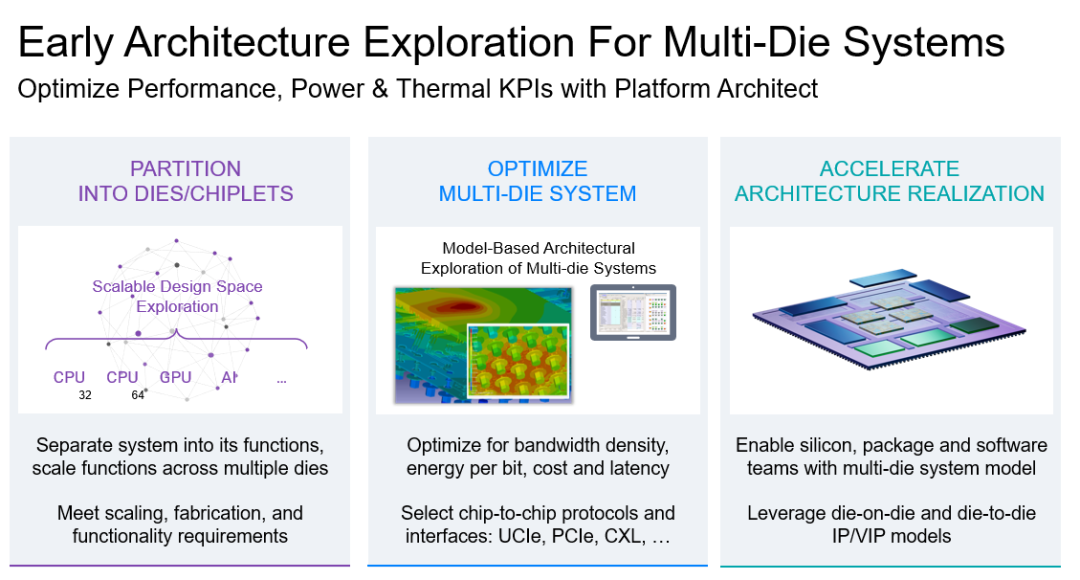

首先,在设计之初时,即在早期架构探索阶段,必须采取分析驱动法来考虑各项宏观架构决策,如IP选择、硬件/软件分解、系统级功耗分析和互连/存储尺寸标注。此外,还要考虑与聚合(利用多个裸片组装系统)和分解(将应用分解到多个裸片上)相关的Multi-Die宏观架构决策。

围绕几个关键领域做出的早期架构决策可以从以下方面改进设计过程:一是将系统分成多个裸片,并且要满足扩展、制造和功能的需求;二是需要优化Multi-Die系统,包括优化带宽密度、每比特的能量、成本和延迟,选择芯片的的协议和接口,如UCIe等;最后是使用Multi-Die系统模型,评估不同制造和封装技术对性能的影响,加速架构的实现。

图3:对Multi-Die进行早期架构探索

架构探索做完之后,另一大重要的挑战是散热问题。Multi-Die系统将多个组件集成在一起,密集的晶体管密度产生大量的热量,尤其是Multi-Die System的架构设计几乎没有什么散热的空间,如果热量散不出去,芯片的功能可能会受到机械应力或翘曲的影响。所以就需要进行热分析,对整个系统进行功率分析、电源完整性、电热vwin 、力学分析,来满足功耗和散热关键性能指标。

另外很重要的一点是,Multi-Die系统还需要一种统一的方法来进行die和封装的协同设计,包括设计、分析和signoff,以加速这些系统的设计闭环。

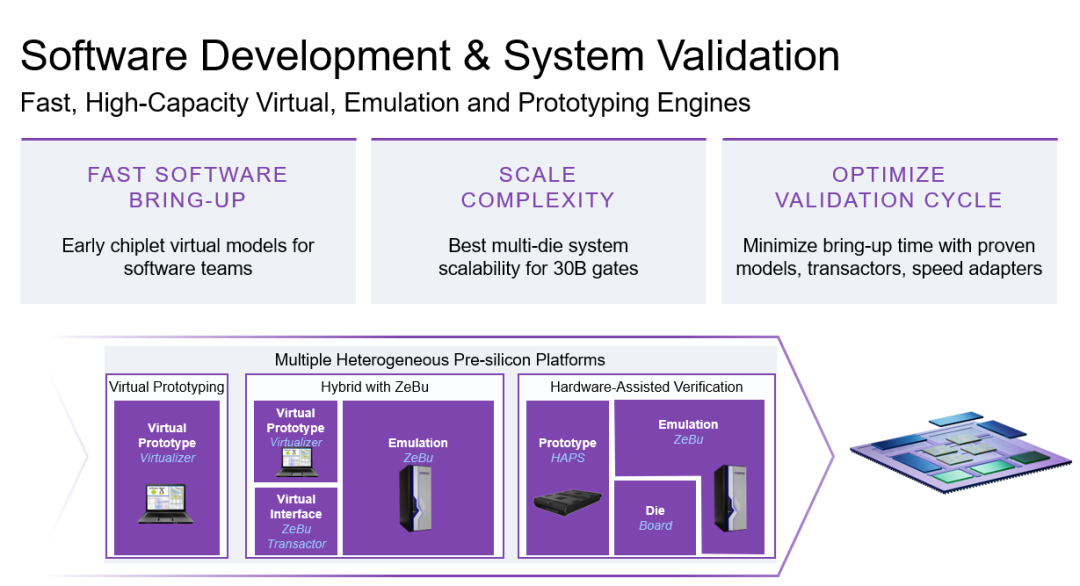

同时,考虑到如此复杂的系统所运行的软件也相当复杂,必须尽早开始验证过程,因此需要创建多模系统的虚拟原型来支持软件开发。Multi-Die系统软件开发和系统验证,需要进行一些关键的考虑和解决方法。多抽象系统建模可以利用快速、可伸缩的执行平台,这些平台使用虚拟原型、仿真、混合仿真和原型。一般而言,300亿的门是Multi-Die最佳的扩展系统。通过使用经过验证的模型、处理程序、速度适配器,优化软件的验证周期,包括die-to-die接口的验证、Multi-Die系统验证,以此来将启动时间最小化。

图4:软件开发和系统验证的一些考量和解决方法

值得一提的是,目前工具流程中的自动化已经提高架构探索效率,超越了过去几年基于电子表格的手动预测。展望未来,统一的设计空间探索将进一步提高这个过程的准确性和效率。

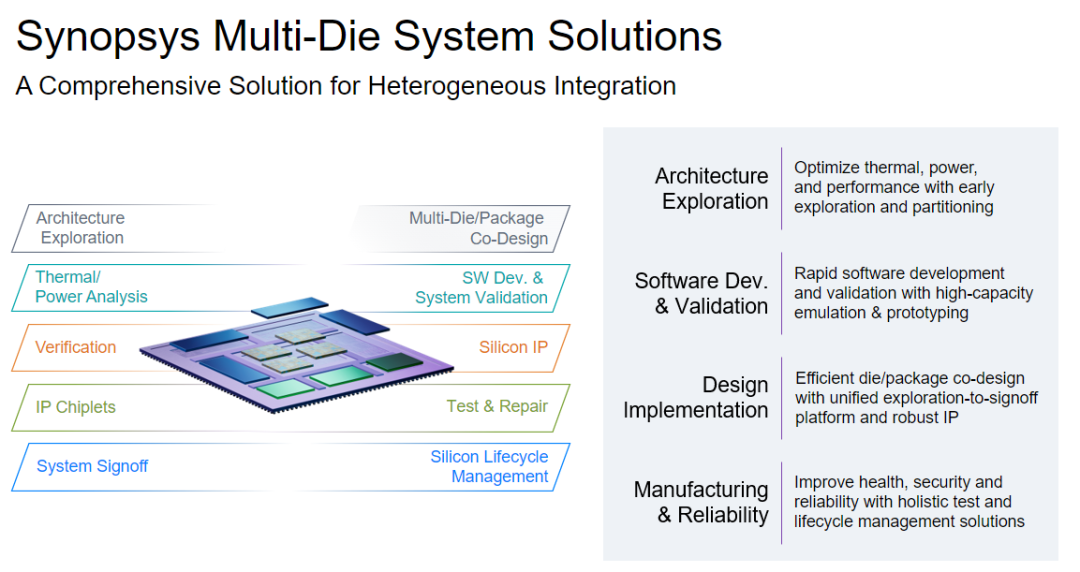

由此可以看出,Multi-Die系统的实现需要理解上述所有设计过程之间的相互依赖性。对此,新思科技提供了业界较全面、具有可扩展的Multi-Die解决方案,为Multi-Die的成功实现提供了更快的路径。该解决方案包含全面的EDA工具和IP,不仅支持早期架构探索、快速的软件开发和验证、高效的裸片/封装协同设计,以及稳健和安全的die-to-die连接,而且还能改进芯片的健康状况和可靠性。久经生产考验的设计引擎以及黄金签核和验证技术能够更大限度地降低风险,并加速打造出色的系统。(如下图5所示)。

图5:新思科技Multi-Die系统解决方案

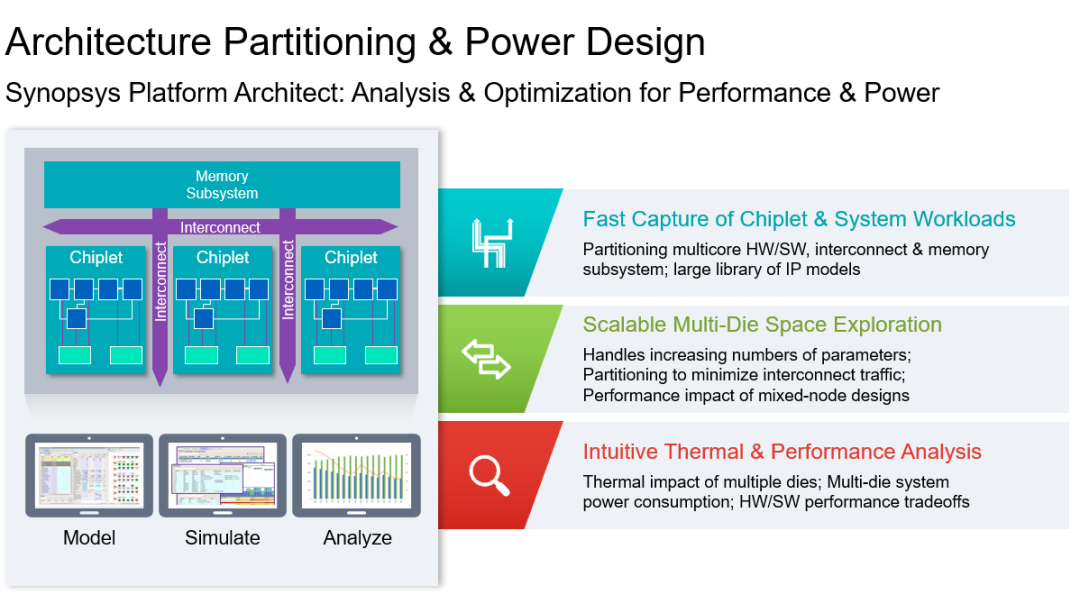

具体来看,在早期架构探索方面,新思科技的Platform Architect为架构师和系统设计师提供了一个基于SystemC事务级模型(TLM)的工具和高效方法,可以用于早期分析和优化多核 SoC 架构的性能和功耗。Platform Architect使开发者能够探索和优化SoC基础设施的硬件—软件分区和配置,特别是全局互连和内存子系统,以实现合适的系统性能、功耗和成本。

图6:新思科技的Platform Architect工作示意图

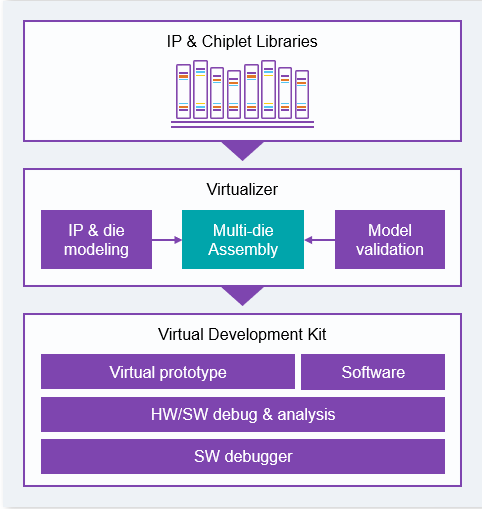

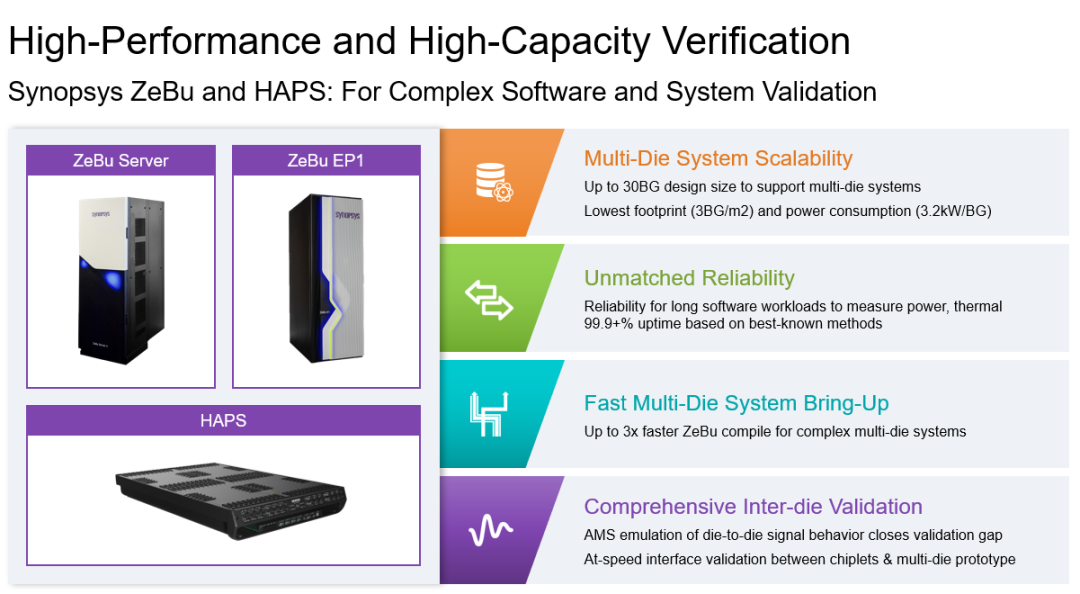

在软件开发方面,新思科技的Virtualizer可以加速Multi-Die系统虚拟原型的开发和部署,Virtualizer解决方案能提供更高的生产力,使开发者能够以最快的速度获得高质量的软件(如图7所示)。在系统验证仿真方面,新思科技的ZeBu和HAPS则可以用于复杂软件和系统验证(图8)。其中,新思科技ZeBuEP1是业界首个统一仿真和原型设计系统,它能使用户可以在整个芯片开发生命周期中利用这个单一验证硬件系统。HAPS-100能允许设计人员、软件开发人员和验证工程师通过HAPS Gateway管理multi-design、多用户部署,以实现最大的生产力和成本效率。

图7

图8

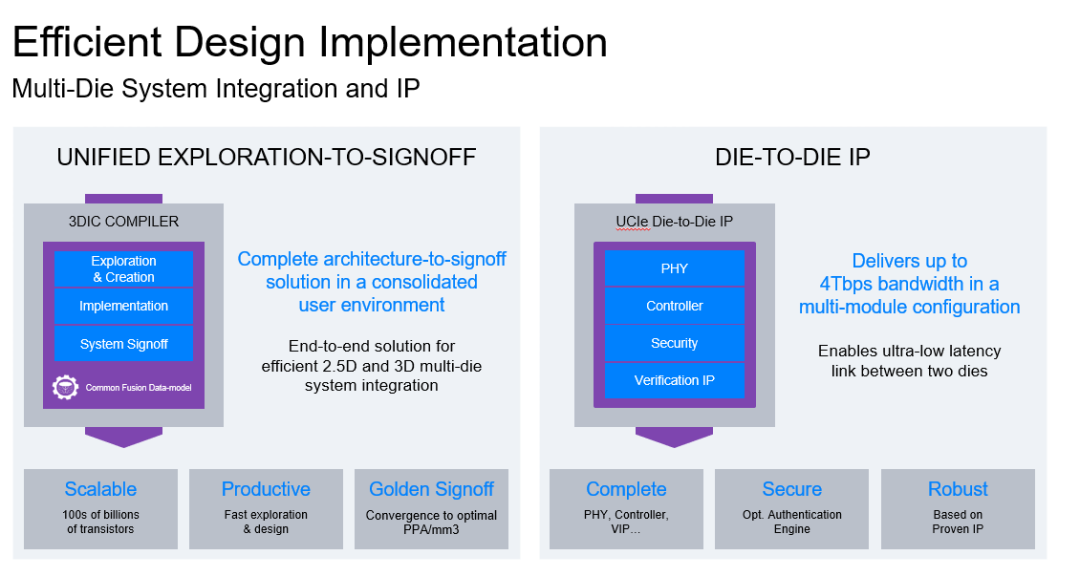

在Multi-Die系统设计实现上,新思科技3DIC Compiler平台是一个完整的端到端解决方案,它结合了许多变革的、Multi-Die设计功能,提供了一个完整的从架构到签核的平台,可实现高效的2.5D和3D Multi-Die系统集成,其内部的黄金signoff工具可以保证每个参数都能准确、完整和方便地signoff。

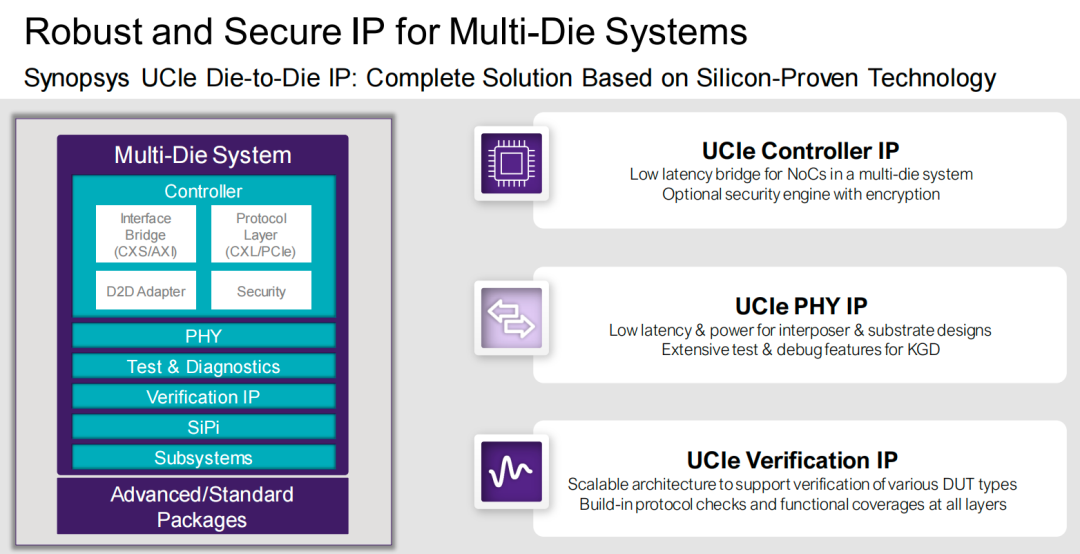

除此之外,新思科技还可以提供一系列经过硅验证的可靠和安全IP,包括用于高带宽、低延迟的die-to-die连接的UCIe、用于高带宽、低功耗内存的HBM和用于防止篡改和物理攻击的安全接口等等。

图9:新思科技可以提供一系列经过硅验证的UCIe IP

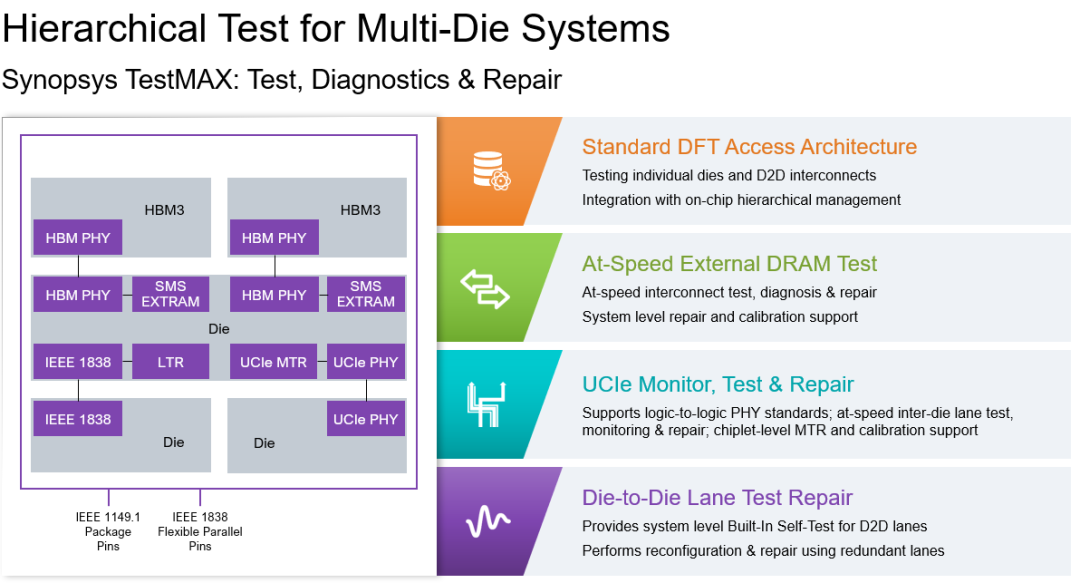

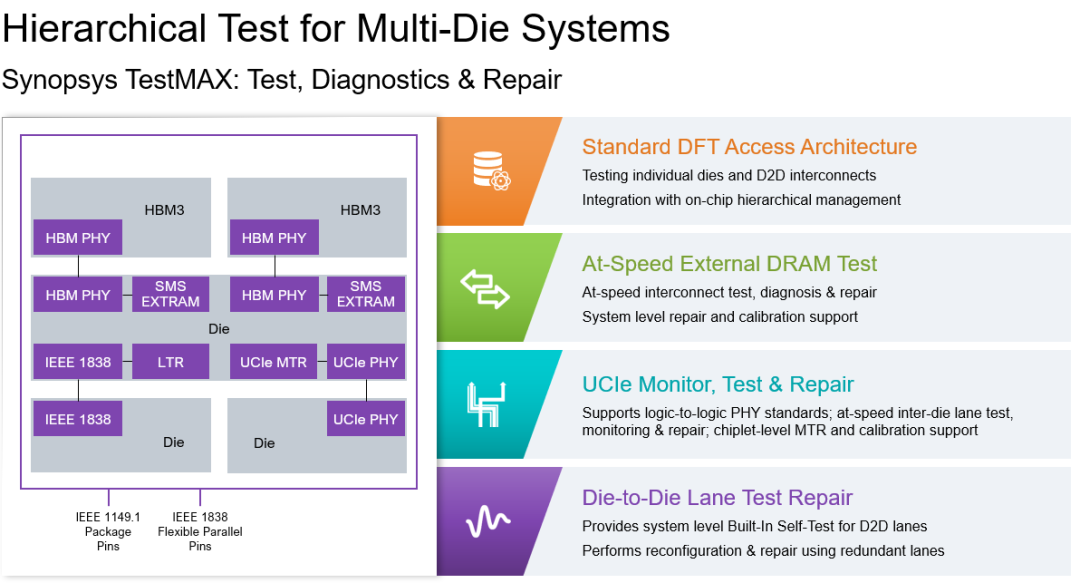

为了确保最终制造的良率和产品的可靠性,需要对产品质量进行测试,包括对Multi-Die系统中的各个裸片、内存、互联以及整个系统进行全面的测试、调试、维修,特别是像3DIC这样的多系统设计提出了独特的测试挑战,IEEE Std 1838-2019就是3DIC一个必须要满足的标准。最终保证已知合格裸片(KGD)、封装和系统的可用性。

图10:需要对产品质量进行测试,对芯片全生命周期进行管理

在测试方面,新思科技的TestMAX系列可以为半导体设备的所有数字、存储和模拟部分提供创新的测试和诊断功能。通过完整的RTL集成支持复杂可测性设计(DFT) 逻辑的早期验证,同时通过与新思科技Fusion Design Platform的直接链接保持物理、时序和功耗感知。这些新功能,再结合对早期可测试性分析和规划、分层ATPG压缩、物理感知诊断、逻辑 BIST、内存自测试和修复以及模拟故障模拟的全面支持。

图11:新思科技的TestMAX 系列

另一方面可以通过芯片全生命周期管理(SLM)技术进行评估,SLM将监视器集成到设计的组件中,以便在设备的整个生命周期中提取数据,甚至在设备在现场的时候。从硅到系统收集到的深入的、可操作的见解允许持续的分析和优化。对于Multi-Die这一体系结构,重点将放在系统上,因此监控基础设施应该跨多个系统,在这方面,新思科技的SLM系列产品改进了设备生命周期每个阶段的操作指标,该系列有一整套集成工具、IP和方法,在系统的整个生命周期内智能高效地收集和存储监控数据,并通过使用强大的分析提供可操作的见解。

图12:新思科技的芯片生命周期管理产品(SLM)系列

Multi-Die系统的出现为电子行业指明了一个新的发展方向,人工智能、超大规模数据中心、网络,手机和汽车等技术正在改变硅行业的格局,将Multi-Die设计推向前沿。但是我们需要明确的是,Multi-Die系统也面临着重大的设计挑战,整个行业需要共同努力,一起推动芯片的创新。

-

新思科技

+关注

关注

5文章

796浏览量

50334

原文标题:爱“拼”才会赢:Multi-Die如何引领后摩尔时代的创新?

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

新思科技Multi-Die系统如何满足现代计算需求

后摩尔定律时代,提升集成芯片系统化能力的有效途径有哪些?

回顾:奇异摩尔@ ISCAS 2024 :聚焦互联技术与创新实践

摩尔斯微电子荣获2024年WBA行业大奖最佳Wi-Fi创新奖等多项殊荣

南京国高电气备自投 —— 技术创新引领电力切换新时代

半导体行业回暖,万年芯深耕高端封装

智驭未来,AI拼才会赢—郑弘孟董事长寄语工业富联,拼搏共赢新篇章

新思科技面向英特尔代工推出可量产的多裸晶芯片设计参考流程,加速芯片创新

“自我实现的预言”摩尔定律,如何继续引领创新

新思科技针对主要代工厂提供丰富多样的UCIe IP解决方案

半导体发展的四个时代

引领科技革命与产业变革,加速新质生产力发展

高精度纳米级压电位移平台“PIEZOCONCEPT”!

爱“拼”才会赢:Multi-Die如何引领后摩尔时代的创新?

爱“拼”才会赢:Multi-Die如何引领后摩尔时代的创新?

评论