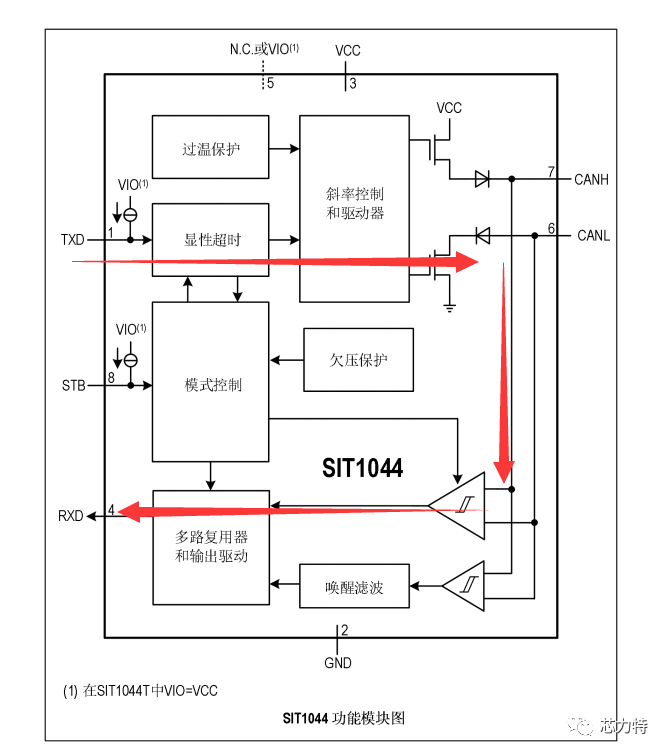

芯力特自主研发的SIT1044芯片是一款应用于CAN协议控制器和物理总线之间的高性能CAN FD收发器芯片,可应用于卡车、公交、小汽车、工业控制等领域,总线耐压达到±40V,支持5Mbps CAN FD灵活数据速率,具有在总线与CAN协议控制器之间进行差分信号传输的能力。

环路延时是指从TXD输入的数字信号被转换成相应的vwin 总线信号,同时总线收发器监控总线,将模拟总线信号转换成相应的数字信号从RXD输出的过程,如下图所示:

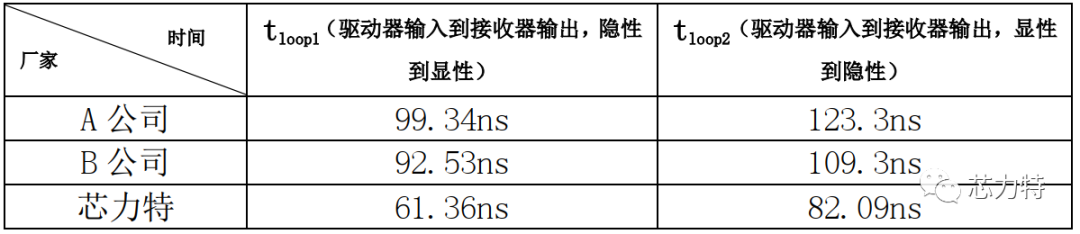

对比目前市面上几家进口公司的同类芯片的环路延时数据,如下表所示:(以下数据在相同环境下测试)

由以上实测测试数据可得知,芯力特公司SIT1044的实测环路延时时间要小于A公司和B公司同类产品。

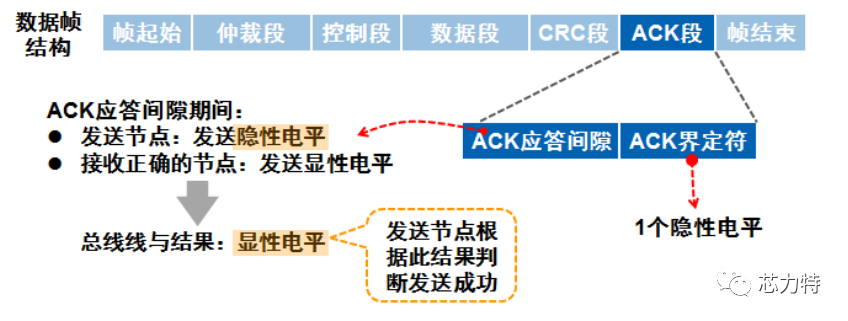

更低的环路延时时间在实际应用时可以使通信距离变长。下面我们以1Mbps波特率下的应用为例,对CAN总线信号延时做简要分析。以标准数据帧为例,从结构上看分成7段,分别为起始段、仲裁段、控制段、数据段、CRC校验段、ACK应答段、帧结束,如下图所示:

ACK段长度为2个位,包含应答间隙(ACK SLOT)和应答界定符(ACK DELIMITER)。在应答场里,发送站发送两个“隐性”位。当接收器正确地接收到有效的报文,接收器就会在应答间隙(ACK SLOT)期间(发送ACK信号)向发送器发送一“显性”的位以示应答。发送节点检测到总线呈显性状态时,就认为有节点进行了有效地应答并且自己所发出的帧是正常的。

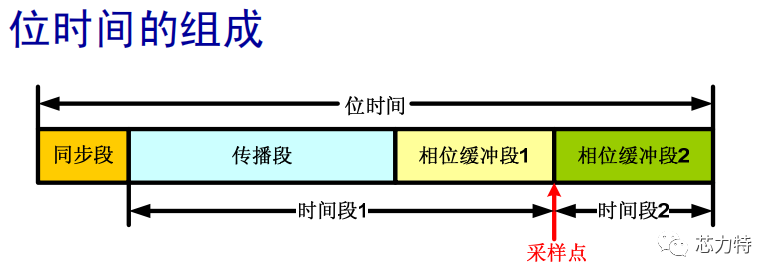

CAN网络通信位定时参数如下图:

CAN总线通信中每一位的时间由4部分组成,即同步段、传播段、相位缓冲段1、相位缓冲段2,划分为3段。

同步段:用于总线诸节点之间的同步;

时间段1:由传播段与相位缓冲段1组成,传播段用于补偿信号的物理传播延时;

时间段2:即相位缓冲段2,相位缓冲段1和相位缓冲段2用于补偿沿的相位误差。

在时间控制器设计中,通过调整时间段1、时间段2的值可以改变对总线传播延时的补偿时间。

发送节点在发完CRC场后,会发出一位应答间隙(ACK SLOT),在这一位的时间内,接收节点应该输出显性位作为回应,发送节点如果在应答间隙内没有检测到有效的显性位,则会判定总线错误,所以限制CAN总线系统信号传播延时上限的根本条件就是必须确保发送节点在应答间隙内接收到有效的应答信号。

为满足这一根本条件,以1Mbit/S,单点采样模式为例,依据采样点在设置同步段、时间段1、时间段2内的前后变化,当设置为75%位宽度时(即采样点位于距位起始的75%位宽度,为750ns),在应答间隙要使得发送节点采集到有效的显性位,理论上来讲,必须满足整个信号传播延时小于750ns。即隔离期间、总线驱动器、线缆等的延时综合小于750ns才能保证应答有效。

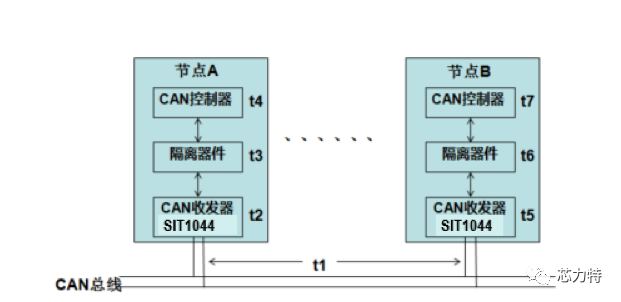

对于CAN网络上节点之间通信的传播延时情况,如下图所示,t2、t5为收发器环路延时,t3、t6为隔离延时(磁耦隔离方式,延时时间在3~5ns)、t4、t7为CAN控制器处理延时(通常情况下,延时在纳秒级以下,可以忽略不计),t1为线缆传输延时。

以节点A发送,节点B接收为例,从CAN报文发出开始,到接收到ACK应答,整个应答回路延时为T总=(t1+t2+t3+t4+t5+t6+t7)*2,期间报文经过了4次隔离及收发器,两次线缆;

由以上公式可知,整个应答回路延时T总=(t1+t2+t3+t4+t5+t6+t7)*2≤750ns,取T总=750ns,假设t3+t4+t6+t7=25ns,则t1+t2+t5=300ns,即t1=300-(t1+t2),所以可以得知t1+t2的值越小,t1的值就越大,在相同线缆材质的情况下,线缆就越长即传输距离更远;故低环路延时的芯力特芯片SIT1044较上述两家进口公司同类芯片更有利于长距离传输。

此外降低应答回路延时时间,可以选择性能较好的CAN FD控制器、使用磁耦隔离收发器以及使用标准线缆,禁止使用电话线、网线等线径较小的线缆,必要时可选择较好材质的导线。

-

芯片

+关注

关注

455文章

50714浏览量

423137 -

收发器

+关注

关注

10文章

3424浏览量

105959

发布评论请先 登录

相关推荐

茂睿芯全系列车规CAN收发器均已实现量产出货

纳芯微CAN收发器NCA1044-Q1获得IBEE/FTZ-Zwickau EMC认证

芯力特发布带振铃抑制功能的CAN收发器——SIT1463Q

IS01044小型封装隔离式CAN FD收发器数据表

TCAN1051具有CAN FD和故障保护功能的CAN收发器数据表

TCAN33x具备CAN FD(灵活数据速率)的3.3V CAN收发器数据表

具有待机模式和故障保护功能的TCAN1044A-Q1和TCAN1044AV-Q1汽车类CAN FD收发器数据表

具有1.8V I/O支持和故障保护功能的TCAN1044V-Q1汽车类CAN FD收发器数据表

TCAN1042具有CAN FD和故障保护功能的CAN收发器数据表

芯力特CAN FD收发器芯片SIT1044低环路延时特性更有利于长距离传输

芯力特CAN FD收发器芯片SIT1044低环路延时特性更有利于长距离传输

评论