本期开发笔记详细为大家介绍基于HPM6750微控制器的硬件电路设计,可以有效提高硬件设计成功率和成熟度,想了解的 “攻城狮“们赶紧上车~

01

简介

本文档的目的是帮助硬件工程师设计和测试基于HPM6750微控制器的硬件电路设计。它提供了关于电路板布局建议和设计清单。

本硬件指南适用于HPM6700/6400系列芯片。同时,可参考对应芯片的数据表、参考手册、以及应用手册。

02

电源配置

2.1电源系统

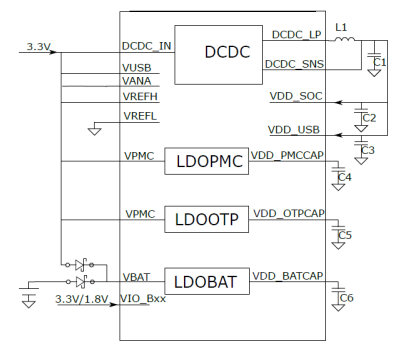

该系列芯片供电是通过对DCDC_IN 和VPMC 脚输入3.0-3.6V单一电源, 并通过内置的电压调节器提供系统所需的VDD_SOC, VDD_PMCCAP, VDD_OTPCAP, V_BATCAP 电源。

当电源DCDC_IN 和VPMC 掉电后,通过VBAT 脚为实时时钟(RTC) 和备份寄存器提供电源。每个I/O 电源VIO_Bxx 根据相应负载接3.3V 或1.8V电源。电源控制图如图1,适用于HPM6700/6400芯片。若无另行说明,所有电压都以VSS 为基准,VSS接地。 图1电源控制图电源域信号电平和去耦电容的建议,请分别参见表 1和表 2 。

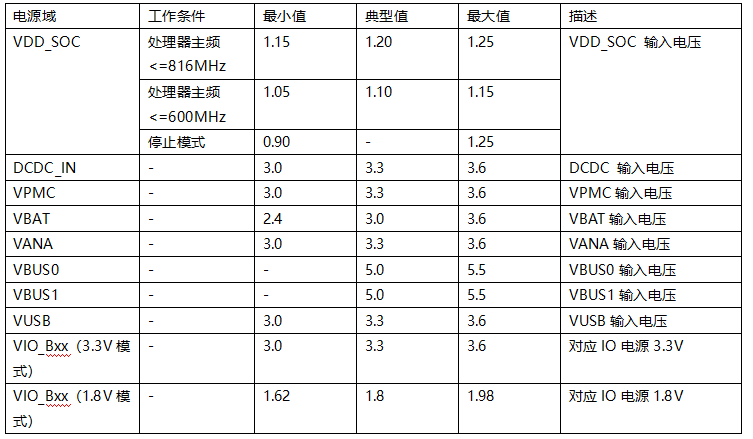

图1电源控制图电源域信号电平和去耦电容的建议,请分别参见表 1和表 2 。 表1 电源域

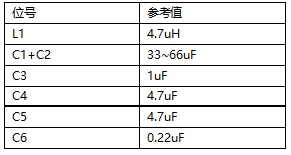

表1 电源域 表2 去耦电容推荐值

表2 去耦电容推荐值

2.2 提升A/D 转换器性能以及参考电压的特别要求

为了提高转换精度, ADC 电路配有独立电源入口,可以由外围电路做电源滤波以减小 PCB 上的噪声,对于需要高精度采样的场合,可以配合高精度的参考电压源实现高精度的AD采样。•一个独立的 VANA 引脚给 ADC 供电。建议使用低噪音LDO供电。•VSS引脚提供了独立的电源接地连接。•VREFH/VREFL为芯片提供高精度低温飘的外部参考电压,例如REF431, 可以提升ADC的采样精度。VREFH上的电压范围为2.4 V 到 3.6V。VREFH/VREFL需要在Pin 附近增加去耦电容,通常采用10nF。

(此处剧透:先楫会推出AD采样精度报告,想了解更多,请关注后期推送)

2.3上电时序

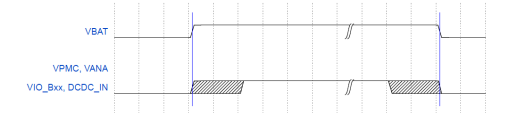

上电时序要求:要求VBAT 不晚于其他电源上电。如果VBAT 和其他3.3V 电源引脚使用相同的供电,则系统对上电时序没有要求。掉电时序要求:VBAT 电源不能早于其他电源掉电。 图2电源时序

图2电源时序

03

3.1晶振/陶振

谐振器和负载电容必须尽可能地靠近振荡器的引脚,以尽量减小输出失真和起振时间。

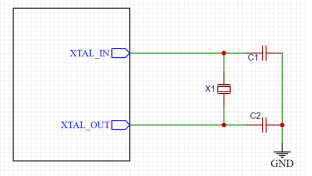

负载电容值必须根据所选振荡器的不同做适当调整。对于 C1 和 C2,建议使用专为高频应用设计、可满足晶振或谐振器的要求且大小介于5pF 到 25 pF(典型值)之间的高质量陶瓷电容。 图3外部晶振/陶瓷谐振

图3外部晶振/陶瓷谐振

C1和C2 的大小通常相同。晶振制造商指定的负载电容通常是 C1 和 C2 的串联组合。确定 CL1 和 CL2 的规格时,必须将 PCB和 MCU 引脚的电容考虑在内 (引脚与电路板的电容可粗略地估算为 10 pF)。

04

调试

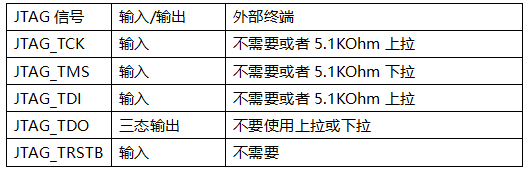

HPM6700/6400系列产品的调试系统符合The RISC-V Debug Specification, Version 0.13 规范。调试系统包括JTAG 接口转换模块(DTM)和调试模块(DM)2 部分。DTM 通过标准JTAG 接口对接外部调试器,可以把JTAG 上收到的调试指令转换成对DM 模块的读写访问。调试模块DM 集成了调试功能,可以暂停或者恢复CPU 的运行,产生复位,以及访问片上资源。表3 JTAG接口

以上为本期分享内容,请继续关注,下期会推出下一篇续集,敬请留意!

-

电路设计

+关注

关注

6673文章

2451浏览量

204125

发布评论请先 登录

相关推荐

HPM6750evkmini如何实现可信的执行环境?

OC6700-规格书

HPM SDK 1.6.0 FreeRTOS LTS更改及适配指南

国产高性能MCU又一力作,集成授权EtherCAT,助力工业伺服走向海内外

先楫HPM6E00新品上市在即

开发者分享 | 基于先楫RT-Thread BSP,使用CLion开发应用

HPM USB系列:HPM6700双USB功能介绍

HPM USB系列:HPM6700双USB功能介绍

干货分享 | HPM6700系列硬件设计指南 (上)

干货分享 | HPM6700系列硬件设计指南 (上)

评论