NSD1624是纳芯微最新推出的非隔离高压半桥驱动芯片,驱动电流高达+4/-6A,可用于驱动MOSFET/IGBT等各种功率器件。

可广泛应用于

•光伏、储能等新能源领域

•半桥、全桥、LLC电源拓扑

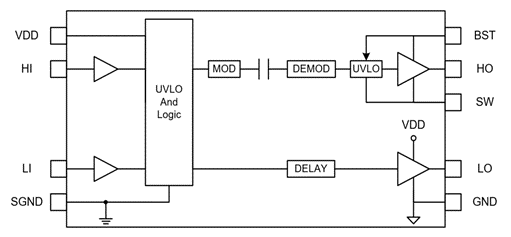

如下图NSD1624功能框图所示,纳芯微创新地将隔离技术方案应用于高压半桥驱动中,使得高压输出侧可以承受高达1200V的直流电压,同时SW pin可以满足高dv/dt和耐负压尖峰的需求。可适用于各种高压半桥、全桥、LLC电源拓扑上。

NSD1624输入逻辑可兼容TTL/CMOS,方便控制。高压侧和低压侧均具备独立的供电欠压保护功能(UVLO),能在10~20V电压范围内工作。此外,NSD1624可提供SOP14,SOP8,LGA 4*4mm多种封装形式。

NSD1624功能框图

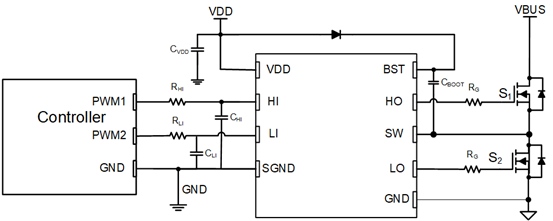

NSD1624简化应用电路

解决高压、高频系统中SW pin负压和高dv/dt的痛点

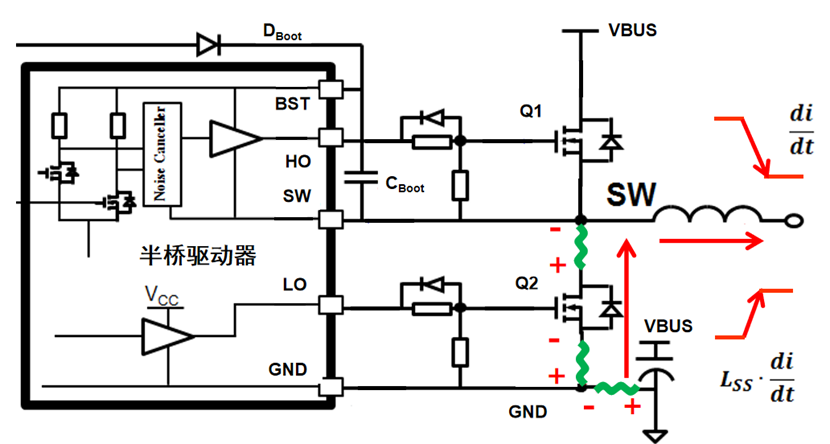

图一:半桥驱动IC典型应用电路图示

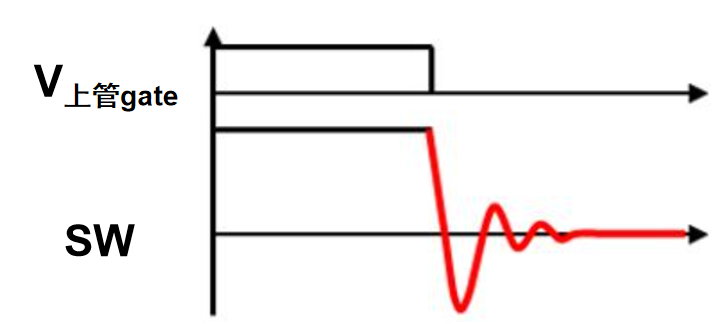

图二:Q1、Q2管子开关过程中,SW产生震荡和负压

上图一所示是半桥驱动IC非常典型的应用电路。在Q1、Q2管子开关过程中,SW 会产生一定程度的震荡,同时会有负压产生,如上图二所示。如果驱动IC SW pin 耐负压能力比较低,就会导致IC损坏。

SW pin 产生震荡和负压的原因是:当上管关闭时,由于负载呈感性,电流不能突变,电流便会从GND 通过下管的体二极管进行续流,如图一的红色箭头方向所示。在真实电路中,该电流路径上许多地方会存在寄生电感,如图一的绿色电感。

SW 的电压 Usw=-Lss * (di/dt),通过公式可以看出,续流电流通过路径中的寄生电感,会在SW上产生负压。如果负载电流越大,开关频率越高,即di/dt 大,同时电路中寄生电感越大,即Lss 值越大,则SW产生的震荡和负压就会越大,就会越容易损坏驱动IC。

此外,开关频率越大,SW产生的dv/dt就越大。如果选择的驱动IC dv/dt 抗干扰能力不足,便会导致驱动IC内部逻辑错误,可能会使得驱动IC的HO 和 LO同时输出高电平,使得上下管同时打开,造成短路,甚至烧坏管子。

纳芯微创新地将隔离技术方案应用于NSD1624 高压半桥IC中,很好解决了上述问题,即:SW pin负压和高dv/dt的痛点。该创新技术,使得NSD1624 SW pin 电压能够承受高达±1200V,可以承受非常高的负压;同时dV/dt抗干扰能力超过100kv/us。因而 NSD1624 非常适合高频、高压、高可靠性的应用场景,符合电源行业发展的趋势。

产品特性

•高压侧电压范围:1200V (SOP14封装);700V (SOP8 / LGA10 封装)

•SW pin耐压:±1200V (SOP14封装);±700V (SOP8 / LGA10 封装)

•高压侧dV/dt抗干扰能力:100kv/us

•驱动电流能力:+4/-6A

•VDD最大耐压值:24V

•两通道都具备欠压保护

•典型传播延时:22ns

•最大延时匹配:7ns

•工作环境温度:-40℃ ~ 125℃

•符合 RoHS 标准的封装类型:SOP8/SOP14/LGA10

-

驱动芯片

+关注

关注

13文章

1277浏览量

54586

发布评论请先 登录

相关推荐

纳芯微提供全场景GaN驱动IC解决方案

供应SW1108P集成氮化镓直驱的高频准谐振IC

负压传感器芯片安装与使用指南

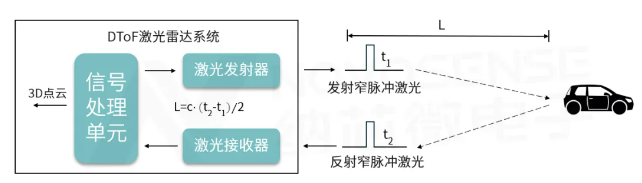

GaN HEMT驱动芯片NSD2017助力解决激光雷达应用挑战

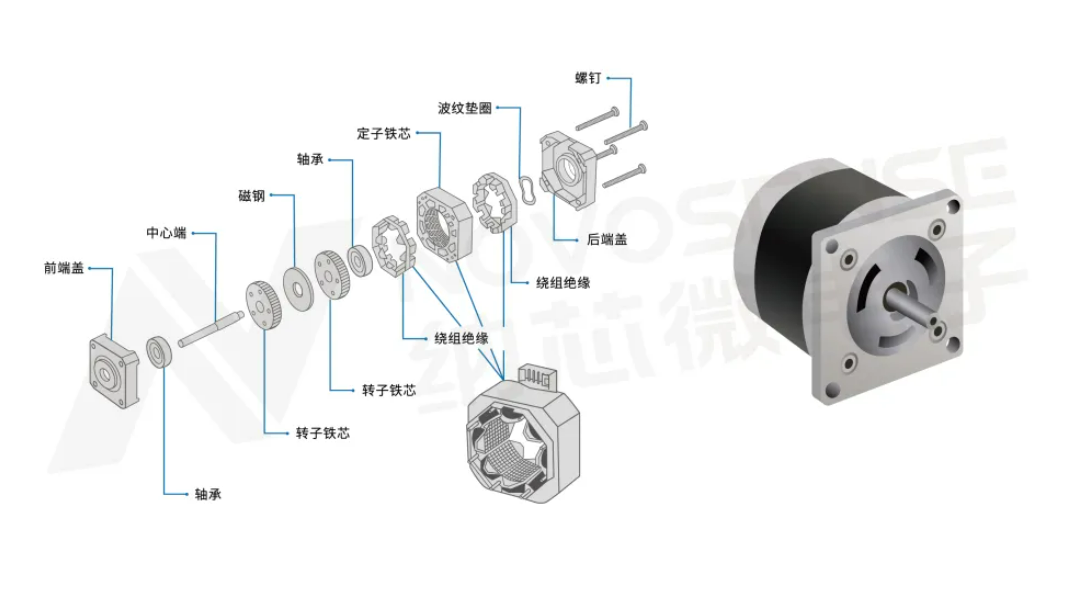

AMEYA360:纳芯微高集成单芯片SoC如何高效智能控制车载步进电机?

纳芯微GaN HEMT驱动芯片NSD2017在激光雷达中的优势

Buck电路EMI高风险区域揭秘

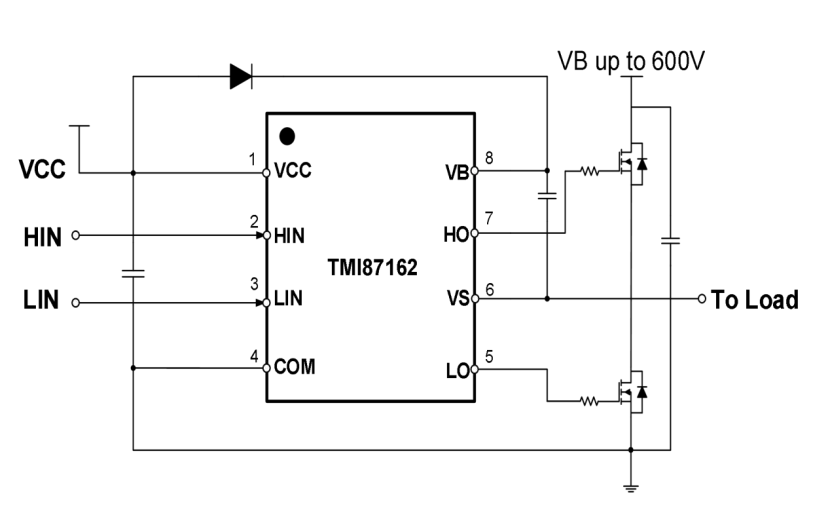

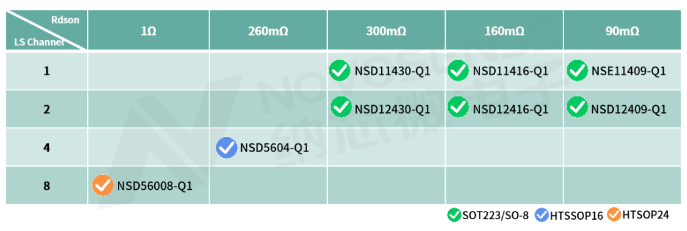

纳芯微8通道1Ω车载低边驱动全新发布!支持负载开路诊断功能!

纳芯微驱动芯片NSD1624,有效解决高压、高频系统中SW pin负压和高dv/dt!

纳芯微驱动芯片NSD1624,有效解决高压、高频系统中SW pin负压和高dv/dt!

评论