小芯片为工程师们提供了半导体领域的新机遇,但当前的键合技术带来了许多挑战。现在,IBM 和 ASMPT 之间的一家合资企业已经开发出一种用于封装芯片的新型混合键合技术,可以在原子尺度上直接键合芯片,从而减小触点尺寸。

chiplet 面临哪些挑战,合资企业开发了什么,这将如何帮助加速未来的 chiplet 设计?

小芯片面临哪些挑战?

随着半导体制造商努力缩小单个晶体管的尺寸,研究人员也在不断寻找提高现代设备性能的新方法。虽然一种选择是使通用处理器更强大(具有更快的计算速度和更大的内存大小),但另一种选择是识别资源密集型的特定任务并创建专用硬件加速器。这种硬件加速器的使用已经得到广泛使用,例如处理图形例程的 GPU、针对神经网络优化的 AI 加速器,以及允许在不影响性能的情况下进行即时加密的加密加速器。

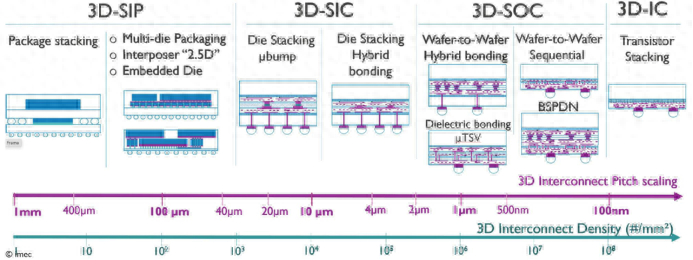

然而,对于加速器提供的所有好处,将加速器放置在芯片外部会对数据带宽产生巨大影响,但尝试将加速器集成到单个单片半导体中会减少可用于其他硬件(例如处理器内核和内存)的总面积。为了解决这一挑战,工程师们正在转向小芯片,即具有特定用途的小型独立半导体芯片,并将这些小芯片连接在一起以创建封装模块。

这不仅让工程师能够充分利用任何一个裸片上的硅空间,而且还允许定制,小芯片可以换成不同的设备,从而实现 SoC 的完全定制。但是,尽管小芯片带来了所有优势,但工程师们正在努力应对一个主要缺点:芯片互连。

在 IBM Research 最近的一篇博客文章中,他们深入探讨了小芯片的概念以及它们如何帮助克服这些挑战。小芯片本质上是复杂功能芯片的更小的功能块,它可以包括独立的计算处理器、图形单元、AI 加速器和 I/O 功能。通过打破片上系统模型,chiplet 可以带来更节能的系统,缩短系统开发周期,并以比现在更低的成本构建专用计算机。

一种解决方案是将小芯片倒装到类似于 PCB 的基板上,并将裸片焊接到基板上。然而,由于目前焊接技术的限制,芯片上的焊盘尺寸必须大于几十微米,这就限制了互连密度。同时,焊料可能难以控制,导致带宽受限的低质量连接。

IBM 的第二代纳米片技术为在 300 毫米晶圆上生产的 2 纳米节点铺平了道路。这项技术允许在指甲盖大小的空间内安装 500 亿个晶体管。用于 2 纳米芯片节点的纳米片晶体管是对几个较小的里程碑的验证,这些里程碑证明了这是可以做到的,也是 IBM 跨学科专家团队在材料、光刻、集成、设备、表征和建模方面的辛勤工作和奉献精神的验证。

另一种选择是将裸片安装到基板上并在裸片之间使用金线。虽然这通常用于芯片键合,但它是一种昂贵的工艺,可能不适合定制小芯片设计的小批量生产。还有一些实际限制可能会使芯片的键合线变得复杂(因为结束键合线会留下尾巴,尾巴会四处移动并可能导致短路)。

IBM 和 ASMPT 开发了

一种新的小芯片键合技术

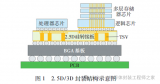

认识到小芯片键合面临的挑战,IBM和ASMPT的研究人员联合开发了一种新的解决方案,可以帮助加速小芯片的部署。这种用于封装芯片的新型混合键合允许芯片在原子尺度上直接键合。

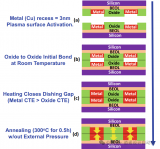

IBM 和 ASMPT 在 chiplet bonding 技术上取得了重大突破。他们开发了一种混合键合技术,可以大大减少两个小芯片之间所需的键合尺寸。这是通过在原子尺度上利用铜和氧化物层来实现的,键本身只有几个原子厚。这一发展可能会彻底改变小芯片的封装方式,并加速小芯片技术的部署。

为了帮助粘合小芯片,该研究机构开发了一种混合技术,该技术在原子尺度上利用铜和氧化物层(粘合本身只有几个原子厚)。然而,为了使粘合起作用,必须去除两个表面之间的所有水分和碎屑,因为即使是几个水分子也足以影响两个触点之间的电气连续性。这也适用于可能在两个表面之间形成的潜在气泡,因为小气泡可以很容易地通过静电力容纳气体分子。

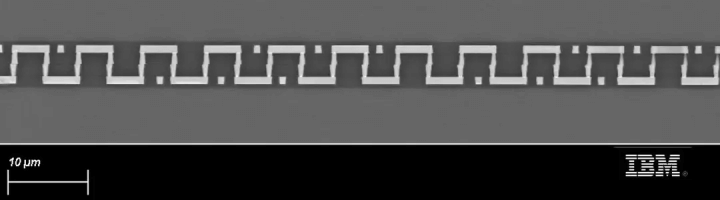

一张图片展示了通过该团队的方法实现的两层之间的微小结合。

IBM 和 ASMPT 开发的混合键合技术改变了半导体行业的游戏规则。通过将两个小芯片之间所需的键合尺寸减小到仅几个原子,该技术可以显着增加两个不同芯片之间的连接密度。这反过来又会导致数据带宽的大幅增加,为半导体产品的设计和性能开辟新的可能性。

据研究人员称,所开发的方法与现有的不同小芯片之间使用的芯片接合方法极为相似,但规模要小得多。此外,该合资企业能够实现与 ASMPT 提供的现有机械的结合,这意味着这项新技术有可能在未来几年内得到部署。

这种贴片技术如何改变未来的技术?

到目前为止,新开发的键合技术提供的最大优势是它显着增加了两个不同芯片之间的连接密度,从而增加了数据带宽。然而,增加连接密度也允许工程师将复杂的设计拆分到多个芯片上,这不仅有助于提高晶圆良率,而且会显着增加设计的尺寸。反过来,这会增加大型半导体产品的晶体管数量,从而导致具有更高处理器和内存容量的指数级更强大的系统。

此外,新的键合技术还有助于加速工程师的半导体定制。虽然仍处于起步阶段,但如果 chiplet 行业与 PCB 行业有任何相似之处,那么用不了多久,工程师就能够以近乎相同的方式设计自己的 SoC,以提供组装服务的定制 PCB。此类服务将允许工程师创建适合其应用的 SoC,为关键任务集成加速器,同时利用低能耗选项来降低功耗。

总体而言,IBM 和 ASMPT 开发的产品令 chiplet 行业兴奋不已。虽然需要做更多的研究来确保键合技术的可靠性和可重复性,但这种用于封装芯片的新型混合键合可能会彻底改变半导体的设计和制造方式。

这种新的混合键合技术的开发证明了IBM和ASMPT的研究人员正在进行的创新工作。这是小芯片技术领域的一个重要里程碑,对未来充满希望。随着这项技术的不断发展,我们可以期待在半导体的设计和制造方式上看到更多激动人心的发展。

IBM 对小芯片的研究已经显示出可喜的成果。他们正在根据行业小芯片标准的两个主要竞争者通用小芯片互连快速 (UCIe) 联盟和开放计算项目的线束规范的方向探索小芯片I/O 的各种设计。IBM 研究人员参与了这两项计划,在潜在的未来小芯片封装解决方案的背景下研究信号映射策略。这种主动方法可确保 IBM 在标准达成一致后立即准备好构建小芯片。

审核编辑:刘清

-

加速器

+关注

关注

2文章

796浏览量

37838 -

SoC芯片

+关注

关注

1文章

610浏览量

34905 -

封装芯片

+关注

关注

0文章

17浏览量

8571 -

chiplet

+关注

关注

6文章

431浏览量

12584

发布评论请先 登录

相关推荐

从发展历史、研究进展和前景预测三个方面对混合键合(HB)技术进行分析

三维堆叠封装新突破:混合键合技术揭秘!

混合键合技术:开启3D芯片封装新篇章

SK海力士将在HBM生产中采用混合键合技术

铜线键合焊接一致性:如何突破技术瓶颈?

Chiplet混合键合难题取得新突破

Chiplet混合键合难题取得新突破

评论