8

存储器

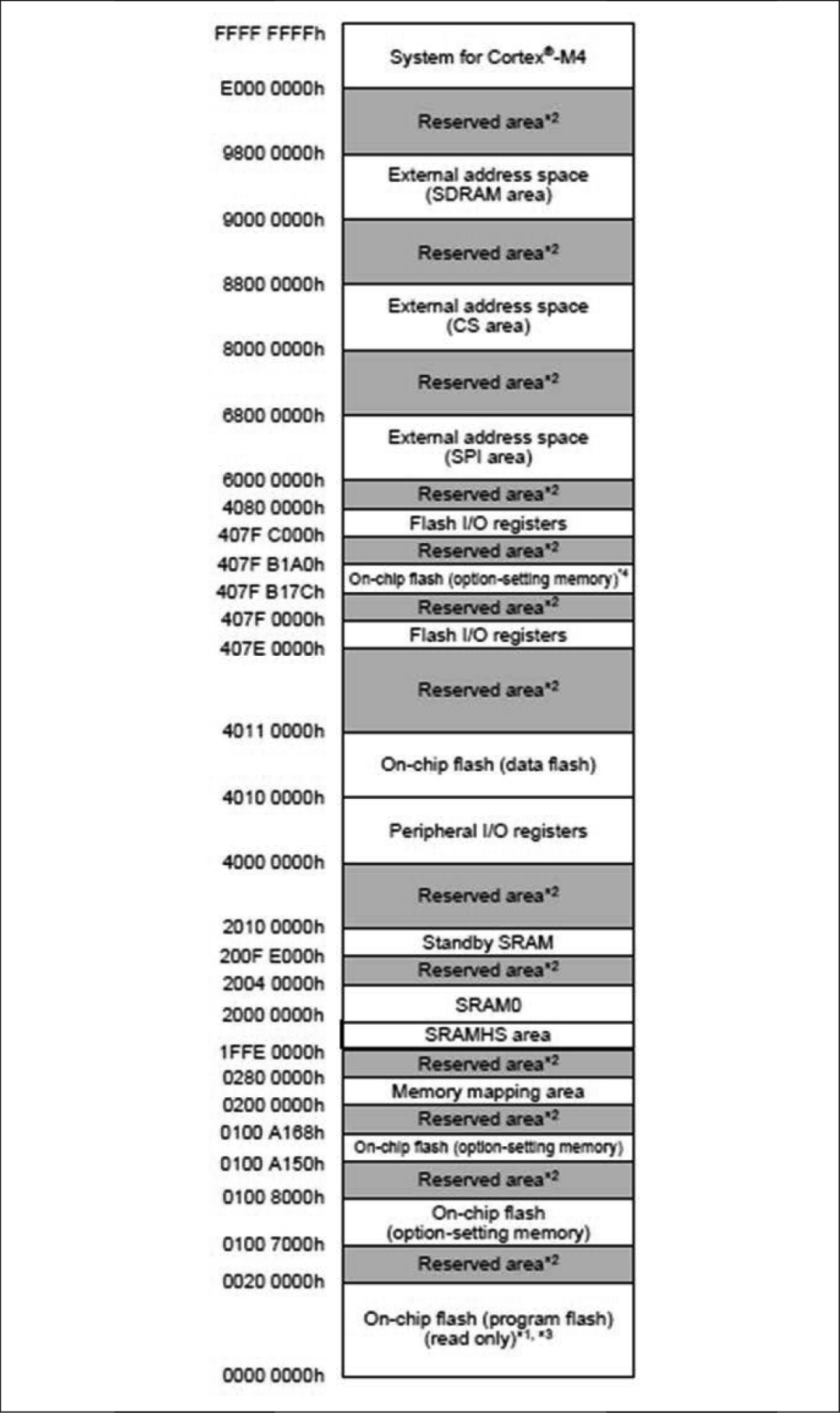

RA6 MCU支持4GB的线性地址空间,范围为0000 0000h到FFFF FFFFh,其中包含程序、数据和外部存储器总线。该系列的某些产品包括一个SDRAM控制器,可利用该控制器访问连接到外部存储器总线的SDRAM器件。程序和数据存储器共用地址空间;使用单独的总线分别访问这两个存储器,从而提高性能并允许在同一个周期访问程序和数据。存储器映射中包含片上RAM、外设I/O寄存器、程序ROM、数据闪存和外部存储器区域。

图16. RA6M3存储器映射

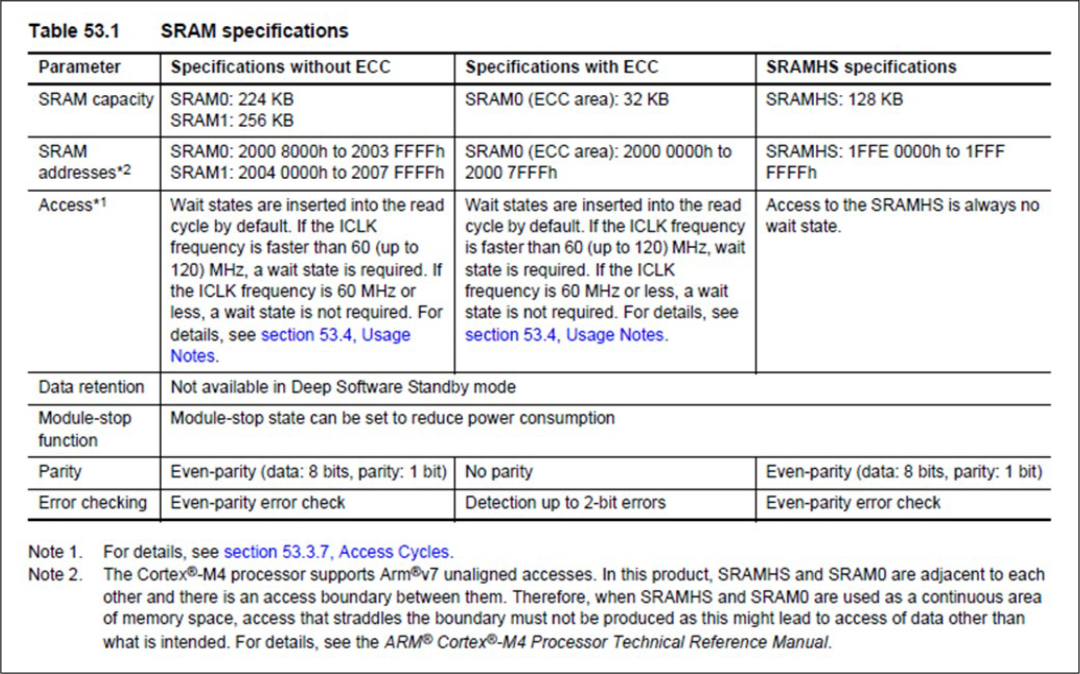

8.1 SRAM

RA6 MCU提供带奇偶校验位或ECC(纠错码)的片上高速SRAM模块。SRAM0的前32KB区域受ECC控制。奇偶校验在其他区域执行。下表列出了SRAM规范。SRAM模块的数量和容量因器件而异。有关详细信息,请参见《硬件用户手册》。

图17. RA6M3 SRAM规范示例

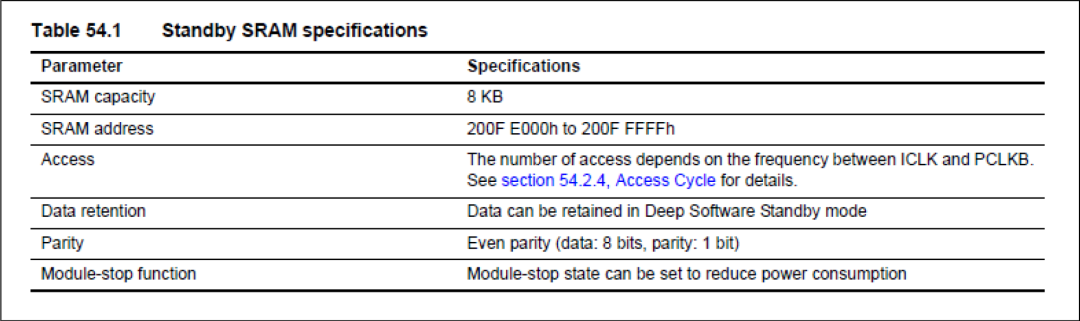

8.2 待机SRAM

RA6 MCU提供了一个片上SRAM,支持在深度软件待机模式下保留数据。下表列出了备用SRAM规范。

在深度软件待机模式下,待机SRAM的电源由DPSBYCR.DEEPCUT[1:0]位使能。如果DPSBYCR.DEEPCUT[1:0]位设置为00b,则将在深度软件待机模式下保留待机SRAM中的数据。有关DPSBYCR.DEEPCUT[1:0]位的详细信息,请参见后文第11节“低功耗模式”。

图18. RA6M3待机SRAM规范示例

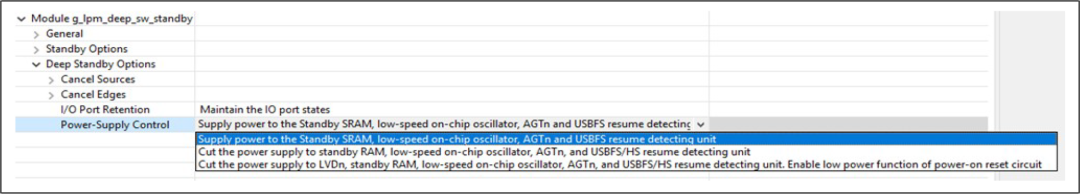

Renesas FSP中的LPM(低功耗模式)驱动程序提供了一个用于切断或保持待机SRAM电源的选项,如下图所示。仍然需要调用LPM驱动程序的API才能将所选设置写入MCU寄存器。

图19. 使用Renesas FSP配置器使能/禁用待机SRAM的电源

8.3 外设I/O寄存器

外设I/O寄存器块出现在存储器映射中的不同位置,具体取决于器件和当前的工作模式。大多数外设I/O寄存器占用的地址范围为4000 0000h到400F FFFFh。但是,位置和大小可能会因器件而异。有关详细信息,请参见《硬件用户手册》。有关详细信息,可参见“I/O寄存器”附录,也可参见每个外设功能的寄存器说明。该区域包含在所有工作模式下始终可用的寄存器。用于控制访问闪存的闪存I/O寄存器占据两个区域,即407E 0000h至407E FFFFh和407F C000h至407F FFFFh。

Renesas FSP包含采用CMSIS数据结构的C语言头文件,这些文件将特定器件的所有外设I/O寄存器映射到易于访问的I/O数据结构。

未完待续

-

mcu

+关注

关注

146文章

16514浏览量

346692 -

瑞萨

+关注

关注

33文章

22268浏览量

85378

原文标题:RA6快速设计指南 [9] 存储器 (1)

文章出处:【微信号:瑞萨MCU小百科,微信公众号:瑞萨MCU小百科】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ram存储器和rom存储器的区别是什么

CK-RA6M5上的RA AWS云连接,带蜂窝网络-入门指南

CK-RA6M5上的RA AWS云连接(带以太网)入门指南

RA6快速设计指南 [9] 存储器 (1)

RA6快速设计指南 [9] 存储器 (1)

![<b class='flag-5'>RA6</b>T2的16位模数转换<b class='flag-5'>器</b>操作 [<b class='flag-5'>9</b>] 配置<b class='flag-5'>RA6</b>T2 ADC模块 (<b class='flag-5'>6</b>)](https://file1.elecfans.com/web2/M00/BB/1B/wKgZomWXtb6ACk_NAAARMuEl9ZA261.png)

![<b class='flag-5'>RA</b>2<b class='flag-5'>快速</b>设计<b class='flag-5'>指南</b> [<b class='flag-5'>9</b>] 一般布线实践与参考资料(完结)](https://file1.elecfans.com/web2/M00/A3/1F/wKgZomUDyFSAT6fEAABMTVrCfpI979.png)

![<b class='flag-5'>RA</b>2<b class='flag-5'>快速</b>设计<b class='flag-5'>指南</b> [7] 模块停止功能,中断控制单元与低功耗](https://file1.elecfans.com/web2/M00/A4/8C/wKgaomUDyOyAOoMAAAI-ZvuSIMY086.jpg)

![<b class='flag-5'>RA</b>2<b class='flag-5'>快速</b>设计<b class='flag-5'>指南</b> [<b class='flag-5'>6</b>] 寄存<b class='flag-5'>器</b>写保护和I/O端口配置](https://file1.elecfans.com/web2/M00/A4/8C/wKgaomUDyRmANKEWAABPNEaw3Rg626.jpg)

![<b class='flag-5'>RA</b>2<b class='flag-5'>快速</b>设计<b class='flag-5'>指南</b> [5] <b class='flag-5'>存储器</b>](https://file1.elecfans.com/web2/M00/A3/21/wKgZomUDyXWAV5qfAAEgG1i2Pgo328.jpg)

![<b class='flag-5'>RA</b>2<b class='flag-5'>快速</b>设计<b class='flag-5'>指南</b> [4] 复位要求和复位电路](https://file1.elecfans.com/web2/M00/A3/21/wKgZomUDyc2AAMHWAAF8yDw8WIc920.jpg)

![<b class='flag-5'>RA</b>2<b class='flag-5'>快速</b>设计<b class='flag-5'>指南</b> [3] 时钟电路](https://file1.elecfans.com/web2/M00/A4/8D/wKgaomUDydmANV-eAAHf1-Z0aUw286.jpg)

评论