`ifndef是SystemVerilog/Verilog中的一种条件编译命令,可以认为其是"if not defined"的缩写,其用法与`ifdef相反,他们主要用来根据其后的宏是否存在于当前编译空间从而进行分支选择,因此在实际的工作过程中,常用来进行"guardagaintcompile"等操作,本文将利用其分支选择的特点介绍`ifndef(`ifdef与其功能类似,不再示例)几种常见用法。

1 避免重复编译

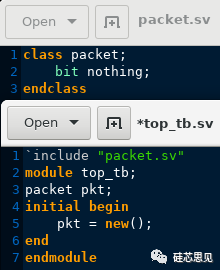

【示例】

【仿真结果】

示例中,在top_tb.sv中include了packet.sv,同时在filelist中包含了packet.sv和top_tb.sv,这样在对filelist进行编译时相当于需要对packet.sv连续编译两次,此时编译到被include的packet.sv报错。这主要是因为同一个文件在编译时被编译了多次,一般情况下多数仿真工具为此都会给出不同类型的提示信息。对于较小的设计重复文件编译一般基本没有影响,但是对于大型设计,这种重复编译会增加编译工作的工作量,影响编译效率,为此一般对于多次共享的一些公共资源都会使用如下示例的方式,避免多次编译影响编译效率。

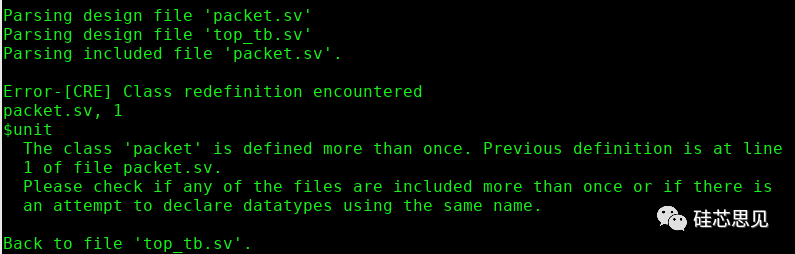

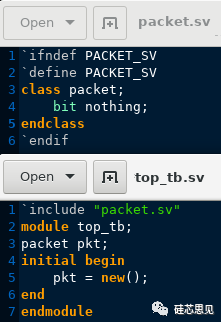

【示例】

示例中,在packet.sv中使用了条件编译结构"`ifndef PACKET_SV ... `endif"。当packet.sv第一次编译时,因为编译空间中还没由PACKET_SV这个宏定义,所以此时会执行其后的"`define PACKET_SV",当执行到top_tb.sv中的"`include "packet.sv""时,因为此时宏PACKET_SV已经存在于当前全局编译空间中,所以此时"`include "packet.sv""中的packet.sv不会被重复编译,从而可以避免同样代码的重复编译。

2被执行代码的选择

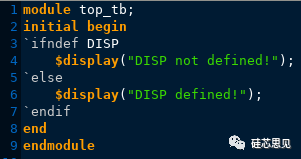

【示例】

示例中,如果编译空间中不存在DISP的宏定义,那么将会执行示例中第4行,如果编译的空间中存在DISP的宏定义,那么将会执行示例中的第6行,即通过"`ifndef ... `endif"实现了根据不同的DISP执行不同的代码段。当然这里之所以可以选择其他分支是因为有"`else"的存在,如果存在多余两个你还可以使用"`ifndef ...`elsif ... `else ... `endif"或者多个"`ifndef ... `endif"嵌套,结构类似于if结构写法,可以根据需要灵活选用。

审核编辑:汤梓红

-

Verilog

+关注

关注

28文章

1351浏览量

110074 -

System

+关注

关注

0文章

165浏览量

36926 -

命令

+关注

关注

5文章

683浏览量

22011 -

编译

+关注

关注

0文章

657浏览量

32851

原文标题:SystemVerilog中ifndef如何避免重复编译

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

SystemVerilog中的类构造函数new

SystemVerilog中的“const”类属性

请问如何理解头文件中的#ifndef?

使用SystemVerilog来简化FPGA中接口的连接方式

STM32头文件中的#ifndef

把头文件的内容放在#ifndef还是#endif中

stm32f429之#ifndef的用法 精选资料推荐

讲讲这个头文件/#ifndef __SYS_H //头件的中的#ifndef

SystemVerilog编码层面提速的若干策略SoC芯片简析

SystemVerilog中的Semaphores

Systemverilog中的Driving Strength讲解

SystemVerilog中ifndef如何避免重复编译

SystemVerilog中ifndef如何避免重复编译

评论