引言

之前在《一文让你理解DC综合全过程!》中,和大家分享了DC映射和优化流程,接下来本文针对如何写DC综合脚本提出五点建议。如果您是DC新手,那么您会发现这几点建议很是实用;如果您是DC老手,由于工具版本的更新,可能增加了您未曾注意的功能,希望本文的分享能对您有所帮助。

一 、使用set_auto_disable_drc_nets命令使时钟网络免于设计规则检查

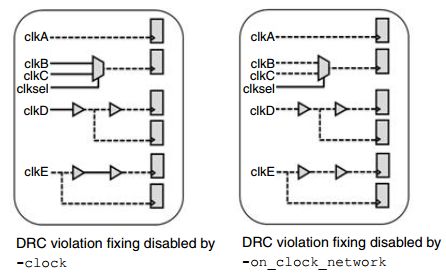

DC会自动通过插入 buffer或者 resizing单元的方式进行设计规则违例修正,不过时钟常值和scan是比较特殊的net,综合人员可以使用set_auto_disable_drc_nets命令来声明不对这些特殊nets进行设计规则违例修正。-default为默认选项,默认情况下时钟和常值是被disable的,不过scan并未disable,可以使用该命令带-all选项,将三者都 disable,或者分别带-on_clock_network、-constant和-scan来分别设置。需要说明的是-clock和-on_clock_network 有些差别,建议使用-on_clock_network,具体差别如图1所示,虚线是被disable的时钟线,-clock保证了对连接到触发器的时钟线,不会进行DRC检查,-on_clock_network是对时钟网络disable DRC,经过组合逻辑再供给到触发的时钟也不会被DRC检查

图 1

二 、使用set_clock_groups命令来约束多时钟设计

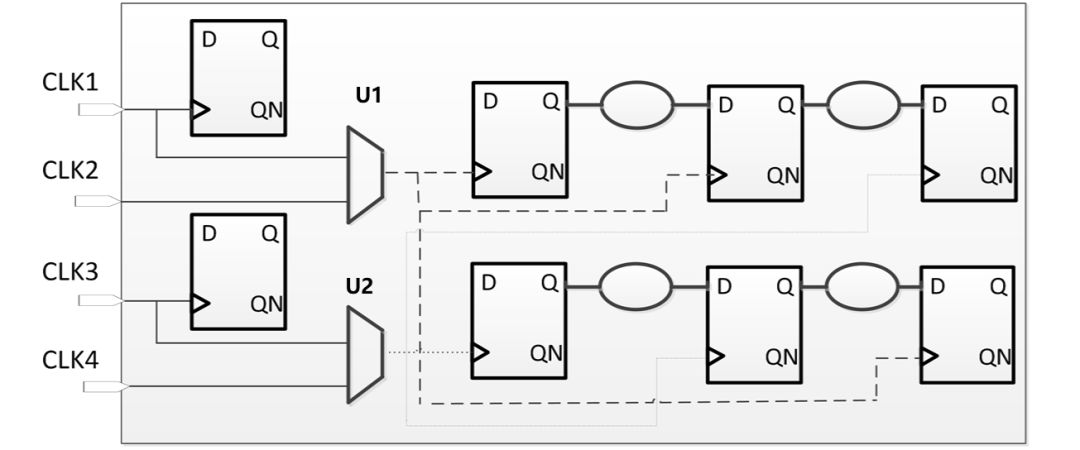

基本所有的多时钟设计中都有时钟切换电路,两个或者多个时钟输入到时钟切换模块,输出被选择的一个时钟。时钟切换电路的电路结构在《你不可不知的——时钟切换电路》中做了详细介绍,需知DC中时钟属性是可以穿过任何组合逻辑的,假设在时钟切换模块前已经用create_clock声明了两个时钟,这两个时钟经过时钟切换模块时穿过的都是组合单元,那么该模块的输出端口也是有两个时钟穿过的。面对这种情况,传统的做法是使用set_case_analysis来做功能选择,比如用于测试的扫描时钟和功能时钟间的切换,这一命令就很有效。但是面对如图2所示的情况,使用set_case_analysis命令,便人为的选定了自认为时序最紧的情况,比如在CLK1和CLK2中选择了频率更高的CLK1,在CLK3和CLK4中选择了频率更高的CLK3,但是可能实际上CLK1到CLK4比CLK1到CLK3时序更紧张。这时,使用如下命令,只告诉DC时钟间的关系,让DC自己分析更稳妥。

方式一:

create_clock -name CLK1 -period 5[get_ports CLK1]

create_clock-name CLK2 -period 10 [get_ports CLK2]

create_clock-name CLK3 -period 15 [get_ports CLK3]

create_clock -nameCLK4 -period 20 [get_ports CLK4]

set_false_path –from [get_clocksCLK1] –to [get_clocks CLK2]

set_false_path–from [get_clocks CLK2] –to [get_clocks CLK1]

set_false_path–from [get_clocks CLK3] –to [get_clocks CLK4]

set_false_path–from [get_clocks CLK4] –to [get_clocks CLK3]

方式二:

create_clock -name CLK1-period 5 [get_ports CLK1]

create_clock-name CLK2 -period 10 [get_ports CLK2]

create_clock-name CLK3 -period 15 [get_ports CLK3]

create_clock -nameCLK4 -period 20 [get_ports CLK4]

set_clock_groups –logically_exclusive–group CLK1 –group CLK2

set_clock_groups–logically_exclusive –group CLK3 –group CLK4

方式一和方式二的作用等价,但显然,使用set_clock_groups命令来描述时钟关系的方式二更简便。其实,除了选项–logically_exclusive,该命令还可以带-phsically_exclusive和-asynchronous选项,这三个选项都可以表述声明的时钟组间的时序路径间是没有约束检查的。不同点在于: 1)-asynchronous选项表示声明的时钟组的组间关系是异步的,异步关系的时钟在芯片正常工作时物理上是可以同时存在的; 2)–logically_exclusive和-phsically_exclusive选项在DC中作用是相同的,–logically_exclusive选项表示的是声明的时钟组的组间关系是逻辑独立、物理可共存的,而-phsically_exclusive选项表示的是声明的时钟组的组间关系是物理独立的,如图2所示,没有信号是跨CLK1传递到CLK2域的,但是CLK1和CLK2是在电路中共存的。这点不同在PT做信号完整性分析时是有影响的,-phsically_exclusive较–logically_exclusive乐观,而-asynchronous最悲观。

图2

另外,set_clock_groups只带一个-group选项的用法也很常见,比如:set_clock_groups–phsically_exclusive –group scan_clk,这表示DFT扫描测试时钟scan_clk与其他所有时钟物理上不共存。其实扫描时钟和功能时钟的关系也是异步的,而使用-asynchronous选项对PT的影响要比实际悲观,故而对于既是物理互斥也是异步的情况,应使用选项-phsically_exclusive。事实上,图2示例的时钟数目少、电路结构简单,而实际电路中时钟选择和电路结构复杂的多,这时候使用命令set_clock_groups描述时钟关系,优势更为明显。事实上,扫描模式与功能模式不同时存在,且时钟频率差距甚大,扫描时钟与功能时钟的切换使用命令 set case analysis足以。

对图2进一步分析,时钟切换电路U1前有两个时钟CLK1和CLK2,图中没有信号跨越这两个时钟域,那么这两个时钟是逻辑独立、物理共存的。那如果有信号跨越这两个时钟域传输的话,CLK1和CLK2便不再是逻辑独立的了,可是U1的输出端口Z后的时钟,仍然是物理独立的,事实上,这种情况更为普遍。下面的约束也更为合适:

create_clock -name CLK1 -period 5[get_ports CLK1]

create_clock-name CLK2 -period 10 [get_ports CLK2]

create_clock-name CLK3 -period 15 [get_ports CLK3]

create_clock -nameCLK4 -period 20 [get_ports CLK4]

create_generated_clock–name G_CLK1 divide_by 1 –source [get_pins U1/A] [get_pins U1/Z] –combinational

create_generated_clock–name G_CLK2 divide_by 1 –source [get_pins U1/B] [get_pins U1/Z] –combinational–add

set_clock_groups –phisically_exclusive –group G_CLK1 –group G_CLK2

create_generated_clock–name G_CLK3] divide_by 1 –source [get_pins U2/A] [get_pins U2/Z]-combinational

create_generated_clock–name G_CLK4] divide_by 1 –source [get_pins U1/B] [get_pins U2/Z] –combinational–add

set_clock_groups –phisically_exclusive –group G_CLK3 –group G_CLK4

还有一种常见的情况是,时钟经过分频模块分出多个分频时钟,然后多个分频时钟经过时钟切换电路选择输出,而且分频电路中常有小数分频,比如1.5分频,且如果有信号从1.5分频时钟域传到未分频的时钟域,这时候最紧的时钟约束应是半个时钟周期,那么综合人员需要跟设计人员确认电路中绝无这种工作情况的可能,才能使用set_case_analysis来选择未分频时钟对后续电路约束。而电路是多个设计人员分别对各自模块设计的,假设和沟通常常容易出错,这时候如果在分频模块的输出端口产生两个物理独立的generated时钟,那么DC工具会给出分析结果。善用命令 set_clock_groups描述时钟关系,优势确实很明显。

三 、面对pad-limitted设计,可调节变量placer_max_cell_density_threshold进行迭代

现在 synopsys建议使用SPG流程,该流程和后端有更好的匹配和关联。如果综合人员所面临的设计是 pad-limitted,那么在第二次综合流程中可以声明一个最小单元密度,这让 core有更好的利用率百分比,也就是让DC围绕着核更密集的排布单元和连线。 set_app_var placer_max_cell_density_threshold0. 7; # In DC/ICC set_app_options -nameplace.coarse. max _density -value 0.7; # In ICC ll 注意:如果在non-spg流程中,DC使用了上诉命令需要在ICC中也使用,在spg流程中ICC 会略过这一步骤,可以不在ICC中做同样的命令设置。如果不对placer_ max_cell_density_threshold设置,DC默认其为50%,在执行了compile_ultra命令后,DC会对这个值重新计算,并将重新计算的值覆盖默认值。综合人员可以查看这个值,并可以将这个值设置为重新计算值和1之间的中间值,进而指导DC下一次综合。

四、尽量使用高阈值电压库综合,时序实在无法收敛时,使用多阈值电压库来综合

泄露功耗与工艺和阈值电压有关,阈值电压越大,泄露功耗越低,但是器件速度越慢。DC EXPERT 需要通过命令set_leakage_optimization true 声明,而DC Ultra会自动进行泄露功耗优化,为了不影响时序性能,DC会默认对非关键路径进行功耗优化。若采用了多阈值电压库,DC 会自动对非关键时序路径,用高阈值电压单元替换低阈值电压单元;综合人员可以使用set_multi_vth_constraint 命令来声明设计所允许使用的低阈值电压单元的百分比,并通过从5%到10%,开始逐步提升低阈值电压单元所占百分比,直到时序符合要求为止。在使用命令set_multi_vth_constraint时,带-type soft选项,DC会在保证时序的前提下,进行功行功耗优化;另外,在计算低阈值电压单元所占百分比的时候,并没有算进黑盒子,如果欲将黑盒子也算进来,使用-include_blackboxes选项。 一般工艺厂提供的工艺库都是已经根据阈值电压的不同对库单元进行了分组的,如果没有分组的话,多阈值电压库可以使用set_attribute命令对库属性进行设置,从而将多阈值电压库中的不同单元根据阈值电压的不同进行分组。

Library-level attribute: defaultthreshold voltage_group:string; Library-cell-level attributestring; 综合人员可以使用analyze_library–multi_vth 命令来获得各个阈值电压组的时序和泄露功耗信息。综合完成后,可以使用report_threshhold_voltage_group 命令,报告设计中低阈值电压单元占比情况。

五、使用set_app_var compile_timing_high_effort true 命令获得更好的时序QoR

在第二次综合时使用compile_ultra –timing_high_effort_script 是大家很熟悉的方式了,不过其中的开关选项-timing_high_effort_script目前在DC 优化过程中已经不起作用了,若希望DC 花费更多资源在时序优化上,那么可使用命令set_app_var compile_timing_high_effort true来获得更好的时序QoR。需要说明的是,该变量的设置只在Design compiler topographical模式下有效,即需要用compile_ultra -spg 命令进行综合优化。

以上几点纯是个人建议,写DC脚本的最终目的是设置合理的约束来指导DC更好的优化电路,每个人都有自己的习惯和综合策略,欢迎大家多多交流心得体会。

审核编辑:汤梓红

-

时钟

+关注

关注

10文章

1733浏览量

131446 -

DC

+关注

关注

9文章

3647浏览量

679638 -

触发器

+关注

关注

14文章

2000浏览量

61130 -

切换电路

+关注

关注

0文章

29浏览量

9408

原文标题:五点Tips助你DC应用进阶

文章出处:【微信号:芯司机,微信公众号:芯司机】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

五点技巧助你DC应用进阶

五点技巧助你DC应用进阶

评论