通过将吸电流负LDO配置为正电压灌电流,可以构建一个低压电源(1.3V)来端接PECL逻辑线路。

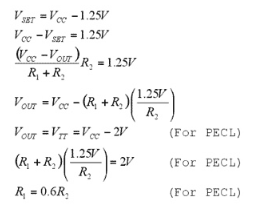

高速电信中使用的正发射极耦合逻辑(PECL)需要奇数电源电压:正VCC为+3.3V,终止电压(VTT)等于VCC -2V = +1.3V。VTT 电源相对于 VCC 进行调节,并且必须能够吸收电流。

大多数正低压差(LDO)稳压器不能吸收电流。负LDO是为此目的而设计的,但通常提供负电压。

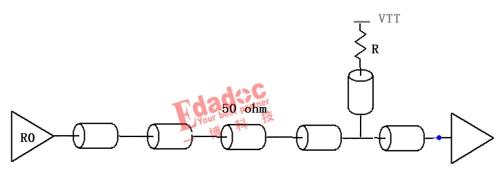

图1所示为针对正电压操作而修改的吸电流负LDO。GND 引脚连接到 VCC,IN 连接到地。这些连接允许负LDO作为正电压吸收器工作,其中VSET上的电压等于VCC -1.25V:

图1.所示连接使负输出LDO(具有固有的电流吸收能力)能够产生正输出电压。

输出电压相对于VCC进行调节。该特性非常适合PECL端接应用,因为它需要输出电压来跟踪VCC电源。最大输出电流受内部保护电路(约400mA)和封装功耗额定值(约550mW)的限制。对于需要更高输出电压或更高电流(或两者兼而有之)的应用,您可以添加串联二极管来耗散部分功率(图 2)。您可以根据需要添加任意数量的二极管来耗散功率,但OUT(引脚5)处的电压必须保持至少高于地电位300mV(IN,引脚2)。

图2.要在超过IC1内部或封装功耗额定值的电压或电流下工作图1电路,请如图所示添加功耗二极管。

审核编辑:郭婷

-

电源

+关注

关注

184文章

17704浏览量

249955 -

稳压器

+关注

关注

24文章

4223浏览量

93760 -

ldo

+关注

关注

35文章

1940浏览量

153310 -

PECL

+关注

关注

0文章

321浏览量

14301

发布评论请先 登录

相关推荐

端接电阻没选对,DDR颗粒白费?

用两个LDO分别做数字模拟电源的隔离,LDO的输出端接电压会对其输入端有影响吗?

高速PCB的终端端接

让你彻底摆脱抖动和时钟质量变低的4种端接方式

不加端接电阻的快乐,你们绝对想象不到!

不加端接电阻的快乐,你们绝对想象不到

DDR存储器端接电源灵活适用于2.5V和1.8V存储器系统

改进的LDO吸收PECL端接电流

改进的LDO吸收PECL端接电流

评论