今天要介绍的时序分析基本概念是 Latency , 时钟传播延迟。主要指从Clock源到时序组件Clock输入端的延迟时间。它可以分为两个部分: 时钟源插入延迟 (source latency)和 时钟网络延迟 (network latency)

source latency :也被称为insertion delay。主要指从clock source端到clock定义端的延迟,即是时钟源(例如PLL)到当前芯片时钟根节点(clock root pin)之间的延迟。

network latency :主要指从clock定义端到时序器件的clock pin端的延迟。

以下两张图分别定义了片上(on chip)和片外(off chip)中clock latency的描述。

我们可以用如下命令来定义描述clock latency:

#specify source latency

set_clock_latency 1.9 -source [get_clocks SYS_CLK]

#specify network latency

set_clock_latency 0.8 [get_clocks CLK_CONFIG]

那latency值有什么用呢?其实这相当于一个target值,CTS的engine会根据你设置的latency值来插入buffer(当然只是对network latency操作),做出一个接近于你设定的值,可能多一点,也可能少一点。

latency值的大小直接影响着clock skew的计算和固定。因为我们的时钟树是以平衡为目的,假设你对一个root和sink设置了1ns的latency值,那么对另外的几个sink来说,就算你没有给定latency值,CTS为了得到较小的skew,也会将另外的几个sink做成1ns的latency。过大的latency值会受到OCV和PVT等因素的影响较大。而当我们生长好了clock tree以后,latency的设定也就不起作用了。

-

时序分析

+关注

关注

2文章

127浏览量

22565 -

OCV

+关注

关注

0文章

25浏览量

12527 -

时钟源

+关注

关注

0文章

93浏览量

15956 -

PLL电路

+关注

关注

0文章

92浏览量

6403 -

时序分析器

+关注

关注

0文章

24浏览量

5277

发布评论请先 登录

相关推荐

时序分析基本概念介绍<Operating Condition>

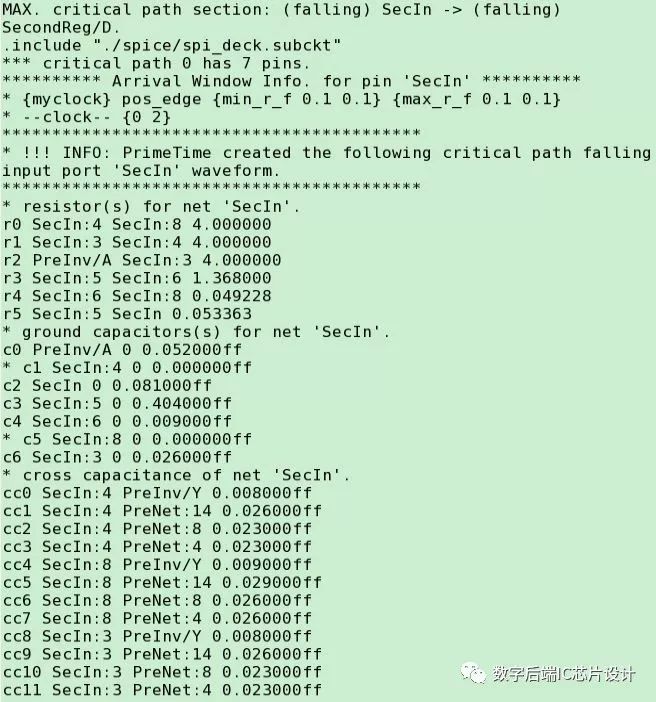

时序分析基本概念介绍&lt;spice deck&gt;

时序分析基本概念介绍&lt;generate clock&gt;

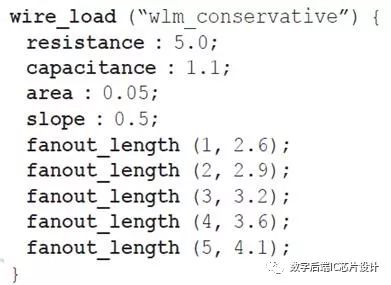

时序分析基本概念介绍&lt;wire load model&gt;

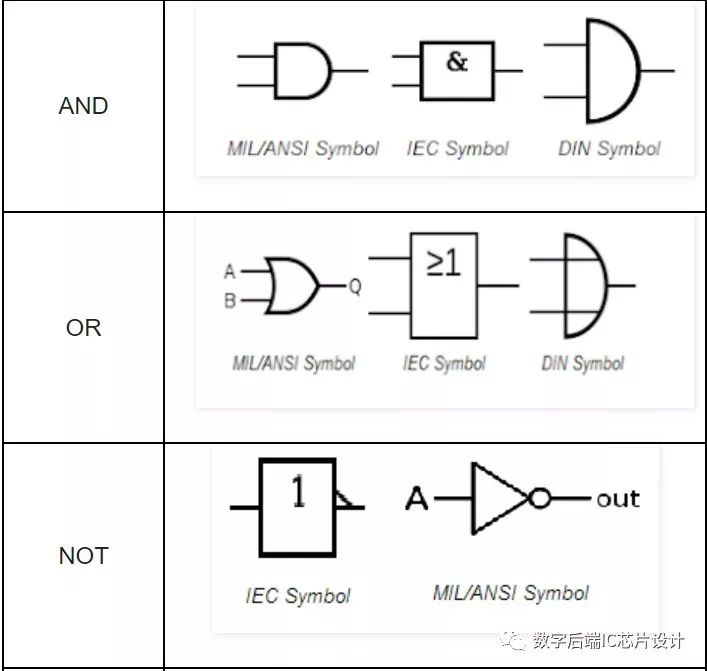

时序分析基本概念介绍&lt;Combinational logic&gt;

时序分析基本概念介绍<Latency>

时序分析基本概念介绍<Latency>

评论