作为高频、高增益及高功率器件,PA(Power Amplifier,功率放大器)的“自激”是必须要认真设计与考虑的问题。

“自激”译自“Self-Oscillation”,是指电路在非激励的频率下,自我产生周期性信号并维持的现象。“自激”的发生一般是因为电路环路出现不稳定,在某个频率产生“震荡”。所以“自激”问题又叫“稳定性(Stability)” 问题、或“震荡(Oscillation)”问题。

PA作为射频系统里输出功率最大、增益较高、应用环境最复杂的器件,是系统中最易发生“自激”的电路模块。在大功率PA中,一些自激现象有可能产生不可控的大功率及大电流,进而烧毁PA,造成Ruggedness问题;即使一些自激现象轻微,不至于使器件损坏,但这些杂散也会恶化射频系统收发性能,也需要避免。

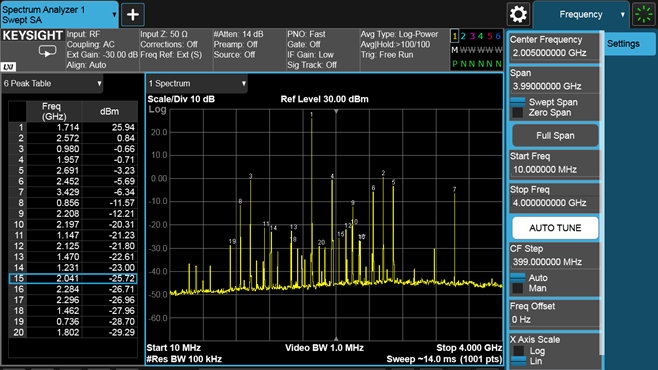

图:PA的自激现象

(主频信号为1.714GHz,其他杂散信号为自激产生)

PA是一个带有非线性的功率输出器件,其稳定性问题来源复杂,较难分析。本文尝试将稳定性的主要来源,以及分析、解决思路做一个梳理,讨论如何规避PA的自激。

0****1

“自激”的分类

“自激”并不是当前半导体PA的特有现象,而是伴随着有源电路的产生一直存在,早在100年前的真空管时代,稳定性问题就已经得到重视并开展研究 [2]。对于射频电路设计者来说,“自激”也并非一直是“噩梦”,在VCO(Voltage Control Oscillator,压控震荡器)设计中,就需要建立起稳定的自激来产生需要的本振信号。

根据产生的原因,主要可以将“自激”分为如下两类:

1.线性自激

2.非线性自激

线性自激是指由于耦合、正反馈等线性耦合回路引起的环路自激,一般的低频、高频震荡均属于线性自激。

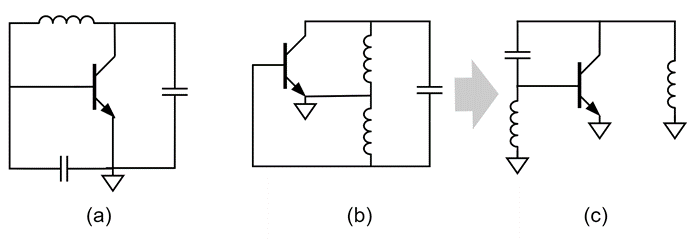

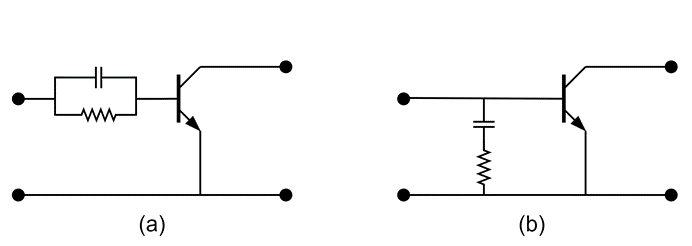

典型的线性自激震荡电路如Hartley Oscillator和Colpitts Oscillator。在射频PA电路中,带有高通反馈特性的Hartley Oscillator与PA Collector/Base间反馈引起的震荡成因更为接近,Hartley Oscillator的分析理解方法可用于部分线性自激分析中。

图:(a)典型的Colpitts Oscillator

(b)典型的Hartley Oscillator

(c)Hartley Oscillator电路针对于PA的电路等效

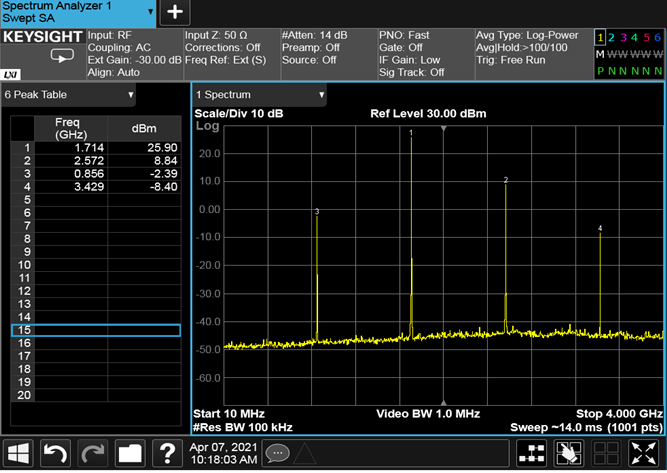

非线性自激是指由于器件的非线性引起的自激,一般分为谐波自激与次谐波(半频、1/3频等)自激。这些自激的发生与器件特性随参数变化而变化有关,所以又被叫做参数震荡(Parametric Oscillation),参数震荡在过去50年里也被广泛研究。

图:非线性自激产生半频震荡的典型频谱

以下将对两种“自激”的分析与解决展开讨论。

0****2

“线性自激”的分析与解决

**“线性自激”的分析

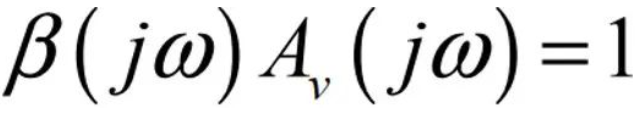

线性自激产生的原因是环路发生了正反馈,一般的分析方法有:环路分析法、负阻分析法、S参数网络分析法等。

- 环路分析法是分析反馈环路,看是否存在环路增益大于1的现象;

- 负阻分析法是指分析发生自激部分电路的阻抗,如果是负阻且负载阻抗小于负阻阻抗的绝对值,则将可能发生自激;

- S参数网络分析法是利用S参数的方法,进行稳定性分析。

以上分析方法在不同的电路设计中都有采用,不同方法殊途同归,可相互转化,均可以对“自激”现象进行分析。以下采用环路分析法对自激问题进行说明。

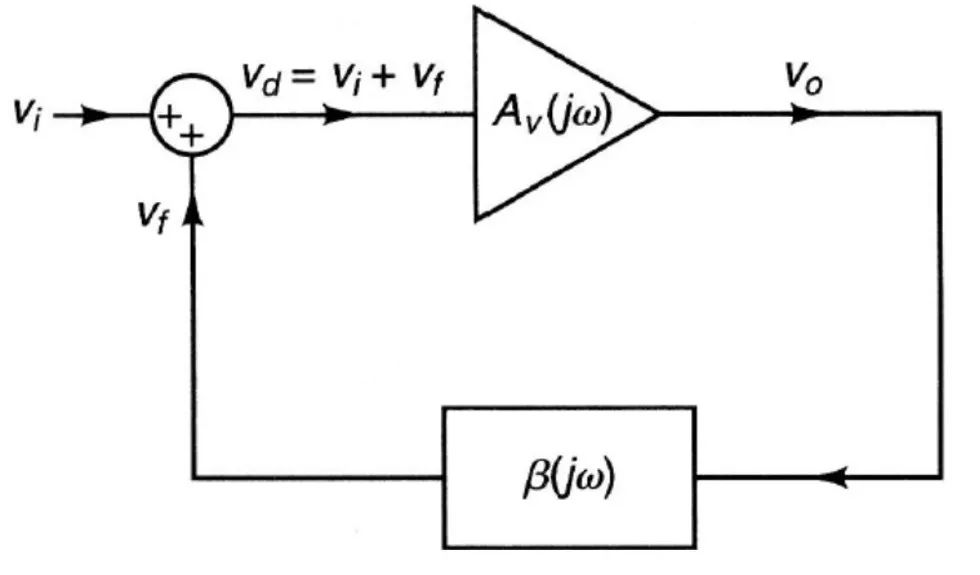

图:带有反馈的射频环路

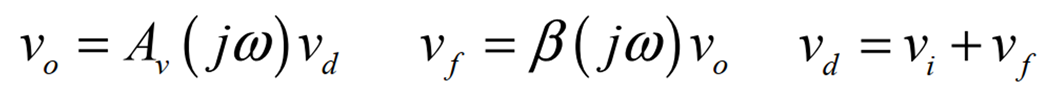

对于带有反馈的射频环路,可表示为如上图所示。在此环路中:

环路增益可表示为:

为震荡发生的边界条件。Hartley及Colpitts结构形成的震荡均可以用环路分析法进行分析。

当满足震荡条件时**,** 白噪声在环路中不断被放大强化 ,产生自激。因为白噪声在所有频率范围均存在,所以任何频率点满足震荡条件,均会发生震荡。

** “线性自激”的规避**

**PA设计侧的规避 **

在PA设计时,需要对自激问题做仔细排查与规避。射频PA一般通过S参数网络分析法进行分析,S参数网络分析法在教科书中均有详细讨论,在此不做过多讨论。

需要注意的是,通过S参数进行稳定性分析有以下限制:

- S参数是基于小信号的参数,所分析出来的稳定性是小信号状态下的稳定性。

- S参数分析法依赖于模型的准确性和完备性,如果耦合路径在模型中没考虑,分析结果将产生偏差。

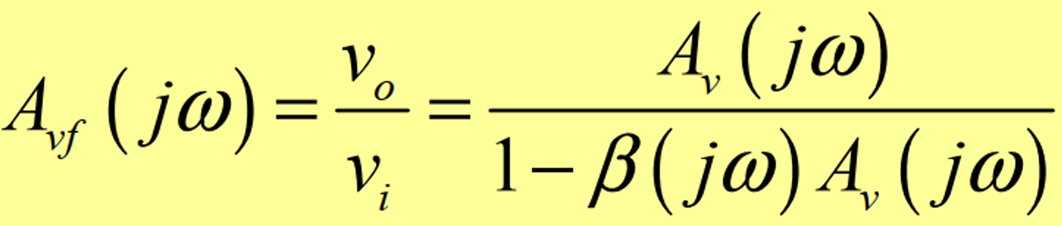

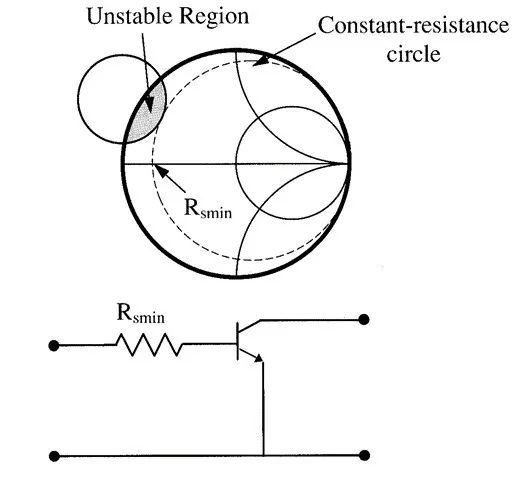

S参数网络分析后,会得到稳定系数和稳定圆,一般设计中需要保证全频段稳定系数大于1,即绝对稳定。

如果在设计中发生稳定性系数有小于1的现象,则需要在设计中进行规避。在链路中增加损耗性器件是一种常见的设计方法。在增加损耗性器件时,需要根据不稳定的特性进行设计,有效解决稳定性问题的同时,尽量小的影响射频性能。

下图为典型的稳定性改善电路,不稳定区域在Smith圆图左侧,此时在输入端串联电阻最为有效,而并联电阻并不能有效改善此电路的稳定性[3]。

图:典型稳定性的改善:增加链路损耗

损耗型网络也可以设计成带有频率响应,来针对性的改善某个频点的稳定性。下图分别为改善低频和高频稳定性的典型电路。

图:(a)改善低频稳定性的电路

(b)改善高频稳定性的电路

**PA应用侧的规避 **

“线性自激” 一般是由于信号的耦合产生正反馈引起,如果耦合发生在应用侧,则可以通过应用侧的方法进行规避。

在应用侧常见的信号耦合路径有:

- 通过电源线引起的低频耦合。

- 通过信号线引起的高频耦合。

- 由于接地不良引起的共模耦合。

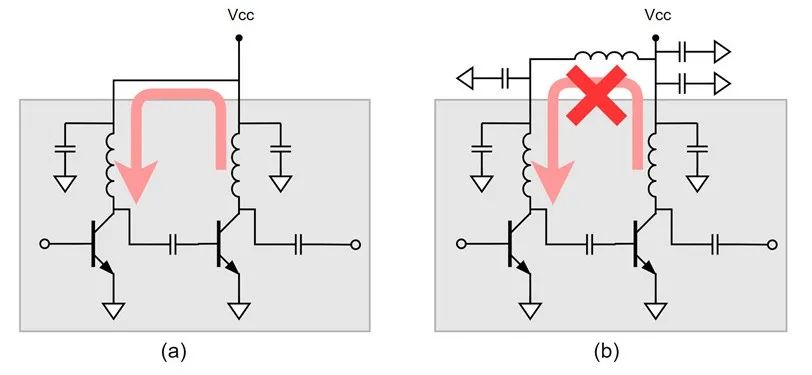

通过电源线引起的低频耦合

在低频段,一般每降低10倍的频率,晶体管的最大可用增益会提高20dB,晶体管在低频段有极高的增益,如果对低频的信号处理不好,则会在低频引起震荡。

低频信号耦合的最主要通路是电源线。由于电源的馈电和去耦网络的低通特性,如果去耦不充分,则电源处有大量被放大的低频噪声信号,当这些信号反馈到前级时,将有可能发生震荡。

如果发生低频震荡,需要仔细检查电源处的去耦电容是否使用得当,是否存在将多级电源拉在一起的现象。规避的方法是将去耦电容仔细设计,必要时可利用去耦电容的自谐振特性,构建某个频率点的陷波;并且将不同级的电源线尽量区隔,可在不同级电源线间串接电感增加隔离。

图:电源引起的低频耦合及规避

(a)通过电源的低频耦合路径

(b)通过电源的低频耦合路径规避

**通过信号线引起的高频耦合 **

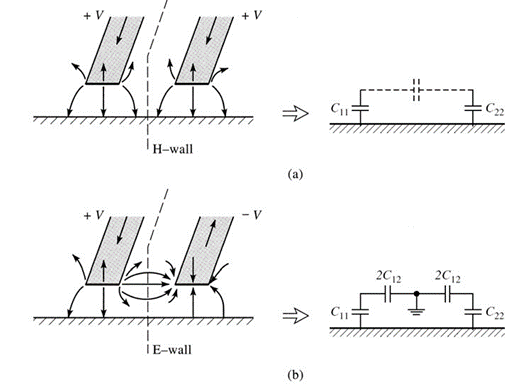

对于非接触射频走线,一般频率越高耦合越明显。对于高频信号,需要避免因为空间耦合引起的信号正反馈。对于应用中常用的微带线结构,耦合传输线的等效模型如下图所示。不同传输线间的耦合等效为并联电容。

图:耦合传输线的等效模型

在规避上,需要仔细检查信号走线,由于输入和输出间放大器增益较大,需要尤其注意输出和输入之间的信号反馈。

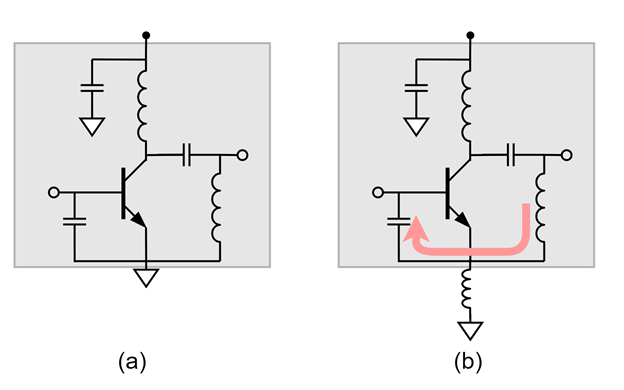

由于接地不良引起的共模耦合

在手机PA设计中,一般是采用多颗晶圆在基板上进行系统级集成实现。基板上接地通孔的存在,使得PA模组电路存在共模电感。如果在应用中发生接地不良,将会增加共模电感的感值,进而增加模组内部的信号耦合。

图:(a)良好接地(b)非良好接地引起的共模耦合

在规避上,需要确保模组芯片接地良好,减少共模电感值。

0****3

“非线性自激”的分析与解决

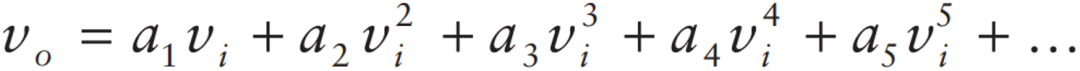

PA是一个非线性器件,其非线性主要表现为两个方面,首先PA一般工作于Class AB状态,本身会产生非线性;其次是用于设计PA的HBT器件本身的C BC 、CBE电容等存在非线性。PA的非线性可以用Volterra级数来表示。

由于器件的非线性引起的自激称为“非线性自激”,非线性自激分为两类,分别是:

1.谐波自激。

2.次谐波自激。

谐波自激是指发生“自激”的输出信号处于输入信号的谐波频率。由于谐波能量产生稳定,频率可控,可通过滤波器进行滤除,并且不会对主信号能量产生明显影响。谐波自激一般并不作为通常的“自激问题”进行分析和处理。

次谐波(Sub-harmonic)自激是指发生于信号次谐波(半频、1/3频等分数频)频率的自激。由于次谐波发生的频段可能是有用频段,并且一旦发生可能对主信号质量造成影响,是需要在设计中规避的自激问题。以下将对次谐波自激进行详细讨论。

** “次谐波自激”产生的机理

次谐波自激原因复杂,较难分析,一直没有清晰简单的模型进行讨论。目前对次谐波自激的分析主要从两个角度进行,分别是器件角度和系统角度。

从器件角度分析,Imbornone等人在1997年于JSSCC上发表的文章认为,PA设计中半频震荡与BJT器件的Base Charge Storage相关 [5]。该方法源自于对PN结器件的非线性分析,Penfield等人在1962年对变容二极管的次谐波产生做过讨论[6]。不过由于器件侧机理复杂,这种分析方法还没有在PA设计中得到广泛应用。欢迎对此分析方法有研究的专家留言,详细讨论。

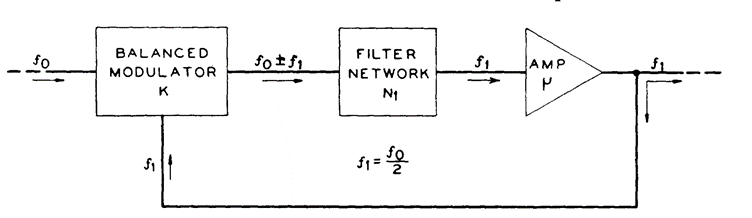

在系统角度分析方法上,R. L. Miller等人于1939年发表论文,讨论再生分频器的设计[7]。文章将主频信号与半频信号放在混频环路中进行分析,非线性器件产生混频增益,当混频增益与反馈回路共同引起的环路增益大于1时,将产生半频信号。

图:R. L. Miller于1939年对半频信号的产生进行分析[7]

R. L. Miller利用这种特性,设计了产生半频信号的分频器。业界称此种分频器为“再生分频器(Regenerative Divider)”,同时也叫Miller分频器。

R. L. Miller应用于Miller分频器件的方法同样可用于分析半频震荡:当PA中的非线性元件HBT在半频混频增益过大,同时存在较大增益的半频的反馈回路时,将可能发生半频震荡。

** “次谐波自激”的规避 **

了解次谐波自激产生的机理之后,可对次谐波自激进行规避。

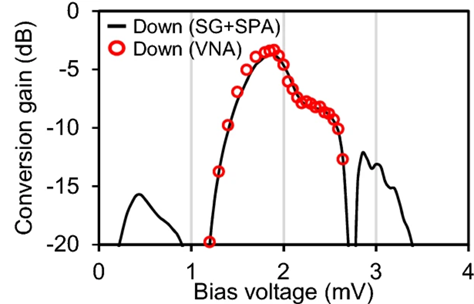

** 方法1:降低混频增益 **

次谐波自激由于次谐波混频引起,可减小混频增益,切断次谐波与主频的混频。

PA作为非线性器件,其混频增益与偏置点相关。一个典型的混频器混频增益与偏置的关系与下图所示[8]。混频增益在某个区间存在最大值,若半频震荡发生,可以适当增加或减小偏置,改变HBT器件的混频增益

图:一个典型的混频器混频增益与偏置间的关系

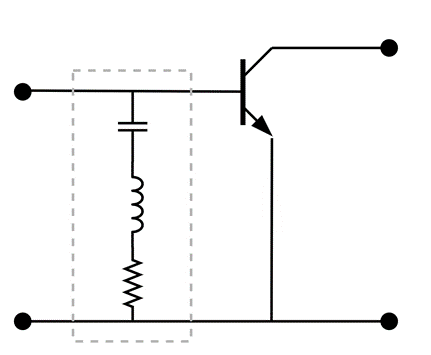

** 方法2:增加反馈损耗 **

另外一个改善次谐波自激的方法是增加次谐波点的路径损耗,从而减少环路增益。

对于半频震荡,可以针对半频频点在链路中针对性的加入损耗性网络,打破半频的起震条件。典型的针对半频的损耗性网络如下图所示:

图:谐振于半频频率的损耗网络

** 方法3:检查耦合路径 **

检查模组内是否有其他耦合路径,如果有半频或其他次谐波频率信号的耦合路径,需要加以规避。

** “次谐波自激”的说明**

一般次谐波自激的发生是由于芯片内部器件的非线性引起,大多数情况下,半频或者其他次谐波频率的耦合路径也存在于芯片内部,若内部配置不改变,一般较难通过应用侧来解决。

若在应用中发生如半频震荡、1/3频震荡的次谐波自激现象,建议联系PA原厂寻求解决方案。

0****4

实战中的“自激”问题

由于一旦确认是震荡问题,则需要花费大量的资源进行实验。而发生杂散不一定是震荡,还有可能是带外干扰信号,所以一定要准确清晰定位是否发生震荡:

- 如果看到的只是干净、稳定的少量毛刺,且不随PA的功率、Bias变化而变化,则有可能是空间干扰信号或者Transceiver干扰信号,不是发生震荡。

- 如果看到噪底整体抬高,出现不高的鼓包而不是毛刺,也有可能不是震荡,需要检查是不是经PA放大的输入噪底。

- 为了减少干扰,PA输入端需要串接滤波器,滤除输入带来的带外杂波;测试也需要在屏蔽环境进行。

在实际应用中,自激问题并不如理论分析中那样容易定位。而且自激发生后,通常是产生如文章首图中的众多毛刺,让人分不清究竟是低频震荡、高频震荡还是半频震荡。不过从经验上,总是可以找到最主要的震荡来源。一般对震荡定位时可以采用以下方法:

- 如果是众多毛刺,则从最高的5-10根毛刺看起。

- 以MHz为单位,变换5次以上主频的频率,记录几根毛刺的频率变化。

- 根据毛刺频率变化关系,分析哪根毛刺是震荡产生,哪根毛刺是混频产生。

- 确定震荡毛刺之后,根据其震荡频率,进行改善规避。

自激问题成因复杂,不易分析,在分析过程中一定要大胆假设,小心求证。

0****5

文章结语

自激问题与Ruggedness问题一样,是PA工程师逃不开的常见问题。

严重的自激会导致整机杂散超标,出现合规问题,并且自激还可能会影响通带内的信号质量。不可控的自激还可能导致功率及电流过大,引起PA烧毁。自激问题一定要在设计和应用中高度关注,加以规避。

-

滤波器

+关注

关注

161文章

7795浏览量

177989 -

功率放大器

+关注

关注

102文章

3568浏览量

131807 -

去耦电容

+关注

关注

11文章

315浏览量

22325 -

射频系统

+关注

关注

0文章

118浏览量

13320 -

震荡器

+关注

关注

1文章

13浏览量

8348

发布评论请先 登录

相关推荐

线性功率放大器设计和乙类和丙类功率放大器设计

ANADIGICS推出功率放大器PA系列

功率放大器的选购 采购原理分析

RF功率放大器的设计

功率放大器PA04原理及其应用

ANADIGICS推出功率放大器PA系列

ANADIGICS推出新型功率放大器(PA)AWB7230

一文解读功率放大器(功率放大器如何选型)

PA功率放大器的基础知识

功率放大器PA自激问题的分析与解决

功率放大器PA自激问题的分析与解决

评论