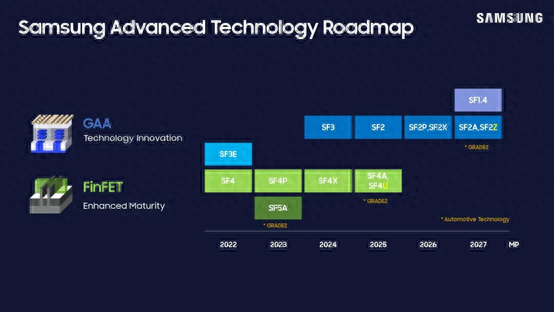

据最新报道,Cadence Design Systems 的工具已通过 Samsung Ondry 2nm 工艺的数字、定制vwin 和背面布线认证。

数字和定制模拟设计流程经过了 SF2 2nm 和 SF3 3nm 工艺认证,而完整的背面布线解决方案则为移动、汽车、人工智能和超大规模应用提供了下一代高性能芯片。

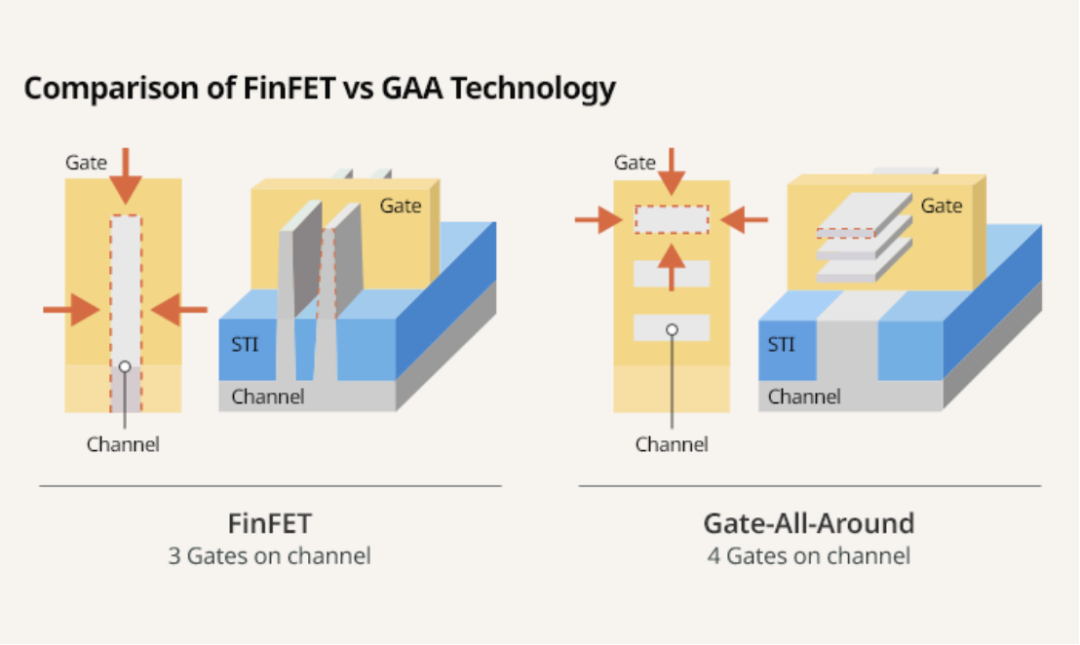

背面实施流程已通过成功的 SF2 测试芯片流片得到验证。这是 2nm 设计的一项关键功能,但可能会受到三星、英特尔和台积电缺乏布线的限制,而是在晶圆背面布线并使用过孔连接电源线。

该认证意味着工程师可以使用定制和模拟工具(包括基于 AI 的 Virtuoso Studio),根据经过认证的 SF2 和 SF3 流程,使用 PDK 设计 IC。

该流程包括 Genus 综合解决方案、Modus DFT 软件解决方案、Innovus 实施系统、Quantus 提取解决方案和 Quantus 场求解器、Tempus 时序签核解决方案和 Tempus ECO 选项、Pegasus 验证系统、Liberate 表征产品组合、Voltus IC 电源完整性解决方案和 Cadence Cerebrus 智能芯片浏览器。

单元交换支持可帮助设计人员对齐单元引脚以进行直接连接,以节省布线资源,同时支持各种组合的混合行解决方案,以最大限度地提高基于区域的设计规则,以及使用掩模移位单元和水平单元放置和细化走线的能力半履带移动单元以减少位移。由于通过订书钉插入增强型、修剪感知功能,还支持各种直线标准单元,以实现更高的密度并减少 IR 降。

背面布线依赖于 Innovus GigaPlace 引擎,该引擎可自动放置并合法化纳米硅通孔 (nTSV) 结构,从而实现正面和背面层之间的连接。Innovus GigaOpt 引擎将背面层用于时序关键的长线,以提高芯片性能,而 Innovus NanoRoute 引擎本质上支持基于该技术的库交换格式 (LEF) 中的规则的背面布线。

Quantus 提取解决方案完全支持背面层,使 Tempus 时序解决方案能够签核正面和背面层混合的设计,从而降低配电网上的压降并提高正面金属层的可布线性。

三星电子代工设计技术团队副总裁 Sangyun Kim 表示:“通过与 Cadence 的持续合作,我们不断寻找新方法来帮助我们共同的客户加速下一代设计创新。” “这一背面设计流程的成功推出,得到了 Cadence 数字流程的全面支持,让客户能够从我们先进的 SF2 技术中获益。”

Cadence 数字与签核集团公司副总裁 Vivek Mishra 表示:“设计人员可以利用我们与 Samsung Foundry 在完整 RTL 到 GDS 流程和 SF2 技术方面的合作来加快产品上市速度。” “我们已经看到了成功的流片,我们期待看到我们的客户使用我们的最新技术取得更多的设计成功。”

定制/模拟设计工具为客户提供了多种优势,例如更好的拐角模拟管理、统计分析、设计中心和电路优化;支持现代计算场以及私有和公共云配置上的并行操作;整个布局环境具有更好的性能和可扩展性;混合信号 OpenAccess 设计套件,可与 Innovus 实施的布局布线引擎无缝集成,从而提高结果质量;总结了 EM-IR 信息,其中突出显示了电阻值、金属层、宽度和长度信息的违规情况和详细信息;以及有关电路性能和可靠性的反馈。

“通过我们与 Cadence 的最新合作,我们看到早期客户利用 Cadence 认证的设计流程以及我们先进的 SF2 和 SF3 工艺技术提高了生产力,”Kim 说。“借助新的 PDK,我们使下一代移动、汽车、人工智能和超大规模设计的开发人员能够更轻松地采用我们的技术并更快地将创新推向市场。”

-

芯片

+关注

关注

455文章

50712浏览量

423108 -

电源完整性

+关注

关注

9文章

209浏览量

20726 -

三星

+关注

关注

1文章

1521浏览量

31203

原文标题:三星2nm,走向背面供电

文章出处:【微信号:芯长征科技,微信公众号:芯长征科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

三星2nm,走向背面供电

三星2nm,走向背面供电

评论