概述

本文主要介绍一种基于FPGA的FT232H接口通信开发方案。传统的USB通信开发对工程人员的要求比较高,除了上层应用软件以外,还需要掌握一定的USB传输协议、固件编程以及底层驱动等等。对于FPGA固件开发人员来说,我只关心数据如何可以正确的收发,说白了就是给我说清楚接口交互时相关信号之间的时序关系即可,其他的内容并不是这么关心。FTDI公司的FT232H应运而生,他把USB的相关协议封装在芯片内部,只把数据端口部分开发给工程开发人员。与市面上另外一款USB芯片(cypress的CY7C68013)相比,FT232H在模式配置上,有官方提供的工具软件直接进行模式配置,而不需要像前者那样,还要编写模式配置的相关代码,从而大大提高开发效率。

接口芯片FT232H

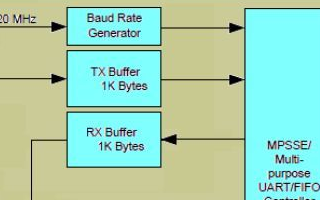

FT232H是一款单通道的高速USB转UART/FIFO芯片,支持USB2.0协议。通过配套的软件可以配置成不同的应用模式,如下图所示:

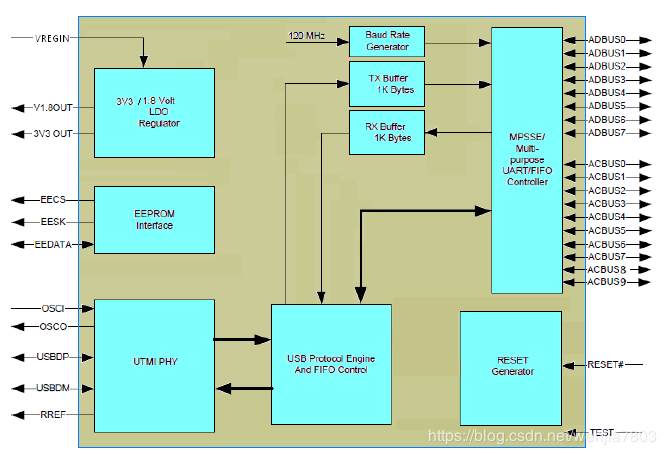

FT232H的内部结构

从图1中我们可以了解到,FT232H芯片内部可以划分为UTMI_PHY、USB_protocol and FIFO ctrol、Tx/Rx Buffer、MPSSE/Multi_purpose UART/FIFO controler以及EEPROM_interface这几部分。其中MPSSE/Multi_purpose UART/FIFO controler是面向用户设计的IO,通过配置成不同的模式,管脚对应的定义不一样。

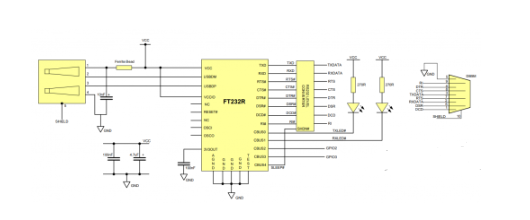

我们通过把FT232H配置成同步FIFO模式,已达到最快的传输速率。

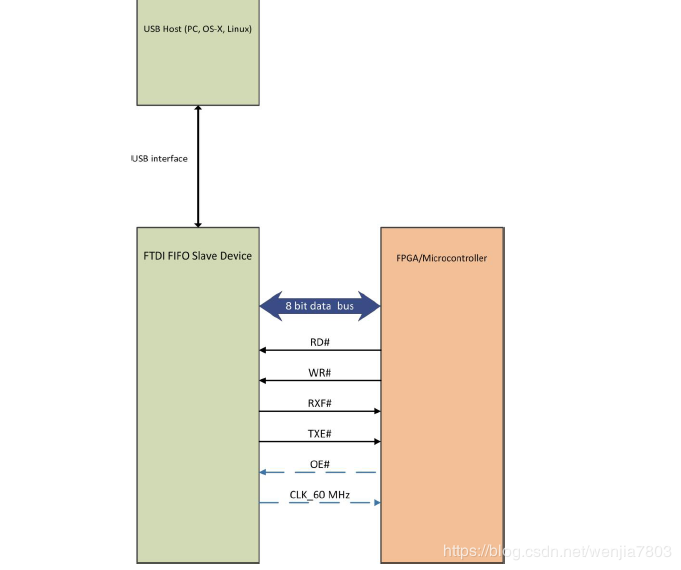

FIFO模式下的拓扑结构

软件设计

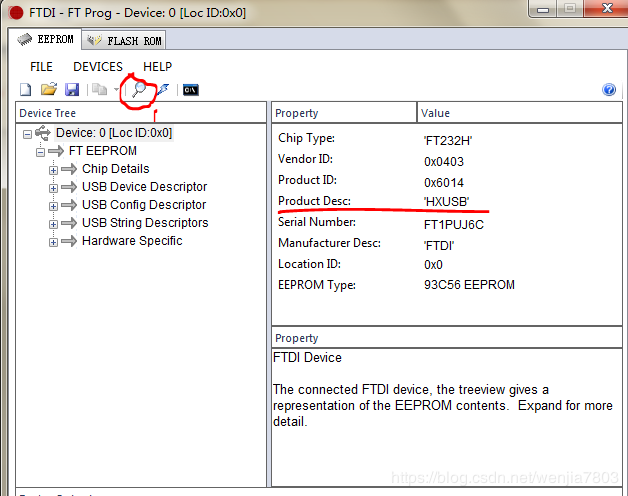

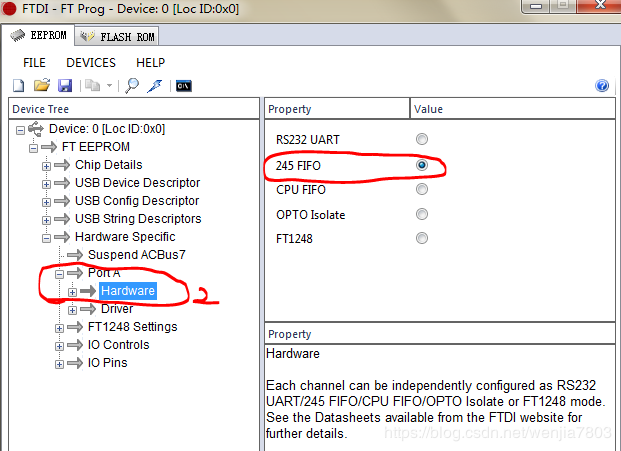

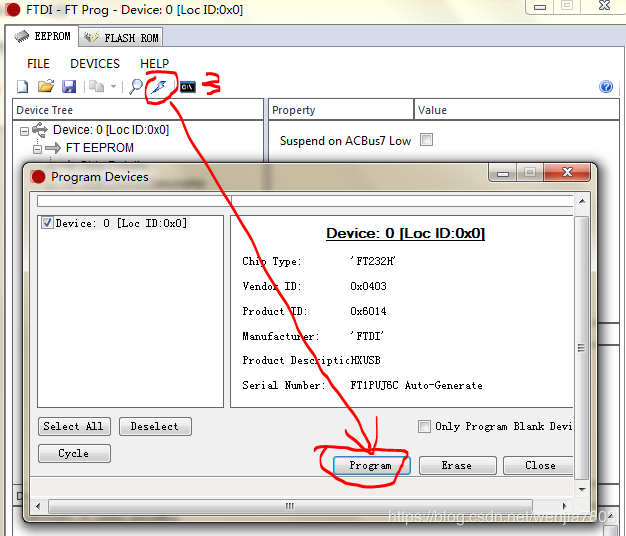

芯片工作模式配置

FT232H在出厂的时候,默认是UART模式,配置长同步FIFO模式,需要通过官方提供的配置软件FT_PROG进行配置,配置过程十分简单,如下:

如上图所示,配置过程大体上可以分为上述3个步骤。需要注意的是在进行第一步之前,PC上需要安装好相应的驱动,才能够识别出芯片;还有一个需要注意的地方是,Property中product_desc里面的值可以自己修改,但是上位机一定要与之对应,否则编写的上位机软件有可能打不开设备。

代码设计

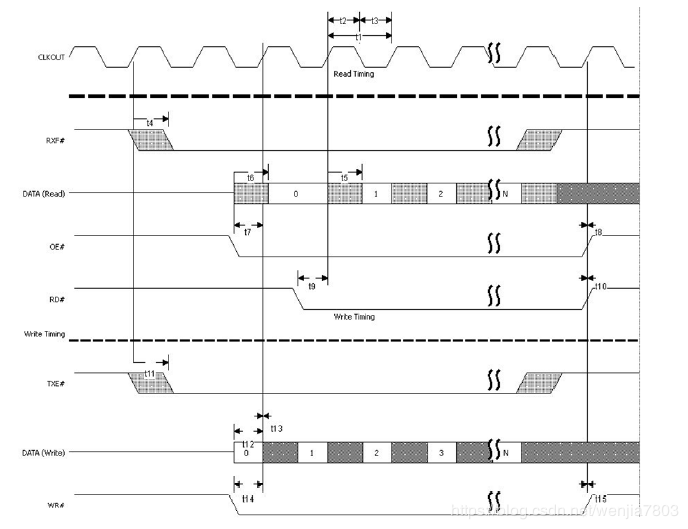

同步FIFO模式下的读写时序关系

发送端(FPGA--->USB--->PC)

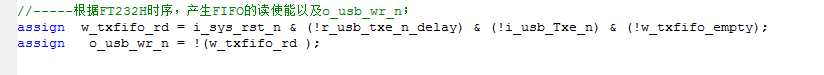

通常来说,为了处理好异时钟域数据传输问题,都会在FPGA端例化一个FIFO来作为与USB接口交互的缓存。在数据发送有个需要注意的地方,当发送速率比USB传输速率快,FT232H内部缓存被填满的时候(TXE#被拉高),会出现丢数据情况。在处理的时候需要特别注意一下。

我们画一下相关时序就知道怎么回事了。

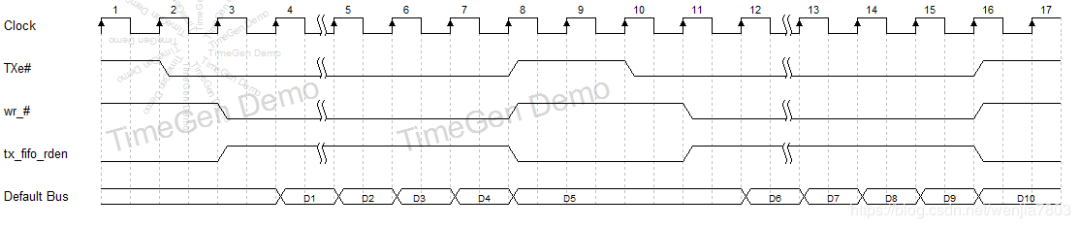

FIFO常规模式下时序图

从图中可以看出,FIFO的读使能持续了5个clk,由于FIFO的输出最少都有1个clk的延迟,所以这次数据传输只传输了4个有效数据,剩下一个数据只能由下一次传输,当然这种情况,在传输流式的数据是没有问题的,碰上我之前的项目,读写由上位机发起,并且读写的数据长度也由上位机决定的时候,就会出现上位机会少接收一个数据的现象。

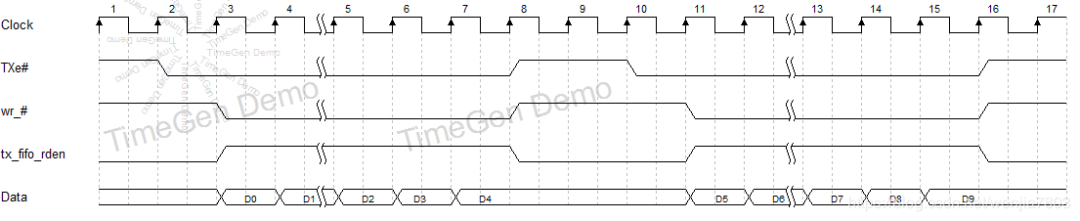

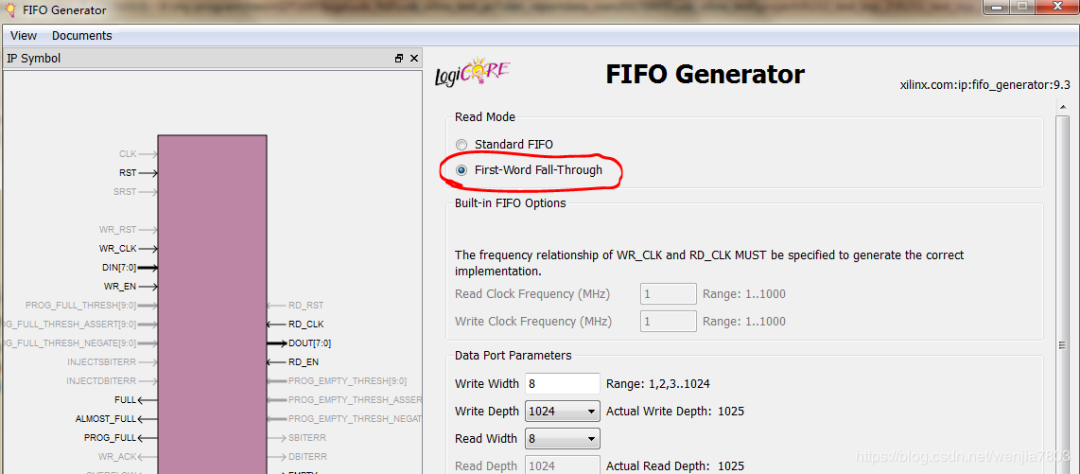

那么有没有办法解决这种现象呢?答案是肯定的,我比较推荐的一种方法如下:

将例化FIFO的时候,设置成First_word Fall through模式就可以了,至于这种模式是什么,请自行度娘脑补一下。

方法还有很多,只要时序对的上即可。

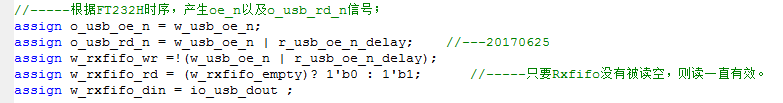

接收端(PC—>USB--->FPGA)

接收端的设计比较简单,这里就不展开论述了。

-

FPGA

+关注

关注

1629文章

21729浏览量

602953 -

芯片

+关注

关注

455文章

50711浏览量

423105 -

接口通信

+关注

关注

0文章

9浏览量

13395

发布评论请先 登录

相关推荐

【紫光同创国产FPGA教程】【第二十八章】USB双向测速例程

UM232H-B是FT232H高速到串行/并行接口转换器的开发模块

FT232H单通道USB至串行/并行接口分线板开发模块UM232H-B-WE

用于FT232H单通道USB至串行/并行接口分线板的开发模块UM232H-B-NC

采用FT245BM和FPGA实现USB接口设计

接口转换芯片-FT232RL

PIC32MX与FTDI FT232H接口如何同步并行

用于FT232RL USB-to-UART接口的串行UART开发模块

USB2.0高速至MPSSE SPI模块VA800A-SPI是一个小型电子电路板

基于FT8U232BM的USB-HART通信接口的开发

基于FT232BL的USB接口快速设计

一种基于FPGA的FT232H接口通信开发方案

基于FPGA的FT232H接口通信开发方案

基于FPGA的FT232H接口通信开发方案

评论