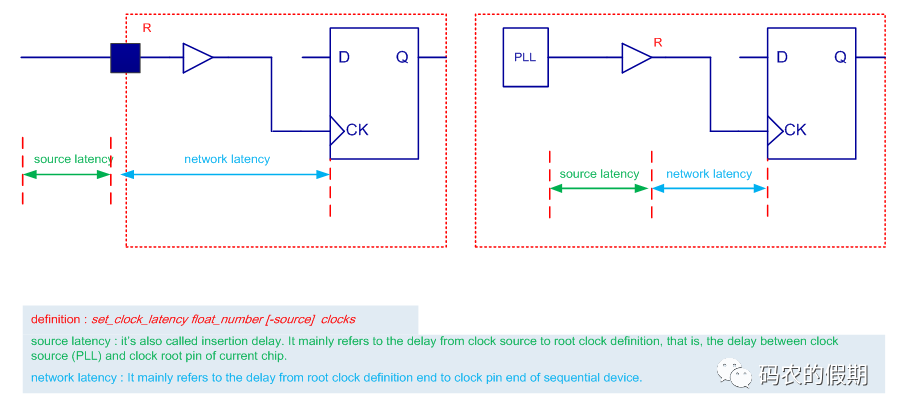

Clock定义指令

Clock分为两大类,一类是root clock,其定义指令是 create_clock ;另外一类是generated clock,其定义指令是 create_generated_clock 。在做设计约束时,如何选择合适的约束指令和指令option是非常关键的,这将直接影响到工具的行为,如果选择有误,将会让工具的行为不符合自己的预期。

create_clock ** option浅析**

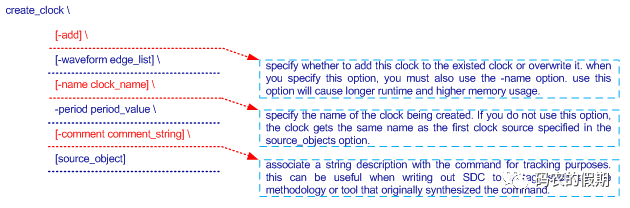

图1 create_clock介绍

如图1中所示,列出了create_clock的所有option以及其详细的解释。在这些当中加“[]”的为可选项,其它的为必选项。其中比较关键的-add,推荐大家最好是都要加上,防止PAD/port共用,造成clock被覆盖;-name,推荐大家一定要加上,杜绝系统自动分配命名。

create_generated_clock option浅析

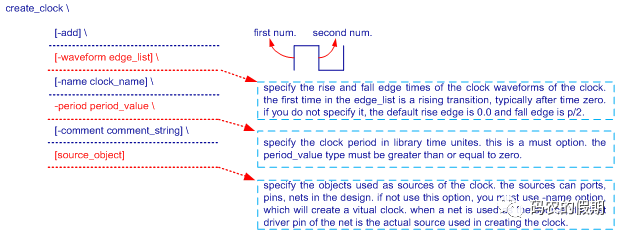

图2 create_generated_clock options

如图2所示,列出了create_generated_clock的所有option以及详细解释,供大家参考。在这些当中,用“}”包起来的可以看做是一组参数,有类似的功能。接下来,重点跟大家探讨下create_generated_clock中的一些option的使用区别。

multiply_by/duty_cycle详解

首先说下multiply_by选项,其意思是倍频多少,主要应用在PLL的倍频clock的输出点的clock的定义,如果其master clock的duty cycle不是50%,然而,经过PLL之后,duty cycle往往都是设计成50%输出,所以可以配合-duty_cycle选项改变定义的clock的duty cycle。

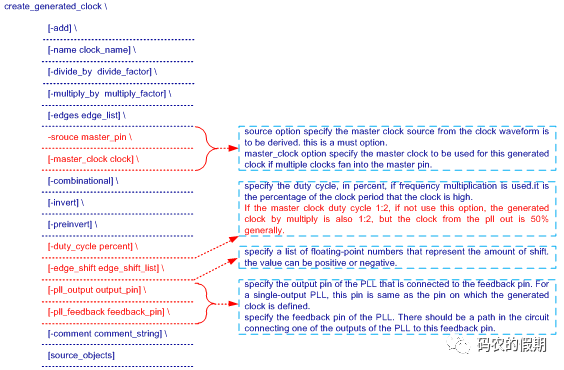

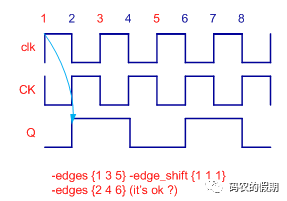

divide_by/edges详解

divider_by表示除频的意思,例如最常见的2分频电路可以用-divide_by 2定义,如图3右中波形所示。但是有时,design设计的divider可能是采用ICG抹掉时钟边沿的方式实现的,如图3左所示。这时经过divider之后出来的波形并不是标准的2分频波形,这时候就不能直接采用-divider_by 2的方式定义分频之后的clock,因为如果采用了divide_by的方式定义了,那么其工具认知的行为波形,跟design实际输出的波形是不符的,如果分频后的时钟,应用在falling edge触发的DFF当中,可能就会造成工具timing check错误。(此处不详细解释了,大家可自己画波形思考)

图3 divide_by/edges options

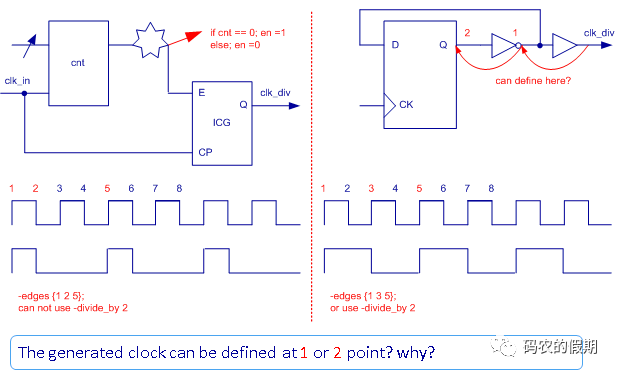

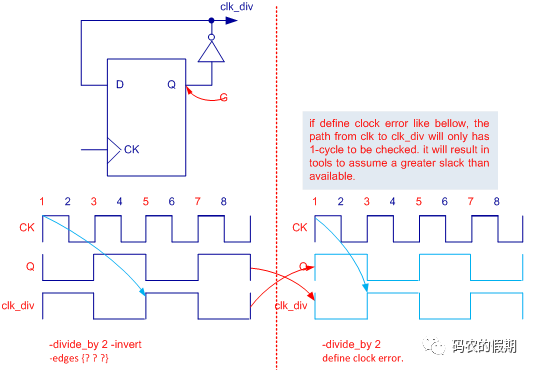

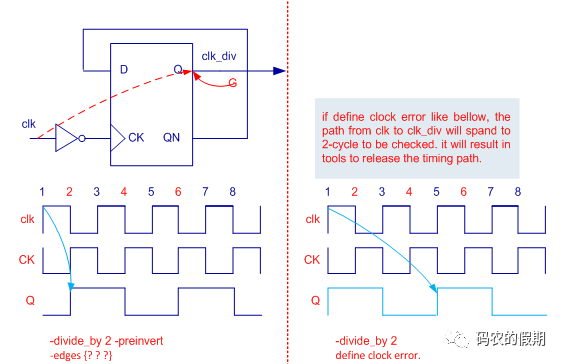

invert/preinvt/edge_shift详解

-invert/preinvert分别表示:先定义clock后clock取反还是先clock取反后定义clock。我通过两个例子跟大家解释一下。如图4所示,将刚才图3右中clock的定义点修改到register的Q-pin上,如果继续使用-divide_by 2的方式定义此clock,那么工具认为的DFF/Q的波形应该是图4右所示的。但是实际上,分析可以知道,design输出的clock波形应该是图4左所示的波形。

工具在做setup timing分析时,是从launch DFF的触发沿到capture DFF的下一个触发沿之间的时间,所以基于错误的clock定义之后,工具的timing check行为将变成图4右蓝色箭头所示的行为。但是实际design预期的行为应该是图4左蓝色箭头的行为。从图中对比可以看出,工具timing check与designer预期不符。如果要正确的在DFF/Q pin上定义clock,应该加上-invert选项(即-divide_by 2 -invert)。

图4 invert option示例

虽然在图4示例中,工具的行为跟designer预期不符,但是分析可知,此时是加紧了工具的行为,即变得悲观了,可能结果是浪费一些PPA,但是不至于design最终行为出错。但是如果出现如图5所示的情况就不一样了。如果是按照图5所示的分频设计,我们同样在DFF/Q pin上定义2分频的clock,同样仅使用-divide_by 2的方式,那么定义完之后,工具认为的clock波形是如图5右所示的情况,而design实际的波形应该是图5左所示的情况。这时工具如果继续按照图5右蓝色箭头去做setup timing check,很明显是放松了对整个design的行为约束,这样导致的后果将是,最终timing收敛完成之后,行为跟实际design的行为不符,完全没有达到预期的timing约束程度,导致整个design失败。如果design如图5中所示,我们想在DFF/Q pin上正确的定义clock,需要加上-preinvert选项(-divide_by 2 -preinvert)。

图5 preinvert option示例

在图4,图5中的clock定义,上面讲到的都是如果采用-divide_by的方式如何正确的定义,那么能不能采用-edge的方式来定义呢?以图5为例,可以替换成-edge并且配合-edge_shift的方式来定义,其定义方式如图6所示。但是,此处需要注意,-edge_shift,其后面list列表中的数目要跟-edge中list数目完全一致,并且,-edge_shift后面list中的number可以为正,可以为负,如果为正,则表示右移,为负则表示左移,其是float类型的,表示右移/左移多少个时间单位。

图6 edge_shift option示例

图6中的定义,那么能不能直接用-edges {2 4 6}的方式呢?以及图4中的示例,能不能替换为-edges的方式定义呢?可以自己思考一下。

敲黑板,划重点

在此可以跟大家分享两条基本原则,有助于分析clock定义是否合理。采用create_generated_clock定义的clock,其一:继承的mater clock的edge一定要正确;其二:跟master clock之间的实际通路一定要物理上存在,并且要通。总结起来就是,clock定义要按照实际design来定义,不能想当然,如果在不清楚如何使用option时,可以先手画波形图,然后按照图再去选择option的使用。

-

分频器

+关注

关注

43文章

447浏览量

49874 -

触发器

+关注

关注

14文章

2000浏览量

61130 -

PLL电路

+关注

关注

0文章

92浏览量

6403 -

dff

+关注

关注

0文章

26浏览量

3417

发布评论请先 登录

相关推荐

Stm32_Clock_Init函数如何定义

介绍一下STM32L151的clock tree

基于Stm32_Clock_Init()函数的流水灯设计

什么是Clock Tree

探讨一下深度学习在嵌入式设备上的应用

请教一下各位标准单元库中clock buffer的设计很复杂吗

Determining Clock Accuracy Req

探讨软件定义未来医疗的新蓝图

怎样通过设置clock group来确认各个时钟之间的关系?

时序分析基本概念介绍<generate clock>

探讨下clock的基本定义(上)

探讨下clock的基本定义(上)

评论