误差矢量幅度(EVM)是广为使用的系统级性能指标,许多通信标准将其定义为用于无线局域网(WLAN 802.11)、移动通信(4G LTE、5G)等应用的合规性测试。除此之外,它还是一个极为有用的系统级指标,可通过简单易懂的值来量化系统中所有潜在损害的综合影响。

大多数射频工程师都会接受有关大量射频性能参数的培训,例如噪声系数、三阶截取点和信噪比。了解这些性能参数对整体系统级性能的综合影响可能极具挑战性。EVM不评估多个单独的性能指标,而是反映整个系统的概况。在本文中,ADI将分析较低水平的性能参数如何影响EVM,并研究一些将EVM用于器件系统级性能优化的实际示例。同时展示如何实现比大多数通信标准目标低15dB之多的EVM。

什么是误差矢量幅度?

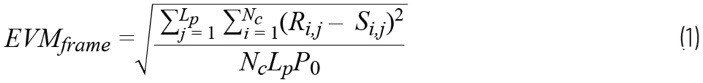

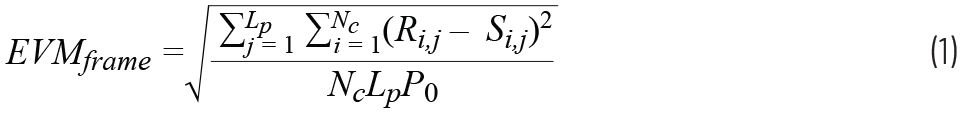

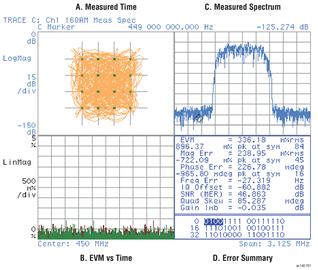

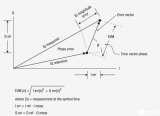

EVM是量化系统中所有信号综合损害的简单指标。采用数字调制的器件经常定义这个指标,可通过同相(I)和正交(Q)矢量图(也称为星座图)来表示(如图1a所示)。一般来说,计算EVM的方式是针对每个接收信号找到理想星座位置(如图1b所示)。通过计算接收信号的位置与其最接近的理想星座位置之间的所有误差矢量幅度的均方根(rms),可得出器件的EVM值。

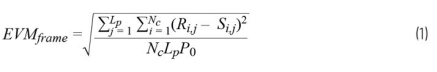

符合IEEE 802.11标准的EVM公式示例见方程式1。

其中:Lp为帧数,Nc为载波数,Ri,j为接收信号,Si,j为理想信号位置。

图1.(a)星座图和判定边界,以及(b)接收信号和理想信号位置之间的误差矢量。

EVM与给定系统的误码率(BER)密切相关。当接收信号远离目标星座点时,它们落入另一星座点判定边界内的概率会随之而增加。这会使BER变大。BER和EVM之间的一个重要区别是,发射信号的BER是根据发射的位模式计算的,而EVM则根据离信号最近的星座点和信号实际位置的距离计算的。在某些情况下,信号可能会跨越判定边界,并被赋予不正确的位模式。如果信号越靠近另一理想信号位置,则该信号的EVM可能会越好。因此,虽然EVM和BER密切相关,但这种关系可能不适用于信号失真水平极高的情况。

现代通信标准根据发射或接收信号的特征(如数据速率和带宽)规定了最低可接受的EVM水平。达到目标EVM水平的器件符合标准,而未达到目标EVM水平的器件则不符合标准。专门用于通信标准合规性验证的测试和测量设备通常会采用更严格的EVM指标,该指标可能会比标准制定的EVM指标低一个数量级。这使得测试和测量设备能在不使信号明显失真的情况下表征受测器件的EVM特性。

影响EVM的因素有哪些?

作为一种误差指标,EVM与系统内的所有误差源密切相关。为了量化所有损害对EVM的影响,可以计算它们使接收和发射信号失真的程度。下面ADI将分析几个关键损害(如热噪声、相位噪声和非线性)对EVM的影响。

白噪声

白噪声存在于所有射频系统中。当噪声是系统中唯一的损害时,可使用以下公式计算出相应的EVM:

其中SNR是系统的信噪比(单位:dB),PAPR是给定信号的峰均功率比(单位:dB)。请注意,SNR一般适用于单音信号。如果是调制信号,则需考虑信号的PAPR。由于单音信号的PAPR为3dB,如果波形具有任意PAPR值,则需从SNR值中减去3dB。

对于高速转换器(如模数转换器(ADC)和数模转换器(DAC)),方程式2可用噪声频谱密度(NSD)表示:

其中,NSD为噪声频谱密度(单位:dBFS/Hz),BW为信号带宽(单位:Hz),PAPR为峰均功率比,Pbackoff为信号峰值功率与转换器满量程之间的差值。通过该公式,可非常方便地使用NSD规范直接计算器件的预期EVM,该规范通常用于最先进的高速转换器。请注意,高速转换器器件也需考虑量化噪声。大多数高速转换器的NSD规范也涵盖量化噪声。因此,方程式3不仅代表热噪声,还代表高速转换器的量化噪声。

正如这两个方程式所强调的,信号的EVM与其总信号带宽、峰均比和整个系统的热噪声直接相关。

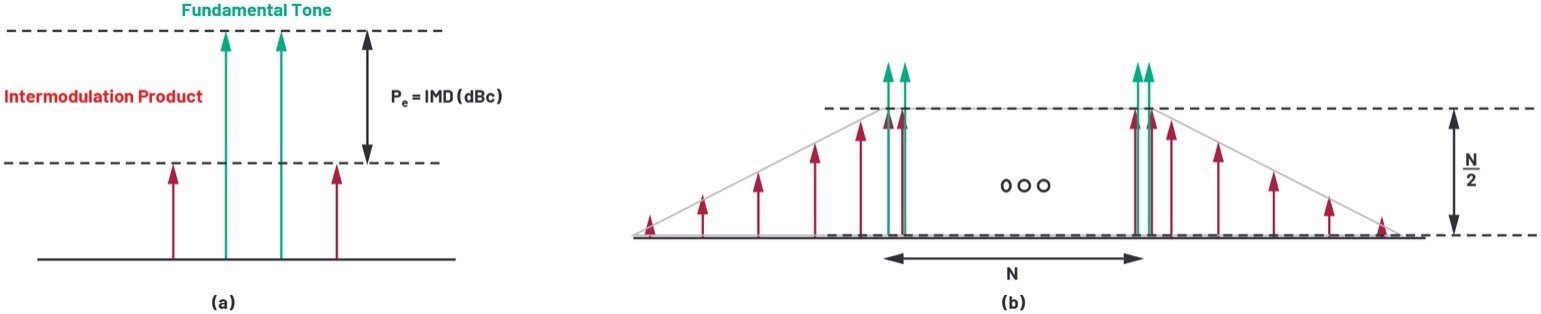

相位噪声如何影响EVM

相位噪声是影响系统EVM的另一种形式的噪声,是波形相位和频率的随机波动。所有非线性电路元件均会引入相位噪声。给定系统的主要相位噪声来源可以追溯到振荡器,如参考时钟、本振(LO)和采样时钟。多个振荡器(如数据转换器的采样时钟、用于频率转换的本振以及基准频率)会对系统的总体相位噪声产生影响。

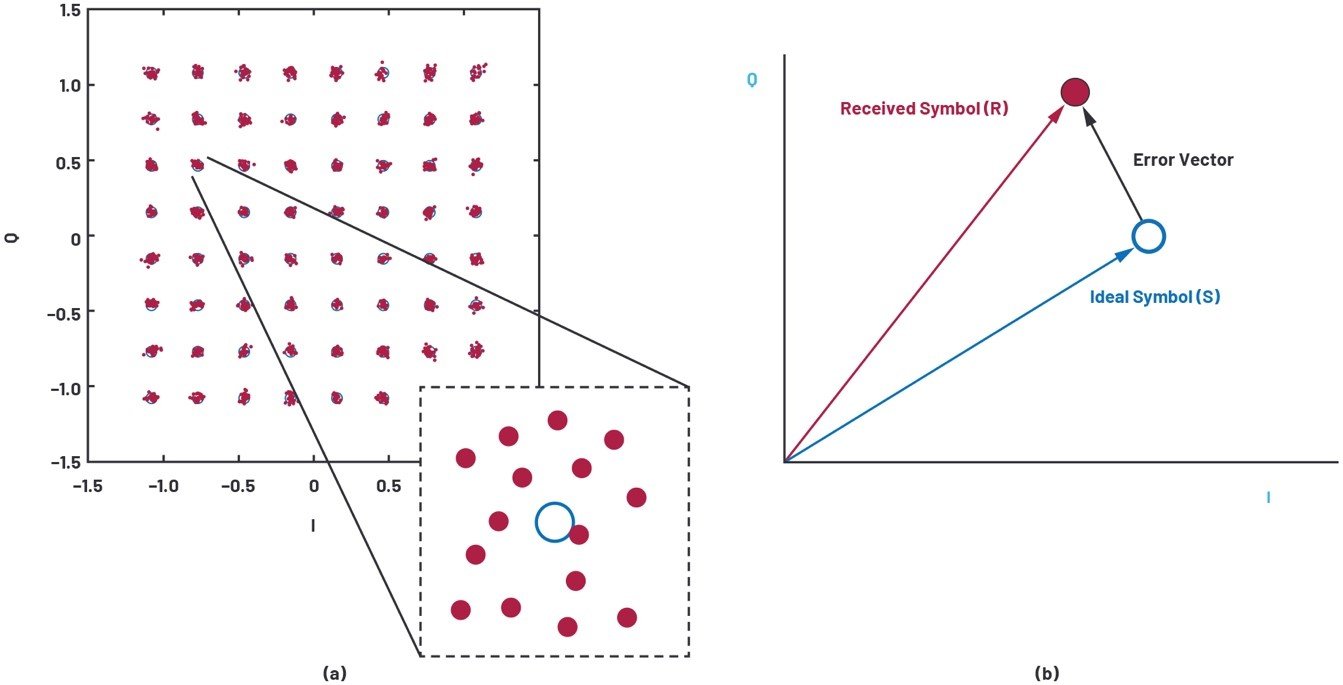

相位噪声导致的性能下降与频率有关。典型振荡器在其基本振荡频率(所谓的中心频率)下产生出大部分载波能量。一小部分的信号能量将在这个中心频率附近传播。特定频率偏移下1 Hz带宽内的信号幅度与其在中心频率下的幅度之比定义即为特定频率偏移下的相位噪声(如图2所示)。

图2.相位噪声

系统的相位噪声会直接影响系统的EVM。在整个带宽内对相位噪声求积分,可计算出系统相位噪声引起的EVM。对于大多数采用正交频域调制(OFDM)的现代通信标准,应从大约10%的副载波间隔开始对相位噪声求积分,直至达到总信号带宽时结束。

其中,L为单边带相位噪声密度,fsc为副载波间隔,BW为信号带宽。

大多数频率发生器件在低于2GHz的频率下出现低相位噪声,典型的积分抖动水平比标准中定义的EVM限值低几个数量级。但在更高的频率和更宽的信号带宽下,积分相位噪声水平可能会非常大,这可能导致EVM值显著变高。工作频率大于20GHz的毫米波(mmWave)器件通常会发生这种情况。要获得最佳的整体EVM,应计算整个系统的相位噪声,这将在“设计示例”部分详细讨论。

计算非线性对EVM的影响

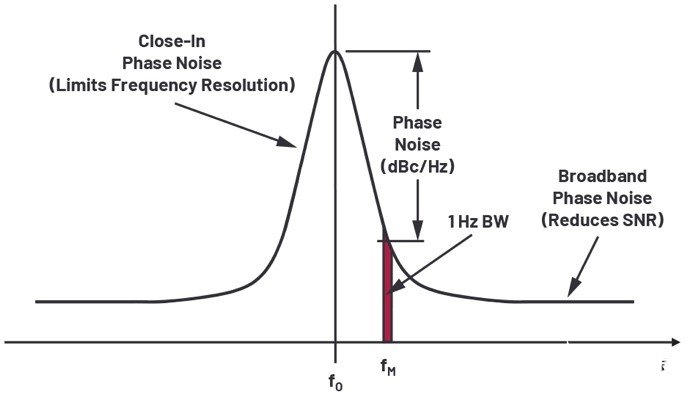

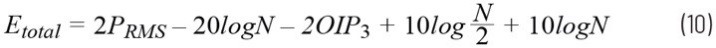

系统级非线性会导致可能处于信号带宽范围内的交调产物。这些交调产物可与副载波重叠,影响它们的幅度和相位。可计算出源自这些交调项的平均误差。让我们推导一个简单的公式来计算三阶交调产物引起的系统EVM。

图3.OFDM交调产物

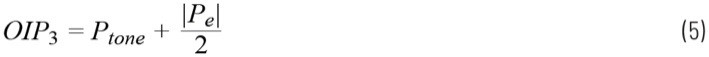

如图3a所示,双音信号将产生两个交调产物。交调产物的功率可通过下式计算:

其中,Ptone为测试音的功率,OIP3为输出三阶截取点,Pe为误差信号,表示基波和交调产物之间的功率差。

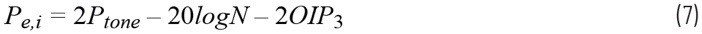

如果OFDM信号具有N个信号音(如图3b所示),则方程式6变为:

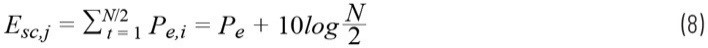

由于在每个副载波位置有N/2个交调产物重叠,因此可将方程式改写为:

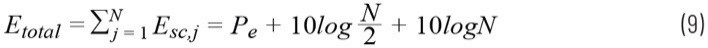

包括所有副载波位置在内的总误差为:

将方程式6代入方程式8,EVM可表示如下:

其中,PRMS为信号的均方根平均值,而C为一个常数(范围介于0dB至3dB之间,具体取决于调制方案)。如方程式11所示,EVM随着系统的OIP3的升高而降低。这与预期相符,因为OIP3越高,通常意味着系统更具线性。此外,随着信号均方根功率的降低,EVM随着非线性产物功率的降低而降低。

使用EVM优化系统级性能

典型系统级设计均始于级联分析,使用构建模块的低级别性能参数来确定使用这些模块构建而成的系统的整体性能。可用于计算这些参数的分析公式和工具均已非常完善。但许多工程师并未考虑如何正确使用级联分析工具来设计出经过充分优化的系统。

作为系统级性能指标,EVM为设计工程师优化系统设计提供了重要的参考。设计人员可以无需考虑多个参数,而只需轻松选择优化EVM均方根值,便能实现最佳系统设计。

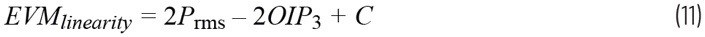

EVM浴盆曲线

下面可以从每个损害产生的EVM影响和输出功率电平考虑,将这些因素合并成单张图。图4显示了基于工作功率水平的系统典型EVM浴盆曲线。在低工作功率水平下,EVM性能主要由系统的噪声性能决定。在高工作功率水平下,系统的非线性会影响EVM。系统的最低EVM水平通常根据所有误差源(包括相位噪声)的组合来定义。

图4.EVM浴盆曲线,显示EVM随工作功率的变化

可通过方程式12归纳总EVM:

其中EVMWN为源自白噪声的EVM影响,EVMPhN为相位噪声影响,EVMlinearity为源自非线性失真的EVM。对于给定的功率水平,所有这些误差项的功率和表示了系统中的总EVM水平。

除方程式12外,系统的浴盆曲线在系统级优化中也非常有用,能够以组合的形式直观呈现出给定系统的所有损害。

设计示例

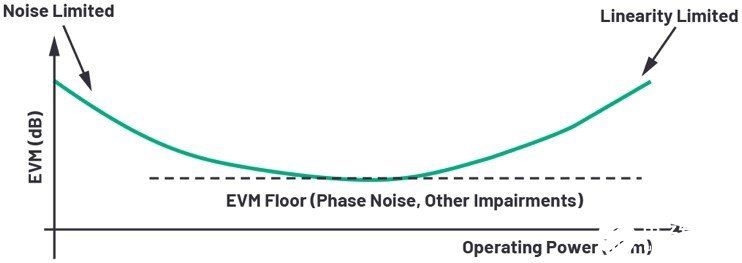

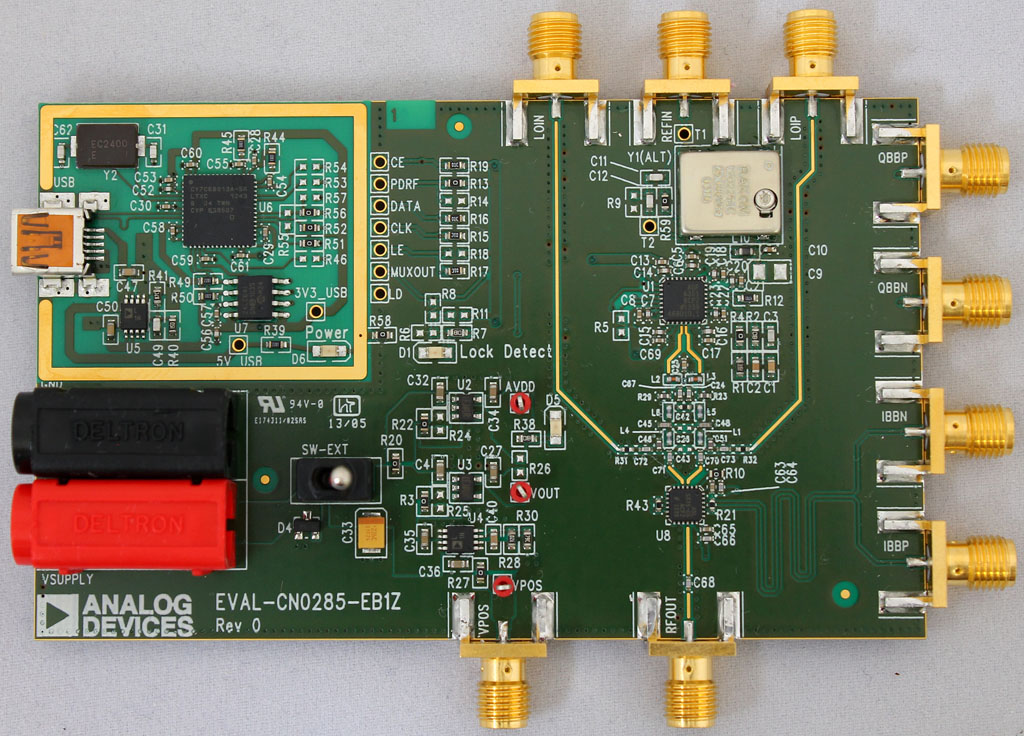

用EVM作为指标来设计一个实用的信号链。在本例中,ADI将使用RF采样DAC、毫米波调制器、毫米波频率产生器件和其他信号调理器件来设计一个毫米波发射器(如图5所示)。

图5. 毫米波发射器信号链

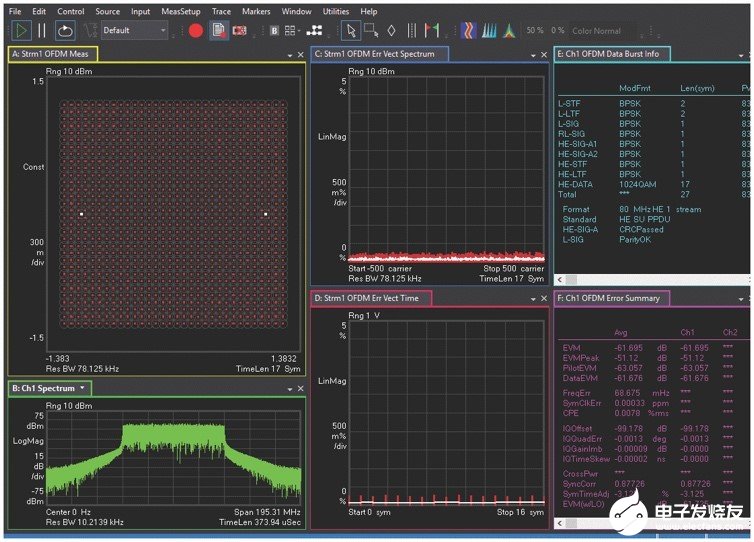

该信号链使用AD9082器件,该器件配备了采样速率分别为12GSPS和6GSPS的四通道DAC和双通道ADC。使用这些具有直接RF功能的转换器可使毫米波信号链的设计更具灵活性,性能无与伦比。图6显示了使用12位10GSPS模数转换器AD9213完成的AD9082的EVM测量值。这两个器件采用环回配置,产生的EVM水平低至-62dB,比标准限值低27dB。

该信号链还使用完全集成的毫米波调制器(ADMV1013),该调制器将传统信号链的多个子模块(如倍频器、正交混频器和放大器)集成到一个元件中。为了降低滤波复杂度,我们在该设计中使用了复数IF拓扑,从而向调制器的正交混频器馈入正交信号。这消除了上变频信号的一个边带,与双边带上变频操作相比,降低了滤波复杂度。

图6.使用AD9213的AD9082在400MHz中频下的典型EVM测量值(适用于80MHz带宽IEEE 802.11ax波形,采用1024 QAM调制)。

为了优化该信号链以获得最低EVM,可先分析系统级相位噪声,然后讨论噪声和线性度之间的权衡,最后整合所有构建模块。

通过最佳相位噪声预算改善EVM

如前所述,整个系统的相位噪声会限制毫米波频率下的整体EVM性能。为了确保将整体EVM降至最低,先分析每一级的相位噪声影响,以确保为该信号链挑选出最佳元件。

在该信号链中产生频率的元件是DAC(使用合成器提供时钟)和LO信号。总相位噪声可表示为:

其中,LTx为发射器的总相位噪声,ℓIF为DAC输出端的相位噪声,ℓLO为LO信号的相位噪声。

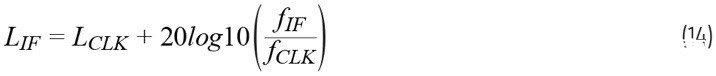

本例中使用的DAC (AD9082)具有极低的附加相位噪声。输出端的总相位噪声(即IF信号)可使用方程式14所示的简单公式计算:

其中,LCLK为时钟信号的积分相位噪声,fIF为DAC输出端的IF频率,fCLK为DAC的采样时钟。下面分析采样时钟和LO源的两个候选项,以确保挑选出相位噪声和复杂度最低的元件。

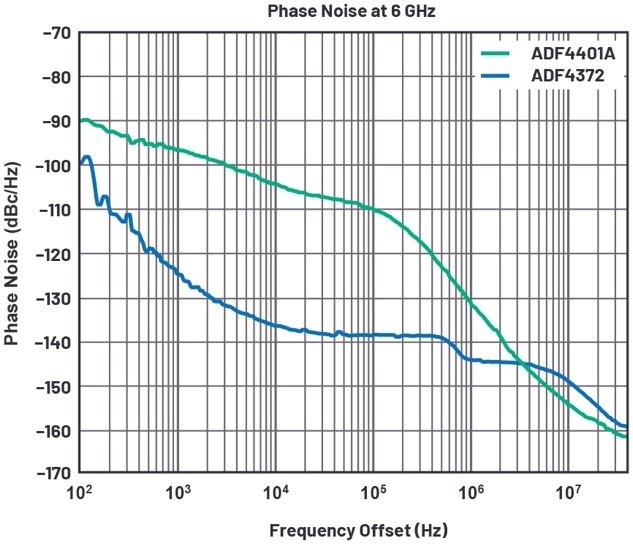

图7显示了该信号链两个主要频率合成器候选项的单边带相位噪声。使用6kHz至100MHz积分带宽对信号源的相位噪声求积分,可计算出5G NR波形的积分相位噪声(如表1所示)。

图7.时钟和LO源选项的相位噪声

表1.合成器的典型积分相位噪声测量值

| 元件 | 6GHz时的积分相位噪声(dBc/Hz) | 2GHz时的积分相位噪声(dBc/Hz) | 30GHz时的积分相位噪声(dBc/Hz) |

| ADF4372 | -54.6 | -64.1 | -40.6 |

| ADF4401A | -73.1 | -82.6 | -59.1 |

在该信号链的典型中频下,ADF4372和ADF4401A的积分噪声水平都极低。由于ADF4372所需的总印刷电路板(PCB)面积小很多,因此是为产生IF信号的RF转换器提供采样时钟的理想选择。但正如所料,ADF4401A器件固有的起始相位噪声较低,因此可选择作为信号发生器来产生LO信号。在30GHz时,其积分噪声比ADF4372器件低大约20dB。这种低积分相位噪声水平确保了LO信号的相位噪声不会限制整个系统的整体EVM性能。

利用方程式4,可按方程式15所示计算出由相位噪声引起的总EVMPhN:

相位噪声引起的这一EVM水平完全足以测量5G NR标准定义的信号(EVM水平约为-30dB)。

噪声和线性度之间的权衡

RF设计中最基本的权衡之一就是在整个系统的噪声性能和线性性能之间作出选择。针对这两个性能参数的其中一个进行优化通常会折损另一个参数的性能。当需要优化整个系统的性能时,系统级EVM分析是非常有用的工具。

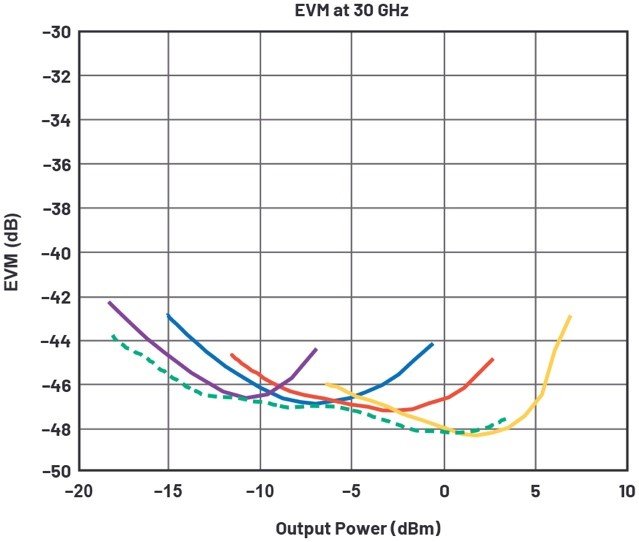

图8显示了针对之前构建的信号链在噪声和线性度之间作出的权衡。通过改变集成电压可变放大器(VVA)控制电压,得到了每条迹线。对于每条迹线,DAC的输出功率电平均已改变。请注意,EVM随着功率水平的升高而降低,原因是系统整体信噪比提高了。在某个功率电平之后,总信号路径的非线性开始导致EVM性能降低。针对给定VVA配置产生的EVM浴盆曲线非常窄。

图8.整个系统的噪声和线性度之间的权衡

幸运的是,通过调整VVA控制电压,可以过渡到另一条曲线,在这里整个系统的EVM较低。图8中的虚线表示使用ADMV1013的集成VVA可实现的系统级优化。优化后产生的浴盆曲线显著变宽,因此可在宽输出功率水平范围内实现超低EVM。

结论

在本文中,ADI讨论了作为系统级性能指标的EVM,以及如何通过EVM优化系统级性能。正如文中所述,EVM是许多系统级问题的良好指标,可测量的EVM是所有误差源的结果,可用于优化整体性能。同时已证明,使用最新的高速转换器和完全集成的毫米波调制器,可展示出仪器仪表级性能,还可以实现与目标通信标准相比低几个数量级的EVM。

-

ADI

+关注

关注

146文章

45819浏览量

249711 -

高速转换器

+关注

关注

0文章

27浏览量

11817 -

EVM

+关注

关注

3文章

864浏览量

41037

发布评论请先 登录

相关推荐

用于相邻信道功率比和误差矢量幅度测量的完整数字至射频发送器包括包括原理图和物料清单

矢量网络分析仪E8362B的误差来源及其校准-Agitkservice

矢量网络分析仪的误差来源于哪里?

宽带低误差矢量幅度(EVM)直接变频发射机

是德科技推出可实现实现极低的剩余误差矢量幅度的矢量网络分析仪

误差矢量幅度测量如何提高系统级性能

误差矢量幅度(EVM)测量怎样提高系统级性能

误差矢量幅度(EVM)测量怎样提高系统级性能

评论