本篇博文旨在提供发生 JESD204B 链路中断情况下的调试技巧简介。

其中提供了发生链路建链失败情况下需要收集的信息以及可能的原因。

需要收集的有助于调试的常规信息包括:

所使用的核是哪个版本?

出现何种类型的建链失败情况?

设计是否包含JESD RX、JESD TX和/或JESD PHY?

设计的模块框图是否可用?时钟方案是怎样的?

设计运行的数据速率是多少?

refclk 与核时钟频率是多少?

使用的子类 (Subclass) 是哪个?

有助于调试的文件包括:

XCI 文件

IP integrator 设计或 Tcl 文件,便于重新生成设计

仿真或硬件捕获的错误

参数基本信息:

M = number of converters

N = resolution of the converter

例如,四通道 ADC,resolution 为 14:M = 4;N = 14

N' = number of nibbles (calculated by dividing N by 4)

L = number of lanes

F: Octets per Frame

K: Frames per Multiframe

链路初始化问题:

以下列出了链路初始化问题的 5 个可能原因:

GT 初始化未完成:PLL unlock(PLL 解锁)或 GT reset done(GT 复位完成)未处于高位

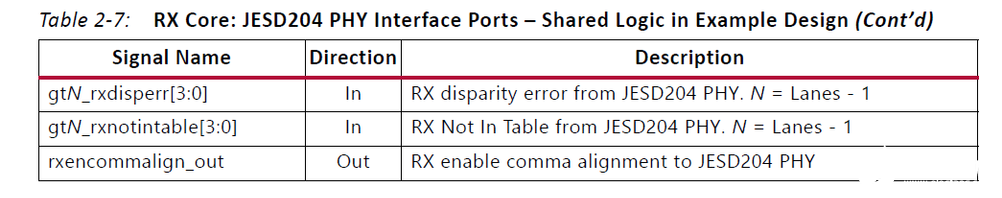

链路上存在错误(disparity 错误、not in table 错误、意外的 K 值)

未捕获 Sysref(请参阅以下时钟设置部分)

未接收到 4 个连续的 K28.5 字符。

TX 上设置的链路参数与 RX 上的参数不匹配。

同步丢失:

核因下列原因而断言 SYNC 有效:

完整(长)重新同步请求:

4 个连续位错误(disparity 错误或 not in table 错误)

4 个连续的意外 Kx.y 字符(rxcharisk 只能出现在帧末尾)

8 个连续的不匹配 (misalignment) 错误(多帧未对齐)

如果接收到单位错误或者意外的 Kx.y 字符,则会触发 Short SYNC 错误报告。通过在 Error Reporting RX 寄存器 0x034 处设置 SYNC 配置位,即可启用此错误报告。

千兆位收发器:

如果看到 8b10b 错误(disparity 错误或 not in table 错误),表示存在 GT 问题。

应执行以下检验:

1) 确认 GT refclk 正常。

2) 检查电源。

3) 检查眼图。

时钟设置:

所选时钟设置方案对于 JESD204 链路成功至关重要。JESD204 产品指南(PG066)包含建议使用的时钟设置方案。

强烈建议您使用本部分中提供的下列时钟设置方案之一。使用其它时钟设置方案可能导致设计失败。

如果链路建立时发生问题,请检查 MMCM 或 GT (QPLL / CPLL) 的锁定信号。

采用 Subclass 1 模式时,SYSREF 信号必须与核时钟同步,并且应从外部器件驱动,此外部器件用于为 TX 和 RX 生成 SYSREF。

在某些情况下,核时钟和参考时钟使用相同的时钟频率或时钟源可能更有利。但这有时可能不切实际。

因此,深刻理解对于参考时钟与核时钟所施加的限制以及系统级别的影响(例如,同步捕获 Subclass 1 或 2 确定性时延的 SYSREF / SYNC)就显得尤为重要。

请参阅(PG066)的“时钟”部分以获取更多详细信息。

复位:

掌握 JESD204 核所使用的复位有助于您正确开发自己的系统。

“系统复位”是异步复位,它将复位整个系统(核逻辑和收发器):在发射核上,此复位即为 tx_reset,在接收器核上则为 rx_reset。

AXI4-Lite 接口和配置寄存器不受这些复位信号的影响。

s_axi_aresetn 是为 AXI4-Lite 接口提供的独立复位信号,用于将配置寄存器复位为默认值。

只要对核参数进行了更改,就应将 AXI 核复位。

“软件复位”是通过 AXI4-Lite 接口提供的寄存器,用于为软件控制下的发射或接收逻辑数据路径触发数据路径复位序列。

配置寄存器不受此操作影响。使用此复位并不会复位 PLL。

“看门狗定时器复位”的工作方式与软件复位相同。如果需要,可使用寄存器访问来禁用看门狗定时器。

在正常系统操作下,赛灵思建议看门狗保持处于启用状态。如需了解更多信息,请参阅(PG066)的“看门狗时间复位”部分。

“AXI4-Stream 复位”:执行系统复位或软件复位时,rx_aresetn 或 tx_aresetn 输出将断言低电平有效,直至完成复位周期为止。

调试信号:

JESD204B RX 核包含调试状态寄存器(寄存器地址 0x03C),可用于调试链路信号。该寄存器内由 4 个位组成的每个组都对应于设计中的一条通道:

对于每条通道:

位 0 - 通道正在接收 K28.5(BC 对齐字符)

该位表示此通道上从收发器到核的输入为 0xBC 并且 charisk 已置位。

如果该位转至高位,那么您可继续查看“Code Group Sync”(代码组同步)阶段。

如果该位不转至高位,那么最好确定未能达成 SYNC 同步的原因。

例如,如果置位后,核并未在所有通道上都接收到 0xBC,可能表示部分 GT 处于故障状态,且输出无效。

下一步是检查 GT 并确保复位结构正确。

位 1 - 通道达成代码组同步 (CGS):

该位表示此通道已达成代码组同步。

位 2 - 检测到 ILA 开始:

该位表示已正确观测到从 0xBC 到 ILA 的转换。

看到该位置位表示此通道已开始 ILA 序列。

反之,则表示 ADC 行为不正常。请检查链路另一端,确认其设置是否正确。

位 3 - 检测到数据开始:

该位表示已正确观测到从 ILA 到数据的转换。

看到该位置位表示此通道已确认 ILA 序列结束,并且链路上用户数据已开始。

反之,则表示 ADC 行为不正常。

请检查链路两端的成帧参数,确认是否某一端设置错误。

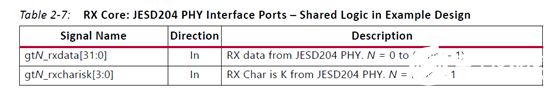

以下是 GT 输出。最好检查这些输出,确认是否接收到正确的 K28.5 或者是否接收到任何错误。

结论:

希望本文能在您遇到 JESD204B 链路中断时,帮助引导您遵循调试步骤逐步完成操作。

审核编辑:汤梓红

-

仿真

+关注

关注

50文章

4070浏览量

133551 -

pll

+关注

关注

6文章

776浏览量

135129 -

时钟

+关注

关注

10文章

1733浏览量

131445

发布评论请先 登录

相关推荐

构建JESD204B链路的步骤

在Xilinx FPGA上快速实现JESD204B

基于高速串行数字技术的JESD204B链路延时设计

JESD204B串行接口时钟的优势

jesd204b ip核支持的线速率

JESD204B协议有什么特点?

构建JESD204B链路的步骤

JESD204B协议介绍

如何构建JESD204B 有效链路

ADC16DX370 JESD204B串行链路的均衡优化

JESD204B使用说明

JESD204B链路中断时的基本调试技巧

JESD204B链路中断时的基本调试技巧

评论