1 单片机的低功耗设计技术

1.1 高集成度的完全单片化设计

将很多外围硬件集成到了CPU芯片中,增大硬件冗余。内部以低功耗、低电压的原则设计,这给单片机的低功耗设计提供了很强的支持。

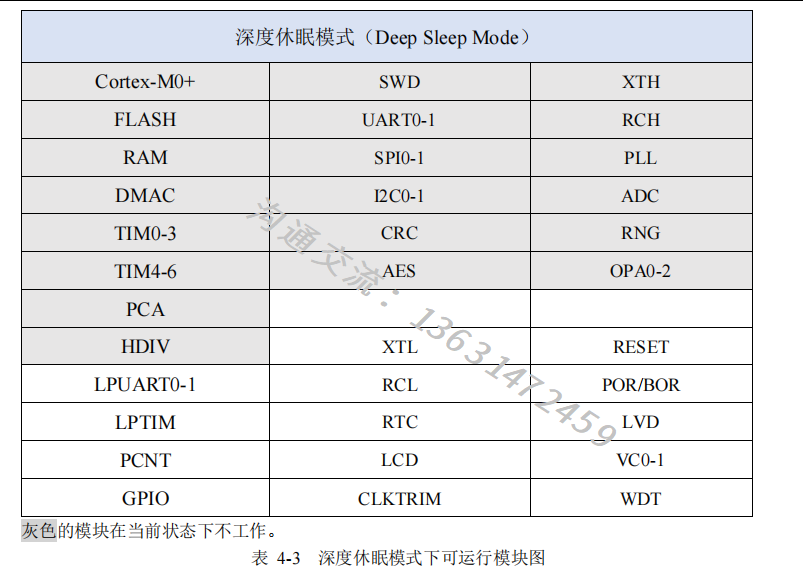

1.2 内部电路可选择性工作

通过特殊功能寄存器选择使用不同的功能电路,即依靠软件选择其中不同的硬件;对于不使用的功能使其停止工作,以减少无效功耗。

1.3 宽电源电压范围

先进的单片机芯片工艺特别决定了单片机在很宽的电源电压范围内部能正常工作。例如,NEC公司的 78K0和78K0S系列的单片机,可以在 1.8V~5.5V电源电压范围内正常工作。单片机供电电压范围的放宽,可以进一步拓宽单片机的应用领域,尤其是便携式或掌上型仪器或装置,可以放心地使用电池作为电源,而不必关心电过程电压曲线是否平衡、是否会影响单片机正常工作,更不必因电池供电而专门增加稳压电路,从而可减少大约1/3的功率消耗。

1.4 具有高速和低速两套时钟

系统运行频率越高,电源功耗就会相应增大。为更好地降低功耗,内部集成了两套独立的时钟系统,高速的主时钟和32.768kHz的副时钟。也可在满足功能需要的情况下按一定比例降低CPU主时钟频率,以降低电源功耗。在不需要高速运行的情况下,可选用副时钟低速运行,进一步降低功耗。通过软件对特殊功能寄存器赋值可改变CPU的时钟频率,或进行主时钟和副时钟切换。

1.5 在线改变CPU的工作频率

可根据CPU处理任务的不同,在外部振荡器不变的情况下,通过程序改变处理器时钟控制寄存器PCC的值,在线改变CPU的频率。CPU在几种不同频率下工作的电源功耗比较如图1所示。

1.6 后备功能

后备功能是为了进一步降低系统功耗。CPU用主时钟时有HALT(待机)模式和STOP(休眠)模式,用副系统时钟时有副时钟运行模式和HALT模式。如表1所示。

1.7 内部钟表定时器

NCE 单片机内部提供了时钟定时器,每隔0.5s产生一次中断。在系统处于休眠状态时,仍可定时被唤醒。对于单片机只须间歇工作、但又需要实时计时功能的应用场合,提供了非常有效的节能方法。CPU在不工作时可进入STOP模式或HALT模式,进入低功耗的后备功能状态。当时钟中断到来时,CPU回到正常工作状态,进入时钟中断处理程序做时钟更新处理,然后再进入后备功能状态。

2 单片机应用系统中的低功耗设计主要注意的问题

(1)系统中单片机以外的其它电路器件尽可能选用静态功耗低的器件,如选用CMOS电路芯片。

(2)外部设备的选择也要尽可能支持低功耗设计。

(3)设计外部中断唤醒电路,使单片机在等待时可进入休眠模式或待机模式,需要时由外部中断信号唤醒。

(4)设计外部器件的电源控制电路,使外部器件或设备在不工作时关断供电,减少无效功耗。

(5)设计充分利用系统低功耗特点的软件。

3 在线改变CPU的时钟频率以降低功力量的C语言程序举例

CPU在不需要高速运行时,可设置在较低的时钟频率下工作,在运行过程中可根据需要在线改变CPU的时钟频率。下面是一个通过按键产生外部中断信号改变NCE单片机μPD780058的CPU时钟频率的程序,它使CPU在主、副时钟切换运行。通过I/O口P6的位0引脚连接1个LED小灯,每按下一次按键就使CPU的时钟频率改变。在主时钟和副时钟频率下工作时,用同样的软件延时程序控制小灯点亮的时间,以此观察CPU的运行速度。

低功耗单片机的应用使电子产品、控制系统更符合当今时钟的要求,达到便携、低功耗和高可靠性。加之用高级语言(如C语言)对单片机进行开发的工具日臻完善。更为快速高效的开发应用提供了良好的条件和环境。低功耗的节能单片机应用系统将会带来很好的社会效益和经济效益。

审核编辑:彭菁

-

单片机

+关注

关注

6034文章

44554浏览量

634561 -

cpu

+关注

关注

68文章

10854浏览量

211563 -

软件

+关注

关注

69文章

4921浏览量

87383 -

定时器

+关注

关注

23文章

3246浏览量

114713 -

电路器件

+关注

关注

0文章

5浏览量

5287

发布评论请先 登录

相关推荐

单片机应用系统中的低功耗设计主要注意的问题

单片机的低功耗设计技术及其相关注意问题介绍

浅谈低功耗单片机系统的设计

单片机低功耗

单片机的低功耗设计技术及注意问题

单片机的低功耗设计技术及注意问题

评论