在HLS中用C语言实现8192点FFT,经过测试,实验结果正确,但是时序约束不到100M的时钟,应该是设计上的延时之类的比较大,暂时放弃这个方案,调用HLS中自带的FFT库(hls:fft)hls_fft.h。实际上,在HLS中调用该库实现FFT,其实是Vivado中的那个FFT核实现的,但是HLS中的配置和给定输入输出数据比较方便,并且对其外部封装其他类型的总线接口非常容易。

1.hls_fft.h初探

在HLS中打开示例例程 fft_single ,注意以下几点:

(1)默认设定

【1】输入数据和输出数据的格式固定,必须采用16位定点复数数据,其中1bit表示整数,其他的表示小数部分,即输入数据范围 —1 ~ 1,输出也是 —1 ~ 1;

【2】结构类型为流水线型;

【3】默认点数1024点,当不是这个点数时,除了修改头文件的点数,还需要修改config里的参数才能重新配置IP核;

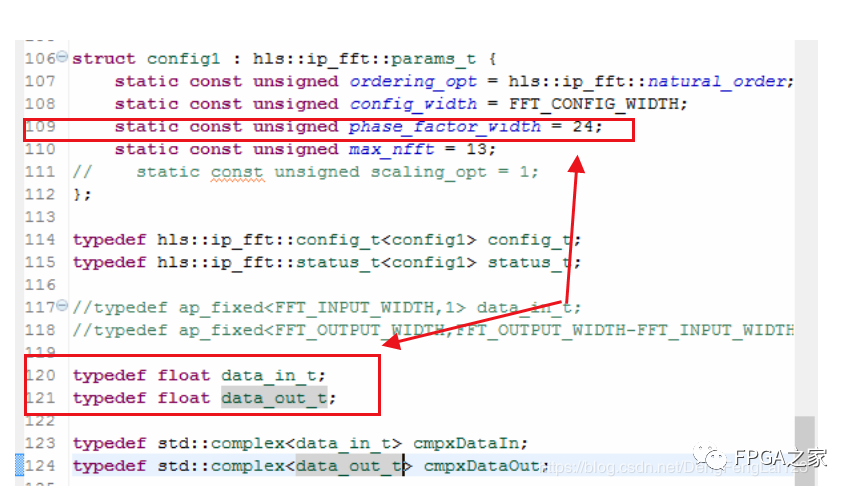

【4】默认输入输出16位定点,相位因子16位,如果需要改成浮点数输入输出,需要更改相位因子为24或25位,并且在config里面更改IP核的配置;

【5】HLS中的FFT的IP库只处理复数类型complex的FFT数据。

【6】Xilinx FFT IP块只对复数类型数据进行操作。尽管可以对把所有虚部都设为0的复数进行FFT,但是通过预处理数据可以更有效地执行FFT。

【7】HLS需要bit-reverse命令数据块后端,所说的自然顺序和一个O (N)转换适用于FFT输出提取的频谱数据N-point真实数据集。注意,第一个输出两包第0个和512(纯粹的)分别输出频谱数据的实部和虚部。

【8】设计是完全流水线,流设计高吞吐量;用于数据的连续处理,但具有节流功能(如果输入停止,则停止)。

【9】AXI4-Stream接口用于连接IP Integrator (IPI)中的所有块。

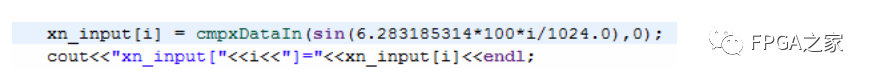

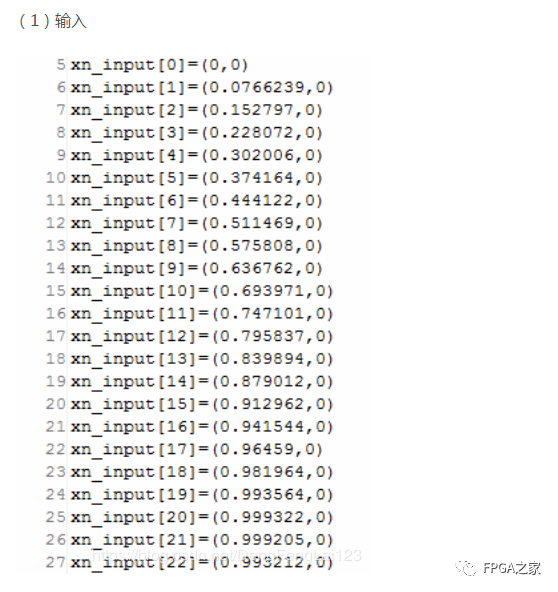

(2)在testbench中自己给输入信号进行测试,先给定一个正弦信号,注意下面的赋值,在2016.2版本是可以直接给复数的实部和虚部赋值的,但是2018.2这种方式会报错,需要采用下面的赋值函数来给一个复数赋值

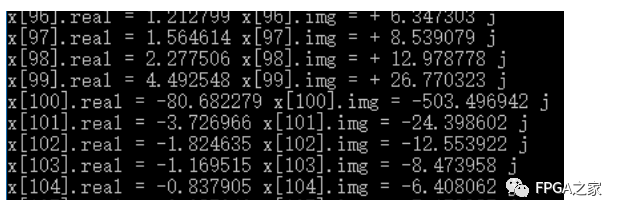

(3)scale放缩因子的设定 如果不设置放缩因子,输入上述 —1 ~ 1的正弦信号后,输出结果应该为

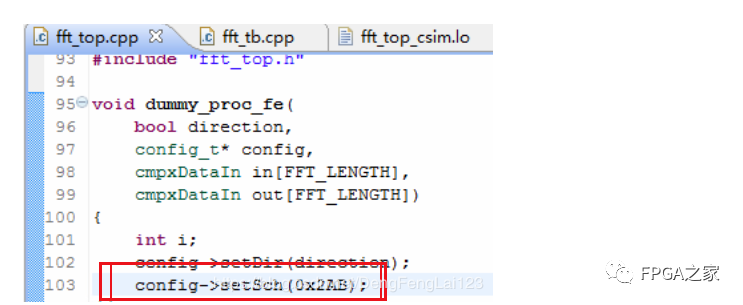

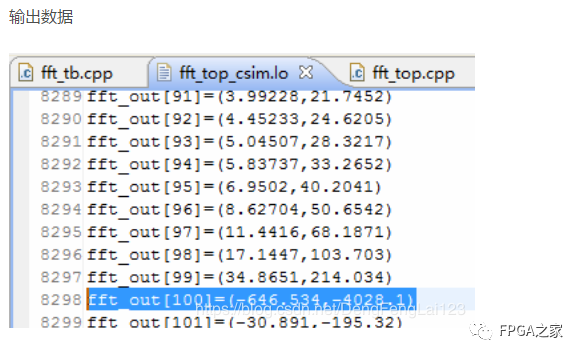

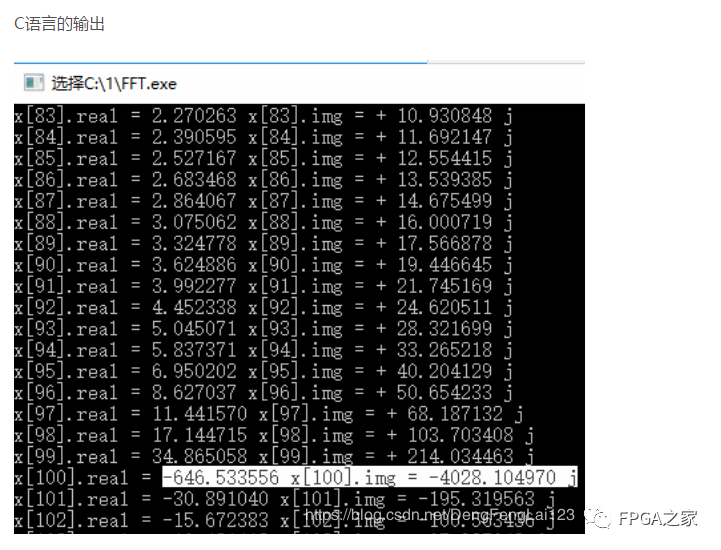

可以看到,最大值在x[100]处,虚部已经到-503级别,不符合输出数据的要求,在此过程中,需要对数据按照FFT的级数缩放,如下图所示,示例中设置1024点的FFT的放缩因子为0X2AB,即 10 10 10 10 11,按照每2bit合在一起,即为 2 2 2 2 3,依次相加为(2+2+2+2+3)=11,放缩倍数为2^11=2048。

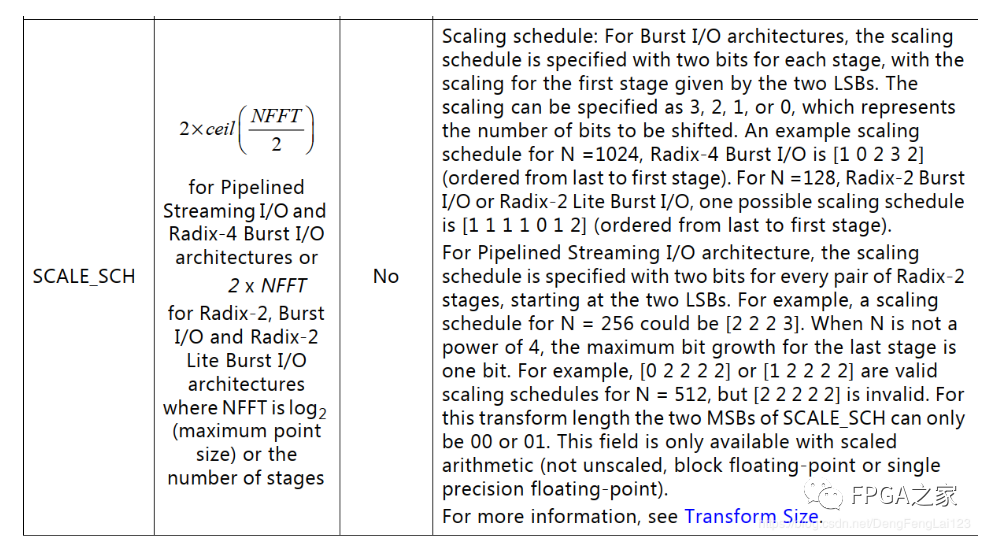

具体scale的设置详见PG109,翻译过来就是:

对于突发I/O架构,每个阶段的扩展调度由最低位的两个LSBs指定,第一个阶段的扩展调度由两个最低位LSBs指定。缩放可以指定为3、2、1或0,表示要移位的数目。例如:

【1】对于N =1024, Radix-4突发I/O是[1 0 2 3 2](从最后一级开始排序)

【2】对于N =128, x-2突发I/O或Radix-2 Lite Burst I/O,一种可能的扩展计划是[1 1 1 1 1 0 1 2] (从最后阶段到第一阶段排序)。

对于流水线并行I/O架构(示例默认使用流水线型),每个Radix-2阶段(从两个LSBs开始)都使用两位指定伸缩因子。例如:

【4】N = 256的缩放调度可以是[2 2 2 3]。当N不是4的幂时,最后阶段的最大位增长为1位。例如,[0 2 2 2]或[1 2 2 2 2]对于N = 512是有效的扩展调度,但是[2 2 2 2 2]是无效的。对于这个转换长度,SCALE_SCH的最高位的两个MSB只能是00或01。此字段仅适用于按比例缩放的算术(不包括未缩放unscaled、块浮点或单精度float)。

2.更改配置

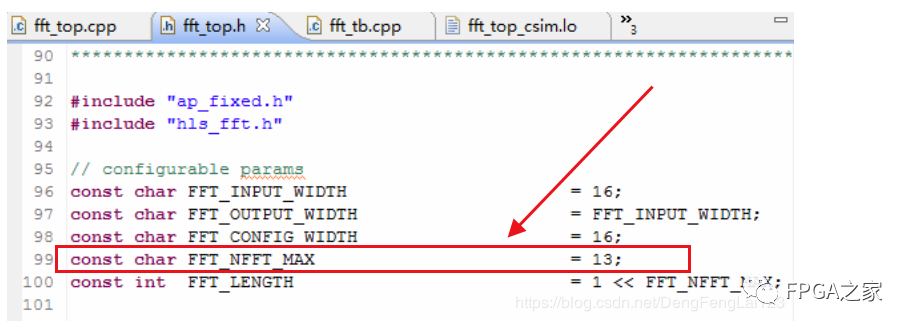

(1)改成8192点FFT(2^13)

【1】更改最大支持点数FFT_NFFT_MAX=13,这时候FFT_LENGTH也随之改变,效果为该FFT支持最大8192点(当设置为最大支持8192点时,4096/256等比8192小的点数也是支持的),并且本次运行点数时8192点。

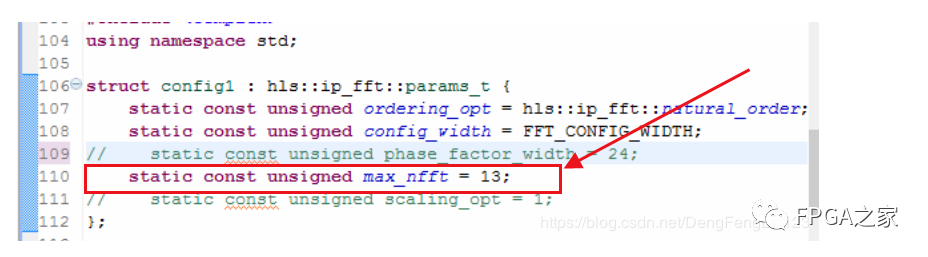

【2】修改config配置信息,将修改的点数写进fft的配置,如果没有110行的修改,那么实际上还是执行的1024点的FFT。

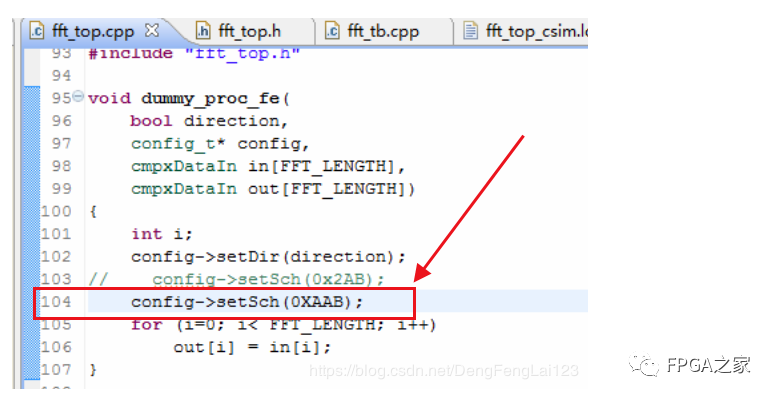

【3】修改放缩因子为0XAAB(8192点FFT,缩小8192倍,一般多少点设置多少倍,然后看overflow信号是否指示数据溢出,若溢出,则继续增大缩放因子)

此后点击运行,得到的结构范围在 —1 ~ 1之间,将所有数据*8192,得到正常的数据,但是,因为前面的放缩实在每一级上的累计放缩,所以存在较大的误差累积,通过和C语言double型正常未放缩执行的代码对比,发现在输出数据较小的地方误差非常大,基本可以看成是错的,在数据较大的地方,比如本例的100Hz的sin信号,在输出xk_output[100] 处与实际结果误差很小。

3.更改输入输出为float型,提高精度

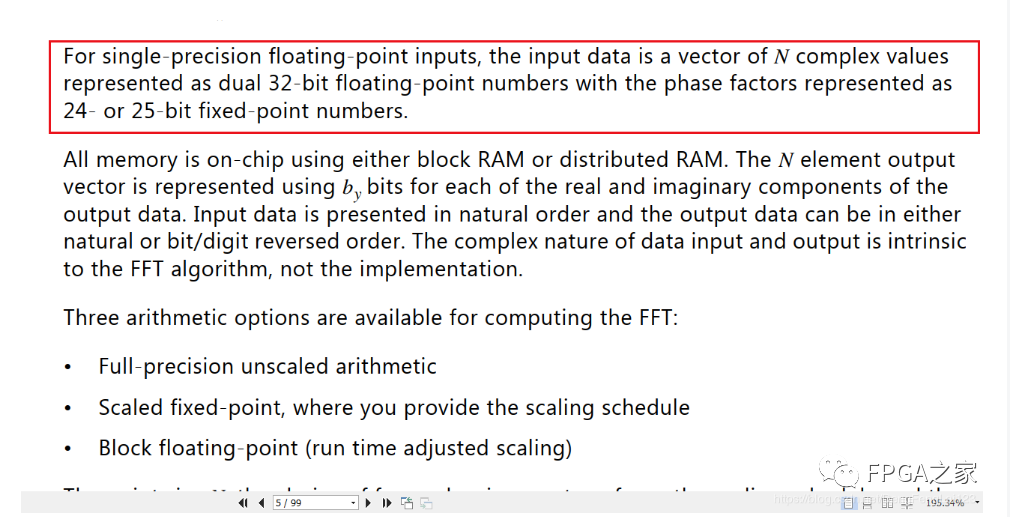

对于单精度浮点型输入,输入数据时N维复数向量(双32位浮点数),相位因子必须是24或者25位的定点数(PG109文档)。

4.结果

审核编辑:汤梓红

- FPGA

+关注

关注

1620文章

21468浏览量

597936 - FFT

+关注

关注

15文章

428浏览量

58948 - 时钟

+关注

关注

10文章

1650浏览量

130829 - C语言

+关注

关注

180文章

7561浏览量

133274 - HLS

+关注

关注

1文章

128浏览量

23876

原文标题:FPGA实现OFDM通信——FFT与IFFT——调用HLS的FFT库实现N点FFT(hls:fft)

文章出处:【微信号:Hack电子,微信公众号:Hack电子】欢迎添加关注!文章转载请注明出处。

发布评论请先登录

相关推荐

FPGA实现OFDM通信——FFT与IFFT应用实现

第29章 ST官方汇编FFT库实现IFFT

第32章 实数FFT的实现

HLS中FFT的反向输入算法不能实现

2048点FFT在TMS320C240x定点DSP上的实现

fft原理及实现

调用HLS的FFT库实现N点FFT(hls:fft)

调用HLS的FFT库实现N点FFT

调用HLS的FFT库实现N点FFT

评论