来源:EETOP

作者:Daniel Payne

移动电话技术的进步不断挑战极限,要求SoC在提供不断提升的性能的同时,还能保持较长的电池续航时间。为了满足这些需求,业界正在逐步采用更低的技术节点,目前的设计都是在5纳米或更低的工艺下完成的。在这些更低的几何尺寸下设计和验证时钟带来了越来越多的复杂性和验证挑战。在这种快速发展的形势下,必须重新评估当前的时钟验证方法,以确保最佳的时钟性能和可靠性。

现有的时钟方法主要依赖静态时序分析 (STA) 作为独立解决方案或更高级的方法,将 STA 与 SPICE vwin 器结合起来分析关键路径。此流程需要 CAD 部门的参与来建立流程和严格的方法来产生准确且及时的结果,但即便如此,对于较低工艺节点的 SoC 级时钟信号,仿真可能缺乏容量和/或精度要求。而且,关键路径的识别很大程度上依赖于工程师的判断和经验。这种方法会导致不必要的guard-banding,从而使宝贵的时序裕度未被利用,限制了整体性能。

在 7nm、5nm 和 3nm 工艺节点,晶体管和互连尺寸均减小,从而导致对各种设计和工艺相关问题的敏感性,例如轨到轨故障和时钟信号中的占空比失真。

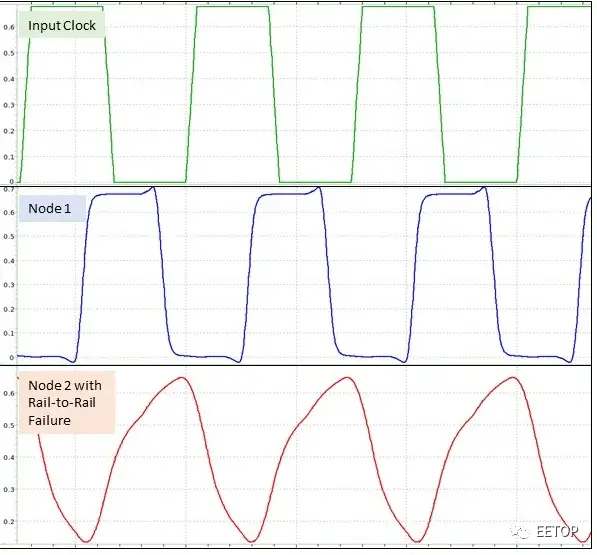

轨到轨故障(Rail to Rail Failure)

如果时钟网络的驱动器较弱、互连较长且电容负载较大,则可能会导致插入延迟增加,最坏的情况会导致轨到轨故障。在轨到轨故障中,时钟上的电压电平根本达不到 VSS 和 VDD 电平。单独运行 STA 不会检测到这种故障机制,因为 STA 在特定电压阈值下测量时序。

时钟频率的增加会减少时钟周期,从而缩短时钟达到电源轨电压电平的时间窗口。电压缩放还使时钟信号更容易受到轨到轨故障的影响,因为电源和 Vth 之间的间隙较小会导致非线性操作增加,从而降低驱动强度。即使 Vth 的工艺变化、晶体管 W 和 L 变化或寄生电容也会导致轨到轨故障。本地电源电平会因 IR 压降效应而反弹,从而降低时钟信号中的信号电平和时序。

时钟轨到轨故障检测

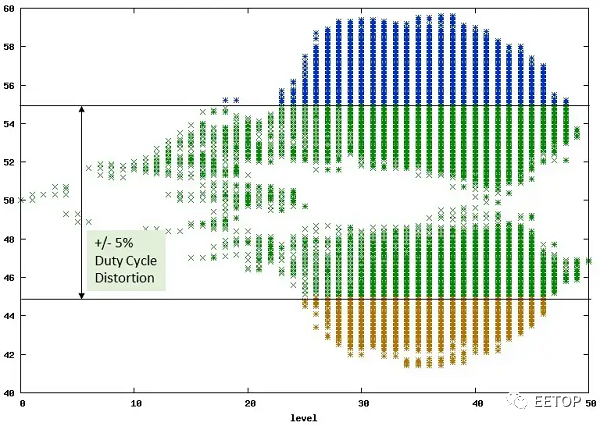

时钟占空比失真

当时钟信号通过一系列具有不对称上拉和下拉驱动强度的门传播时,会导致占空比失真(DCD)。时钟的理想占空比是 50% 低脉冲宽度和 50% 高脉冲宽度。增加时钟频率会加剧时序不平衡并导致 DCD 等信号完整性问题。时钟互连受到电容效应和电阻效应的影响,这些效应会改变上升时间和下降时间的转换速率,延迟时钟并导致不对称,从而使 DCD 效应更加明显。工艺变化直接改变互连,增加电路时序的不平衡,增加 DCD。

时钟占空比失真

对于具有不对称 PVT 角的工艺节点,DCD 变得更加明显。STA 工具的结果主要关注插入延迟,因此报告 DCD 和最小脉冲宽度 (MPW) 的准确性较低。

转换速率和过渡失真

在较低的工艺节点,寄生互连具有更明显的电阻屏蔽和电容耦合,降低了转换速率和时钟沿转换。STA 工具使用简化的互连寄生模型,该模型可能会低估时钟信号的衰减。

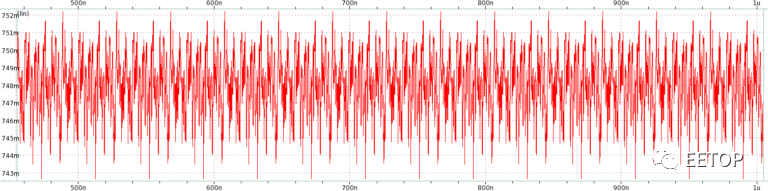

电源引起的抖动

供电网络 (PDN) 中的噪声会影响时钟时序,产生抖动,从而影响时钟性能。当电源经历波动或噪声时,它会引入电压变化,直接影响时钟信号的稳定性和完整性。电源引起的抖动可能会导致时钟信号出现定时错误,导致它们比预期提前或晚到达。这可能会导致建立和保持违规,从而导致时钟中潜在的功能故障。增加的抖动还会降低时序余量,使设计更容易受到时序违规和潜在性能下降的影响。STA 工具主要侧重于基于电路的静态表示来分析设计的时序行为,而不能分析抖动。设计人员通常使用抖动效应的近似值,

电源噪声

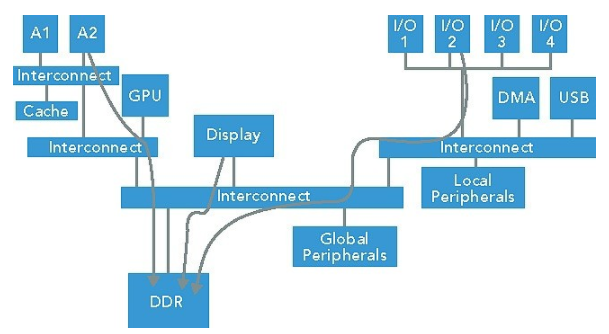

使用时钟网格和主干的拓扑

网格和脊柱架构,特别是在 7 纳米及以下技术节点,可以提供显著的优势,包括增强的信号完整性以及功率和面积效率。网格和脊柱结构为路由时钟信号提供了规则且结构化的框架,减少了较低技术节点工艺变化增加的影响,提高了信号完整性并减轻了时钟偏差、抖动和噪声等问题。此外,网格和脊柱架构允许优化时钟信号的路由。

电路仿真是验证网格和脊椎的唯一准确方法,但大多数商业 SPICE 模拟器无法处理如此大的网格的容量。在没有充分、快速和准确的验证方法的情况下设计具有网格和脊柱的较低技术节点时钟可能是一个危险的提议。

概括

移动设备需要移动处理器,而它们往往推动着 IC 工艺技术的前沿发展。及时实现 PPA 目标对于移动 SoC 的成功至关重要。在 7 纳米及以下技术节点,必须采用新的时钟验证方法。如果不采用这种方法,就会增加保护带,从而导致面积和功率要求的增加。最重要的是,保护带的保守性质,留下了宝贵的性能。

审核编辑:汤梓红

-

驱动器

+关注

关注

52文章

8226浏览量

146245 -

soc

+关注

关注

38文章

4161浏览量

218152 -

时钟

+关注

关注

10文章

1733浏览量

131445 -

SPICE

+关注

关注

6文章

182浏览量

42563 -

模拟器

+关注

关注

2文章

874浏览量

43207

原文标题:移动SoC的时钟验证

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何设计和验证SoC

SoC设计与验证整合

SoC验证平台的FPGA综合怎么实现?

SoC验证未来将朝什么方向发展?

SoC芯片验证技术的研究

SoC验证环境搭建方法的研究

基于FPGA的验证平台及有效的SoC验证过程和方法

适用于复杂SoC的软件定义验证和验证环境

SoC互连的功能和性能验证

为什么SoC验证一定需要FPGA原型验证呢??

为什么SoC验证一定需要FPGA原型验证呢?

移动SoC的时钟验证

移动SoC的时钟验证

评论