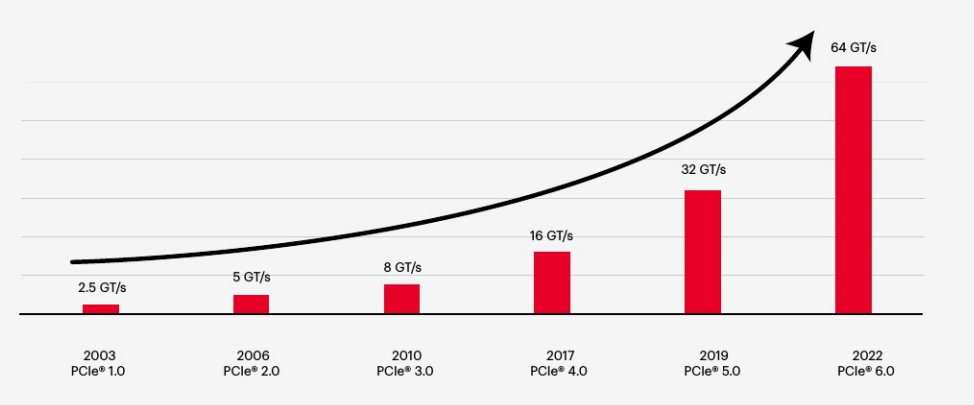

自2003年推出以来,PCIe发展至今已经从最初的1.0升级到了6.0,在上一篇文章中为大家介绍了PCIe基础知识:《什么是PCIe?》,本文则为大家简单介绍一下PCIe标准的演进历史以及各代PCIe标准之间的主要差异。

PCIe 3.0

PCIe2.0的传输速率为5 GT/s,但由于8b/10b编码方案的开销占比为20%,因此单lane的传输带宽为4Gb/s。PCIe 3.0及以后的版本使用更高效的128b/130b编码,将开销占比降低到了1.5%。

通过减少开销占比,PCIe3.0的单lane传输带宽相比PCIe2.0翻倍,达到8 Gb/s,同时保持了与PCle 2.0版本软件和机械接口的兼容性。由于完全向下兼容,PCIe 3.0为客户端和服务器配置提供了与PCIe 2.0相同的拓扑结构。

PCIe1. x和2.x卡可以无缝地插入支持PCIe 3.0的插槽中,反之亦然,支持这些配置以协商的最高性能水平运行。PCIe 3.0规范包含了Base和CEM(卡机电)规范,其中基本规范里的电气部分定义了集成电路(IC)级的电气性能,并支持8 GT/s信令。

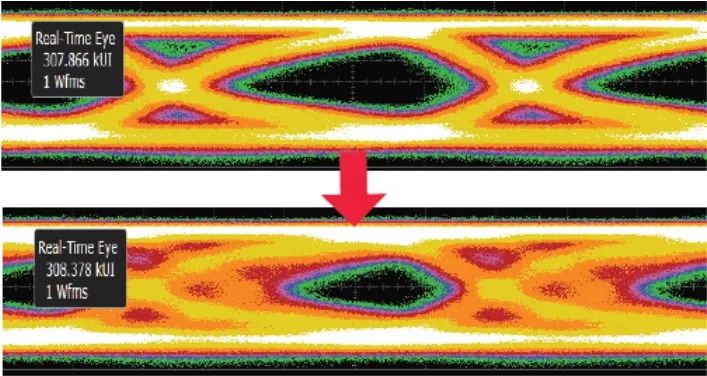

眼图(Eye Diagram)是一种通信领域中常用的时域分析工具,它可以用来评估数字通信系统中的信号完整性和传输质量(因为示波器显示的图形很像人的眼睛,因此被称为“眼图”)。由于PCIe的传输速率随着标准的迭代而增加,信号质量也会受到影响。如下图中的眼图闭合所示,通道长度越长信号质量也会越低,随着速度和信道距离的增加,物理层的验证测试更具挑战性。PCIe 3.0中8 GT/s的速度严重降低了接收器的信号,这将在示波器上以眼图闭合的形式出现(不均衡)。为了实现准确的通信,发送端和接收端需要就构成1和0的电平达成均衡,并采用诸如均衡和去加重等技术,使接收端清晰地看到数据。

PCIe3.0标准增加了接收器均衡和发送器去加重点,这对于能否实现8 GT/s及以上的速率至关重要。均衡可以在发送器、接收器或同时在两者中。PCIe 1.x和PCIe 2.x指定了一种简单的均衡形式,称为发送器去加重。去加重减少了接收器接收到的低频能量,均衡则降低了高频时更大的信道损耗影响。

接收器均衡的实现需要各种类型的算法,最常见的两种是线性反馈和决策反馈(DFE)。发送器去加重均衡发生在发送器,而DFE预加重发生在接收器。接收器均衡也可以包括与DFE相结合的连续时间线性均衡(CTLE)。

为了提高发送端和接收端之间的传输距离,PCIe 3.0引入了一个主动均衡适应过程,接收器可以调整发送器的前置尖头信号和去加重,以实现最适合自己的特定传输线的均衡性能。该性能需要全新的物理层测试,即接收器和发送器的链路均衡测试。链路均衡接收器测试的目的是检查接收器是否可以在最坏的应力条件下调整其链路的发送器均衡,而链路均衡发送器测试的目的是检查发送器是否按照链路的接收器的请求在物理上和逻辑上执行更改。

PCIe 4.0

PCIe4.0标准在PCIe 3.0上线7年后于2017年推出。与前一代相比,PCIe 4.0将传输速率从8 Gb/s提高至16 Gb/s,并与前几代技术从软件到时钟架构再到机械接口充分兼容。

从协议和编码的角度来看,PCIe 4.0与PCIe 3.0有许多共同点,包括128/130位编码。乍一看,PCIe 4.0与PCIe 3.0的共同点相较PCIe 3.0与PCIe 2.0的共同点更多。但是,当提高设备速度时,会自动通过相同的通道发送更高的频率。电信号传输过程中链路中的电阻会导致插入损耗或衰减,并随着频率的提高而增加。

在16 GT/s时,PCIe 4.0信号在典型的FR4通道(最常见的印刷电路板材料)中衰减显著。因此,为确保PCIe 4.0设计的信号完整性需要额外的测试,原因是16GT/s(PCIe 4.0)的信号损失比8 GT/s(PCIe 3.0)的信号损失要大得多。PCIe 4.0在规范中增加了计时器部分以扩展通道的范围,并特别增加了系统的复杂性测试。

即使测试复杂度增加,8 GT/s的PCIe 3.0测试次数也高于16 GT/s的PCIe 4.0测试次数。这是因为PCIe 3.0需要测试三种不同的通道场景:即短、中、长,而PCIe 4.0仅测试长通道场景即可。

与PCIe 3.0一样,PCIe 4.0有时也被称为“闭眼”规范。这意味着即使你有一个完美的发送器,以及一个基本零抖动的发送器,当你把发送器连接到一个频道时,符号间的干扰会迫使“眼睛”闭上。能否成功传输PCIe 4.0信号,取决于接收器的均衡策略能否将“眼睛”打开。

当支持16 GT/s的PCIe 4.0设备链接到另一个支持16 GT/s的PCIe 4.0设备时,链路均衡有两个步骤。首先,以8 GT/s的速度建立链接,如果成功,链路均衡过程将再重复一次,以达到16 GT/s的速率。

对于PCIe 4.0,设计人员应该评估其系统的性能变化耐受度。了解性能变化是必不可少的,因为信号性能因卡而异。这些差异会导致信道损耗、串扰和信道不连贯的增加,从而导致更多的系统噪声、抖动性能的恶化和信号闭眼。

PCIe 5.0

PCI-SIG于2019年5月发布了PCIe 5.0规范,将传输速率提高一倍,达到32 GT/s,同时保持低功耗和与前几代的向后兼容性。PCIe 5.0承诺通过x16配置达到128 GB/s的吞吐量,在数据中心可实现400GE的速度。

PCIe5.0和400GE的速度共同支持人工智能(AI)、机器学习、游戏、视觉计算、存储和网络等应用。这些进步使5G、云计算和超大规模数据中心的创新得以推动。

PCIe5.0标准是在4.0的基础上做了一个相对简单的扩展。它采用与PCIe 4.0相同的Tx和Rx测试方法,以及类似用于校准接收器应力抖动测试的“眼睛”宽度和高度的方法。新标准进一步降低了延迟,并兼容了长距离应用的信号损失。PCIe 5.0使用128b/130b编码方案,该方案在PCIe 3.0和兼容的CEM连接器中首次亮相。

PCIe5.0中的新功能是均衡旁路模式,能实现从2.5 GT/s直接到32 GT/s的训练,可加快链路初始化速度,这有助于在发送器、信道和接收器条件的系统(如嵌入式系统)中减少链路启动时间,为32 GT/s的链路均衡测试提供了一条新的训练路径。

一般来说,除了需要实现速度提升,或者实现电气更改以提高信号完整性和连接器的机械强度之外,规格变化很小。

PCIe 6.0

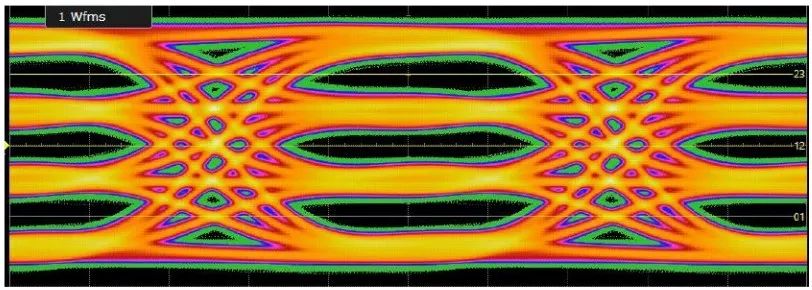

PCI-SIG于2022年1月发布了PCIe 6.0规范。PCIe 6.0技术是第一个使用脉冲幅度调制4级(PAM4)信号编码的PCI Express标准,使PCIe 6.0设备在保持相同信道带宽的情况下能实现PCIe 5.0设备两倍的吞吐量。PCIe 6.0技术最高可达64 GT/s,同时保持低功耗和向后兼容。PCIe 6.0承诺通过x16配置达到256GB/s的吞吐量,在数据中心实现800GE速度。

PCIe 6.0和800GE的速度共同支持AI、机器学习、游戏、视觉计算、存储和网络等应用,以推动5G、云计算、超大规模数据中心等领域的发展。

PCIe 6.0采用高阶调制格式PAM4信号,是对PCIe 5.0技术的重大升级。但是,它对Tx和Rx测试使用了相同的高级方法,同时添加了一些特定于PAM4的新发射器测量编码。与前几代类似,PCIe 6.0设备采用64 GT/s操作的发送器和接收器均衡,并要求前向纠错(FEC)。

除了这些电气变化之外,PCIe 6.0还引入了流量控制单元(FLIT)编码。与物理层的PAM4不同,FLIT编码用于逻辑层,将数据分解为固定大小的数据包。PCIe 6.0以FLIT为单位进行事务传输,每个FLIT有256 B数据(1 FLIT=236B TLP+6B DLP+8B CRC+6B FEC=256B),每B数据占用4 UI。此外,FLIT编码还消除了以前PCIe规范的128B/130B编码和DLLP(数据链路层数据包)开销,从而显著提高了TLP(事务层数据包)效率。

虽然PCIe 6.0更具优势,并且已经提出一年有余,但在PCIe 5.0还没有完全普及的当下,PCIe 6.0何时才能走进用户,有着诸多的不确定因素。目前来看,高性能和吞吐量的应用程序更需要PCIe 6.0,例如包括用于AI工作负载的图形处理单元、高吞吐量网络应用程序和Compute Express Link (CXL)技术,成为异构计算架构下数据交互的高速公路。

Union Memory

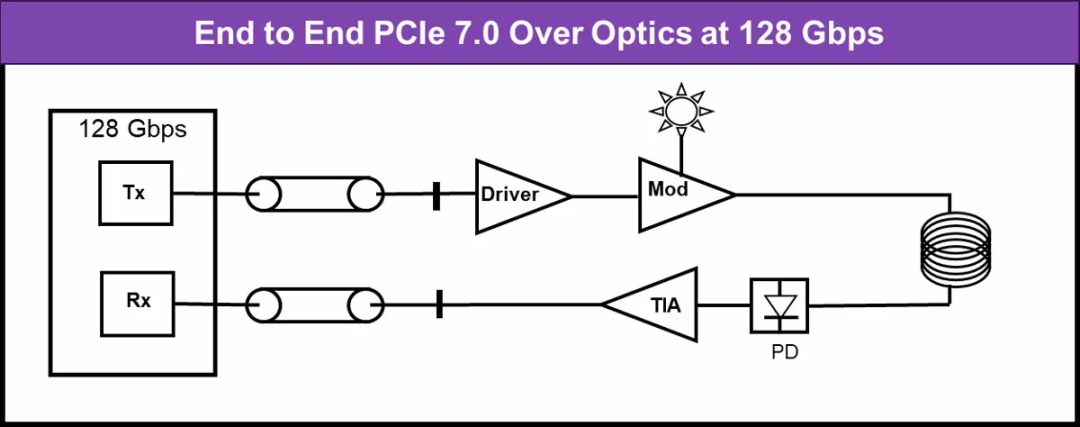

PCIe 6.0接口在保持对前几代产品的向后兼容性的同时,将传输速率提高了一倍,达到64 GT/s,在相同的最大16通道下提供256 GB/s的吞吐量。而7.0版的PCIe规范,将于2025 年发布,预计数据传输速率将再次翻倍,达到128Gbps。

内容来源:

*Evolution-of-PCIe-Standards-and-Test-Requirements

长按识别关注更多忆联资讯

原文标题:PCIe®标准演进历史

文章出处:【微信公众号:UnionMemory忆联】欢迎添加关注!文章转载请注明出处。

-

存储

+关注

关注

13文章

4296浏览量

85796 -

SSD

+关注

关注

21文章

2857浏览量

117366

原文标题:PCIe®标准演进历史

文章出处:【微信号:UnionMemory忆联,微信公众号:UnionMemory忆联】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

pcie扩展槽的使用技巧

pcie 4.0与pcie 5.0的区别

pcie带宽对计算性能的影响

PCIe的最新发展趋势

如何测试PCIe插槽的速度

PCIe 4.0与PCIe 3.0的性能对比

PCIe接口的工作原理 PCIe与PCI的区别

简述微处理器的发展历史

PCIe 5.0 SerDes 测试

PCIe光传输的优势与挑战

pcie4.0插在3.0的主板上会怎么样

PCIE是啥?PCIe结构及应用

PCIe®标准演进历史

PCIe®标准演进历史

评论