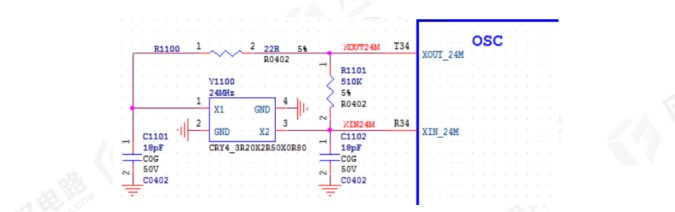

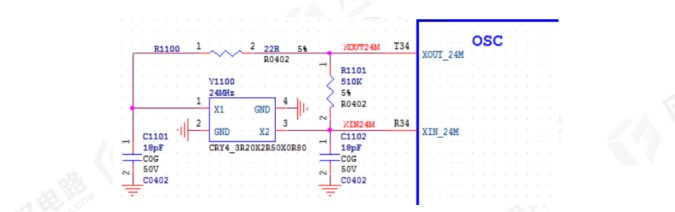

时钟电路就是类似像时钟一样准确运动的震荡电路,任何工作都是依照时间顺序,那么产生这个时间的电路就是时钟电路,时钟电路一般是由晶体振荡器、晶振、控制芯片以及匹配电容组成,如图1所示。

图1 时钟电路

针对时钟电路PCB设计有以下注意事项:

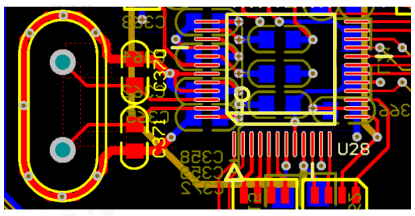

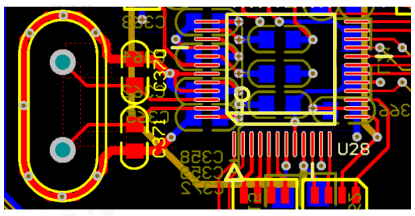

1、晶体电路布局需要优先考虑,布局整体紧凑,布局时应与芯片在同一层并尽量靠近放置,以避免打过孔,晶体走线尽可能的短,远离干扰源,尽量远离板边缘;

2、如果出现晶体电路在布局过程中与芯片放置在不同层的情况,应尽可能的让靠近芯片,让走线变短,并需要将晶体走线全程进行包地处理,以避免被干扰;

3、晶体以及时钟信号走线需要全程包地处理,包地线每隔200-300mil至少添加一个GND过孔,并且必须保证邻层的地参考面完整,如图2所示;

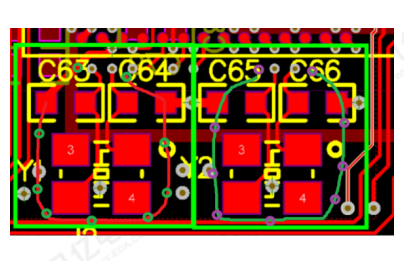

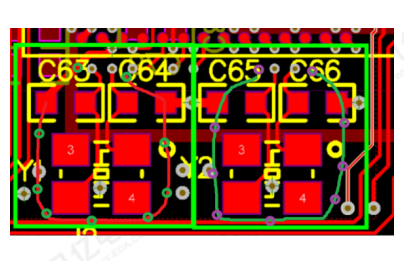

4、晶体的当前层可围绕其进行GND走线形成地环,在地环放置GND过孔,连接到相邻的GND平面层,用以隔离噪声,如图3所示。

图2 晶体布局布线

图3 晶振布局布线

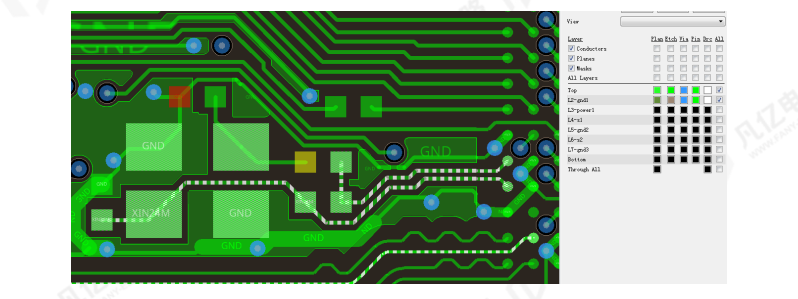

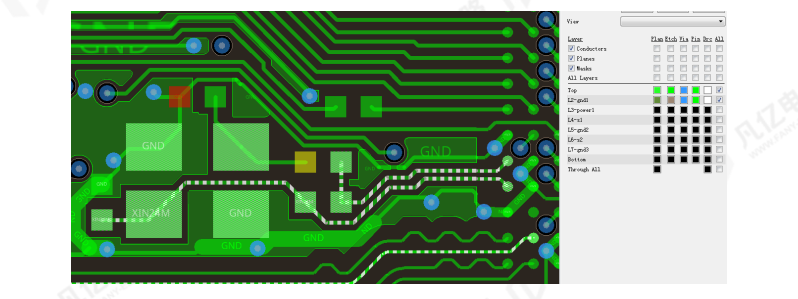

4、时钟走线Xin与Xout以及晶体下方投影区域禁止任何走线,避免噪声耦合进入时钟电路;

6、晶体下面相邻层必须保证完整的参考平面,避免出现跨分割现象,有助于隔离噪声,保持晶体输出,如下图4所示。

图4 第二层为完整的参考平面

声明:

本文凡亿教育原创文章,转载请注明来源!投稿/招聘/广告/课程合作/资源置换请加微信:13237418207

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网

网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:Clock时钟电路PCB设计布局布线要求

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

相关推荐

所提供的表格仅供参考,实际引脚定义可能会因不同的串行接口实现而有所不同。 具体引脚定义应参考相关硬件文档或电路图 。

三、串行接口PCB设计

1、串口一般用到的信号只有 RXD,TXD,GND 。

2

发表于 09-18 12:02

在PCB设计中,布局是一个非常重要的环节,它直接影响到电路的性能、可靠性和成本。以下是关于PCB布局的一些要点,这些要点将帮助您设计出高质量

![的头像]() 发表于

发表于 09-02 14:48

•390次阅读

。以下是它们之间的关系: PCB设计与PCB制板的关系 1. PCB设计: PCB设计是指在电子产品开发过程中,设计工程师使用专业的电子设计软件创建

![的头像]() 发表于

发表于 08-12 10:04

•493次阅读

一站式PCBA智造厂家今天为大家讲讲晶振在PCB板上如何布局?PCB板时钟晶振及相关元件布线原则。晶振布

![的头像]() 发表于

发表于 07-08 09:45

•502次阅读

是否满足ESD或者EMI防护设计要求,撇开原理图设计,PCB设计一般需要我们从PCB布局和PCB布线

![的头像]() 发表于

发表于 06-12 09:49

•605次阅读

针对时钟电路PCB设计有以下注意事项:1、晶体电路布局需要优先考虑,布局整体紧凑,

发表于 06-11 10:24

•0次下载

PCB电源布线是印刷电路板设计中非常重要的一环。电源布线的好坏直接影响到电路的稳定性和性能。本文将介绍几个

发表于 05-16 11:50

•1910次阅读

清宝PCB抄板今天为大家讲讲PCB设计高频电路板布线要注意什么?高频电路PCB

![的头像]() 发表于

发表于 03-04 14:01

•463次阅读

制造缺陷,提高产品的稳定性和可靠性。 而在PCB设计中,布局与布线是决定整个电路板性能、可靠性及制造成本的关键环节之一,所以本文将重点介绍其相关检查项概述。 一、

![的头像]() 发表于

发表于 02-27 18:22

•1756次阅读

缺陷,提高产品的稳定性和可靠性。

而在PCB设计中,布局与布线是决定整个电路板性能、可靠性及制造成本的关键环节之一,所以本文将重点介绍其相关检查项概述。

一、

发表于 02-27 18:19

一站式PCBA智造厂家今天为大家讲讲pcb设计布局布线原则及规则有哪些?PCB设计六大布线规则。在PCB

![的头像]() 发表于

发表于 01-22 09:23

•2094次阅读

PCB电路板布局布线设计交流

发表于 01-19 22:27

现在,虽然有很多软件可以实现PCB自动布局布线。但是随着信号频率不断提升,很多时候,工程师需要了解有关PCB布局布线的基本的原则和技巧,才可

发表于 01-02 15:58

•716次阅读

峰值电流表进行知悉,供PCB Layout时评估线宽作用等。

RK3588 接口的PCB设计

PCB电路接口设计一直属于PCB设计中的重难

发表于 12-25 14:38

峰值电流表进行知悉,供PCB Layout时评估线宽作用等。

RK3588 接口的PCB设计

PCB电路接口设计一直属于PCB设计中的重难

发表于 12-25 14:32

Clock时钟电路PCB设计布局布线要求

Clock时钟电路PCB设计布局布线要求

评论