作为集创赛(全国大学生集成电路创新创业大赛)和全国大学生FPGA竞赛紫光同创赛道官方定制FPGA开发板,紫光同创大学计划协同育人高校推荐开发板,盘古50K开发板已在100+所高校推广使用。

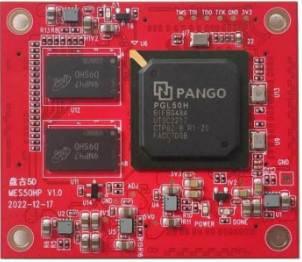

这款基于紫光同创Logos系列PGL50H芯片的开发板,全面实现国产化方案,板载资源丰富,高容量、高带宽,海量外围接口,功能强大,可实现复杂项目的开发评估,满足多方位的开发需求。

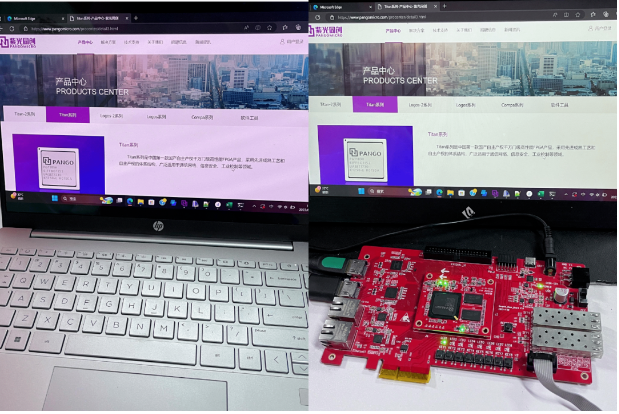

盘古50K开发板试用体验

蔡工:紫光同创PGL50H开发板(盘古50K开发板)配套的资料包内容丰富,提供软件安装文件,提供详细的软件安装方法文档,初学者只需很短的时间就可以掌握Pango Design Suite开发平台,极大增强了学习的信心。

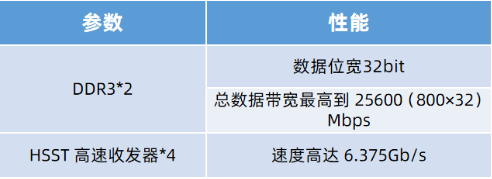

郭工:PGL50H在紫光同创Logos系列中具有不俗的性能表现,逻辑、RAM、IO资源都很充足。其和DDR3之间的数据交互时钟频率最高到400MHz,2颗DDR3的数据位宽为32bit,总数据带宽最高到25600 (800×32)Mbps。同时,PGL50H FPGA 带有4路HSST高速收发器,每路速度高达6.375Gb/s,非常适合用于光纤通信和PCle数据通信。

马工:盘古50K开发板将紫光同创FPGA性能发挥到极致,可以进行复杂项目的开发评估,开发板功能强大,用料实足。

盘古50K开发板详情

1.产品概述

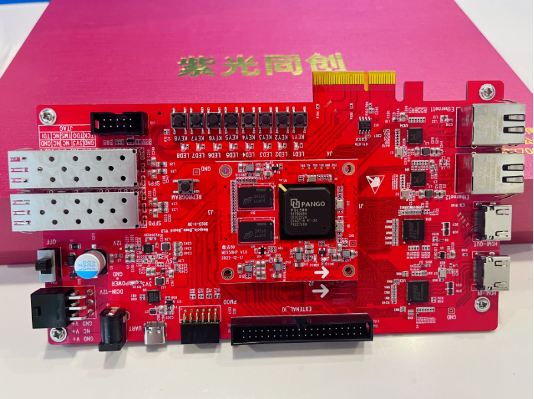

盘古50K开发板(紫光同创Logos系列PGL50H关键特性评估板)采用核心板+扩展板的结构,并使用高速板对板连接器进行连接。

核心板由 FPGA+2 颗 DDR3+Flash+电源及复位构成,承担 FPGA 的最小系统运行及高速数据处理和存储的功能。FPGA 选用紫光同创 40nm 工艺的 FPGA(logos 系列:PGL50H-6IFBG484)。PGL50H 和 DDR3 之间的数据交互时钟频率最高到 400MHz,2 颗 DDR3 的数据位宽为 32bit,总数据带宽最高 25600(800×32)Mbps,充分满足高速多路数据存储的需求。

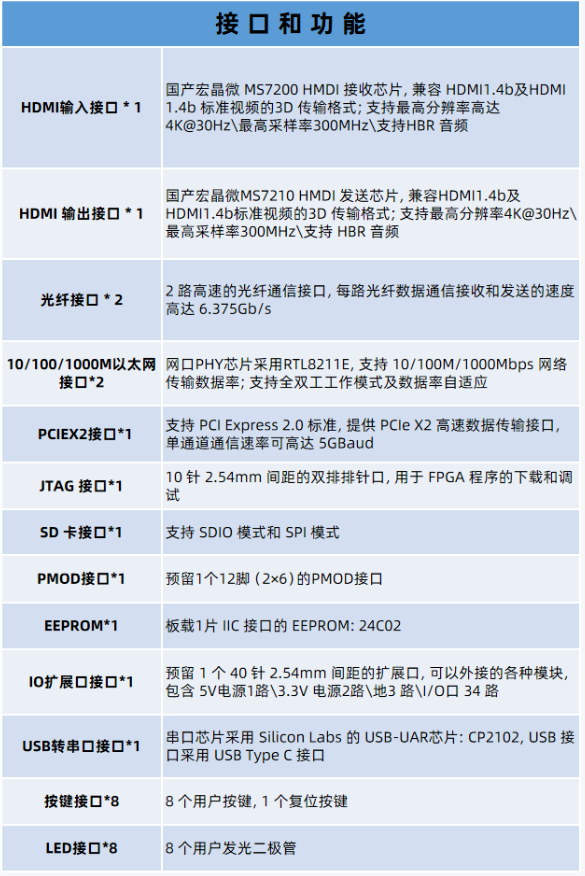

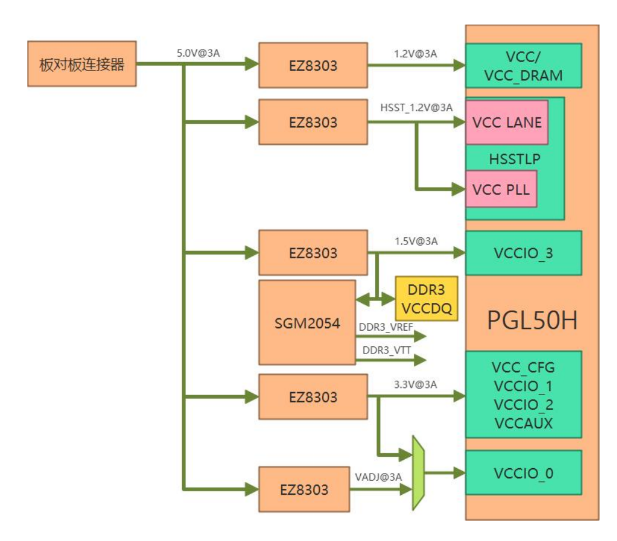

PGL50HFPGA带有4路HSST高速收发器,每路速度高达 6.375Gb/s,适合用于光纤通信和PCIe数据通信;电源采用多颗 EZ8303(艾诺)产生不同的电源电压。底板为核心板扩展丰富的外围接口, 预留 HDMI 收发接口用于图像验证及处理;预留的光纤接口、10/100/1000M 以太网接口,PCIE 接口,方便各类高速通信系统验证;预留一个 40pin 的 IO 扩展连接器,方便用户在开发平台基础上验证模块电路功能。

2.系统资源

系统资源丰富,可以充分满足高速数据的缓存处理需求

海量的外围接口,可以充分满足多方位开发需求

盘古50K核心板详情

盘古50K核心板是基于紫光同创 logos 系列 FPGA(PGL50H-6IFBG484)开发的高性能核心板,具有高数据带宽、高存储容量的特点,适用于高速数据通信、处理、采集等方面的应用。

核心板使用2 片MICRON公司的MT41K256M16TW-107:P 这款DDR3芯片,每片DDR容量为 4Gbit,2片DDR芯片组合成 32bit 的数据总线宽度,FPGA和 DDR3 之间的读写数据带宽高达 25Gb,可以满足高带宽的数据处理需求。

核心板扩展出195个默认电平标准为3.3V 普通IO口,其中有113个IO电压标准可调,12个1.5V电平标准的普通IO口,还有4对HSST高速RX/TX差分信号和1对HSST高速接口的参考输入时钟。

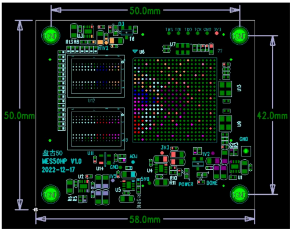

对于需要大量IO的用户,此核心板是不错的选择。FPGA 芯片到接口之间走线做了等长和差分处理。核心板尺寸仅为50*58(mm),非常适合二次开发。

*盘古50K核心板尺寸图

2.系统资源

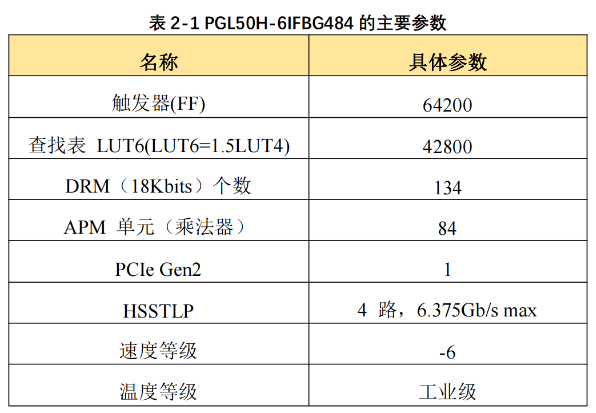

FPGA 型号紫光同创Logos系列PGL50H-6IFBG484速度等级为 6,温度等级为工业级FBG484 封装,484个引脚

3.电源参数

盘古50K核心板电压为 VCCIN,输入电压为 5V需通过板对板连接器供电,连接底板时通过底板供电

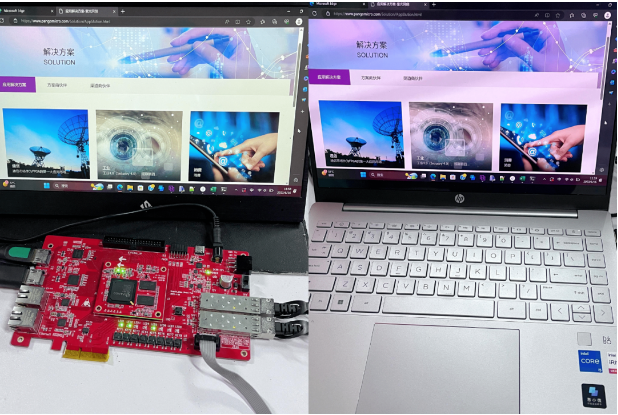

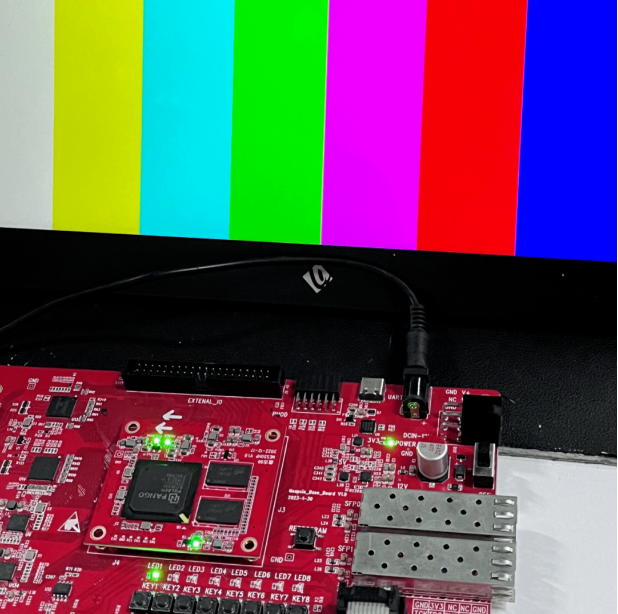

盘古50K开发板实验展示

* 摄像头-HDMI

*视频光纤环路

* HDMI输出

* HDMI视频环路

盘古50K开发板产品实拍

审核编辑 黄宇

-

FPGA

+关注

关注

1629文章

21729浏览量

602960 -

开发板

+关注

关注

25文章

5032浏览量

97371

发布评论请先 登录

相关推荐

被100+所高校种草的FPGA开发板长啥样|国产FPGA开发板PGL50H

被100+所高校种草的FPGA开发板长啥样|国产FPGA开发板PGL50H

评论