今天,我们来聊聊数据中心另一个新技术CXL。

在过去几十年中,CPU一直是计算系统中的绝对核心,甚至连存储、网络等子系统的能力都是CPU说了算。

比如,一个CPU能够支持多大的内存,CPU都是有严格要求的。甚至同样一颗CPU,只是支持不同的内容,都能卖两个价格。

而且更要命的是,随着大内存等应用场景需求大增,想要扩展内存容量,你只能通过买CPU的方式才能扩展内存容量,想要在内存上做点"手脚"那是被限制的死死的。

但人算不如天算,在Intel按部就班的挤牙膏的时候,没想到大数据AI、视觉渲染、基因分析以及EDR仿真等需求的突然爆发,给了NVIDIA 的GPU带了巨大增长空间。

眼看着GPU越卖越多,NVIDIA的市值甚至远远超过了Intel,于是英特尔"挥刀自宫",让充满黑科技意味的傲腾业务和3D Xpoint走向终结,取而代之的是开始向CXL架构发展。

▉推出CXL ,Intel是为了什么?

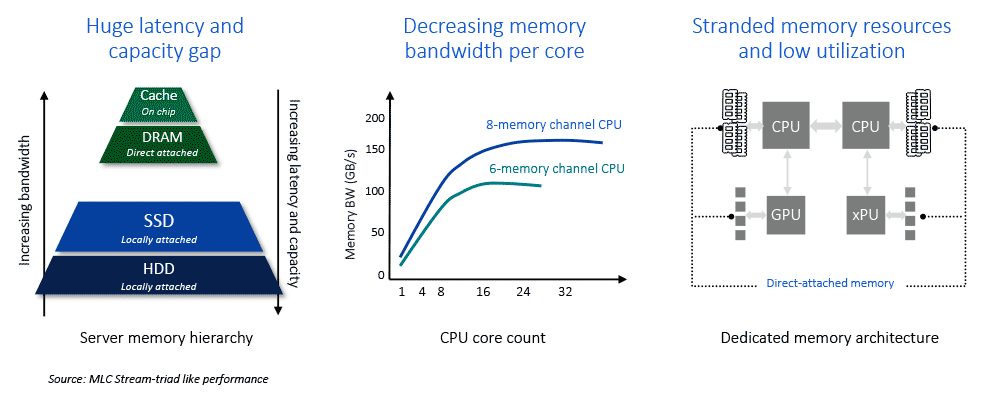

上文中提到,在当前的系统架构中,内存子系统面临诸多挑战。

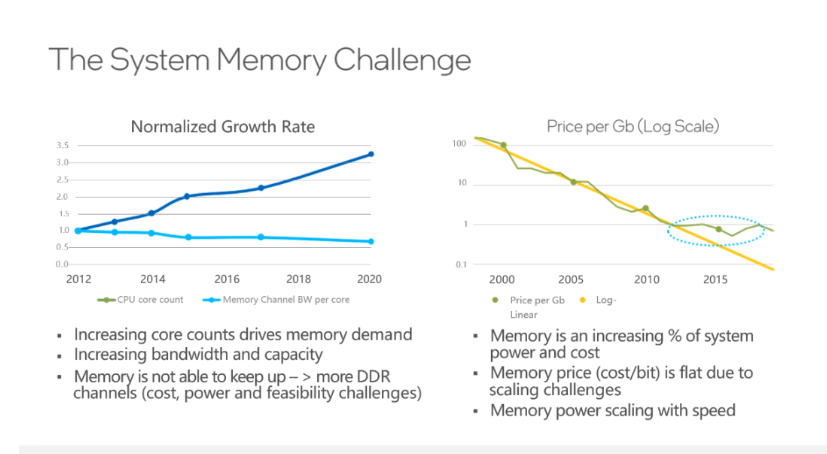

如下面左图所示,CPU技术的发展使得核心数量实现了比较快的增长,内存通道数增速却相对较慢。但从发展趋势来看,每个CPU核心所拥有的内存通道反而是在下降。

这会带来很多问题,很多CPU核心因为不能充分得到数据来处于满负荷的运行状态,会导致整体计算效率下降。

是可忍孰不可忍,这么明显的问题为何Intel在增加核心的时候也增加内存通道呢?

其实并不是英特尔不想,而是牵扯到了多方面原因。首先在CPU设计方面,内存控制器是在CPU里的,如果增加内存通道,则意味着会增加CPU的功耗,芯片面积也会变大,PCB走线距离增加,为了保证信号的完整性,对于PCB本身也提出更高要求,所以,如果增加内存通道,CPU的成本和功耗都会增长。

另外,从服务器整机的层面来看,在主板上增加内存DIMM槽,插上更多的内存后,整机的成本也会不可避免地增长,即使内存成本降低,也不会无限度的降低下去,最终会导致整体成本的上升。所以,不能随意的无限度地通过增加内存通道来解决问题。

既然增加内存通道这条路走不通,那有没有其他方式可以解决内存互联网问题呢?

这个答案当然是肯定的,为了解决内存子系统的问题,几种不同的传输和内存语义协议逐渐出现--IBM的OpenCAPI内存接口协议、Xilinx的CCIX协议、NVIDIA的NVLink协议、惠普企业版的Gen-Z协议,都是为了解决内存池化方面的问题。

虽然这几种协议方式与后来的CXL协议其实类似。但这些明显挖英特尔"墙角"的方式并没有得到Intel的积极响应。店大何止欺客,店大甚至可以决定产品的走向。

但眼看着GPU卖的越来越多,Intel有点坐不住了,于是在2019年3月份Intel推出了CXL(Compute Express Link)协议接口,其与CAPI酷似,也是将CXL协议封装到PCIE链路层数据包中传送,并在CPU端的PCIE总控后端按照事务标识分流CXL专属事务给CXL处理逻辑处理。

为何Intel突然会突然妥协,让出这部分利益,推出CXL协议呢?借用DOIT朱朋博老师的一句话:搁置争议,共同开发。

商人总是寻求利益最大化,既然大内存需求趋势已经来袭,堵不如疏,不如把GPU、DPU等用作一把刀,来与NVIDIA形成某种制衡,当然,如今的NVIDIA也加入了CXL联盟,但是所谓"此路是我开,要在此路过,留下买路财"。反正我建了通往内存的"高速路",你GPU怎么走都得听我的。

通过这种方式,也能进一步制衡GPU的发展,一如文章开头Intel对内存的制约,想支持几个GPU,还得通过我的CPU说了算。值得注意的是,第四代英特尔至强可扩展处理器每一颗处理器支持最多4个CXL设备,支持CXL Type1和CXL Type2。)

▉CXL协议具体能干啥?

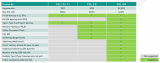

从2019年发布CXL 1.0/1.1,到2020年11月发布CXL2.0,如今Intel已经发布了CXL 3.0,它的功能一直在发生着变化。

首先我们来看下CXL是什么?CXL要如何解决问题呢?

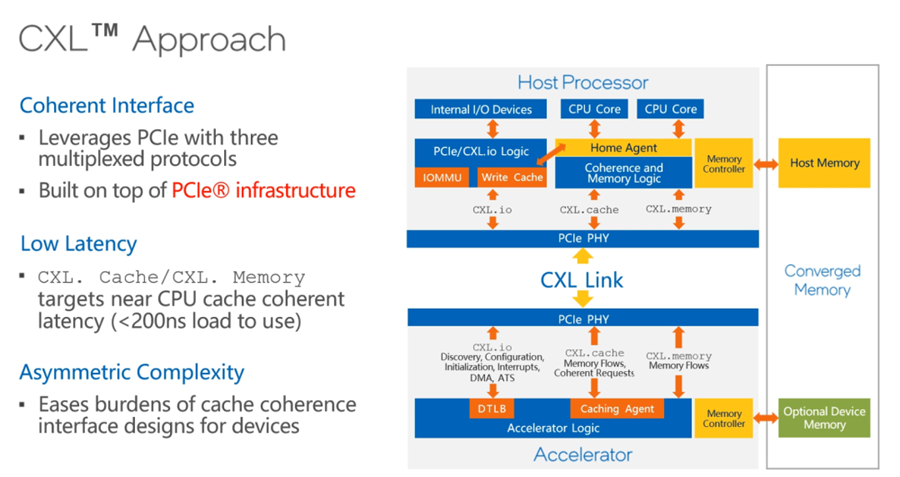

如今,CXL有CXL.io、CXL.memory和CXL.cache三个协议:

其中,CXL.io就是原来的PCIe,在CXL的建立连接、设备发现、配置等过程中发挥重要作用,连接建立后,CXL.cache协议负责做cache一致性的工作,CXL.cache和CXL.memory配合起来用来做内存扩展。

CXL.cache和CXL.memory对于latency的要求会比较高,尤其CXL.cache对延迟要求非常高,因为这关系到计算的效率。

在CXL1.0和1.1规范定义了三种Device:

Type1Device主要的应用场景是高性能计算里的网卡(PGAS NIC),它支持一些网卡的原子操作,主要利用的协议就是CXL.io和CXL.cache。

Type2Device主要指的是带有内存的加速器,包括GPU、FPGA等加速器,它使用的协议包括用来做链接的CXL.io,做cache一致性的CXL.cache,用来做内存扩展的CXL.memory。

Type3Device主要用作内存的Buffer,做内存的扩展。它主要利用CXL.io和CXL.memory的协议。如图所示,CPU除了可以用本地的DDR内存,还可以通过CXL去扩展远端内存,远端内存可以是一个大的内存池,这里的内存可以共享给不同的CPU来用。

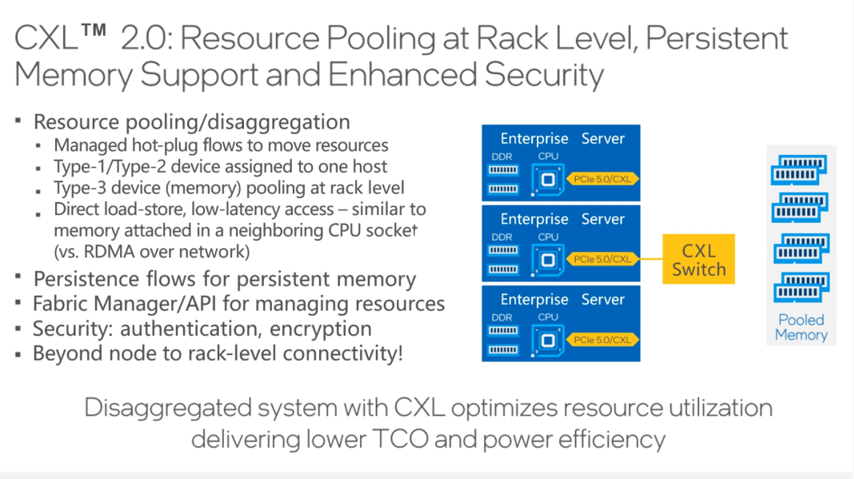

CXL2.0规范实现了机架级别的资源池化。

云计算强调资源可以像水和电一样按需获取,云计算的技术潮流下,追求不同资源之间的松耦合,为的是提高使用效率,为了提高使用效率,要实现的是相同资源的池化。

随着技术的发展,未来的服务器不再是传统意义上的服务器,它不再具有现实的形态,用户从云服务商那里申请云主机的时候,主机的CPU是从CPU池里拿出来的,内存是从内存池里拿出来的,CPU池和内存池通过CXL连起来的。

使用从资源池里拿出来资源组成逻辑上的服务器,这就是资源解耦和资源池化在未来能带来的变化。

CXL2.0规范在资源池化方面有所强化,同时,也还增加了CXL switch功能,它可以在一个机架内通过一套CXL交换机构建成一个网络。

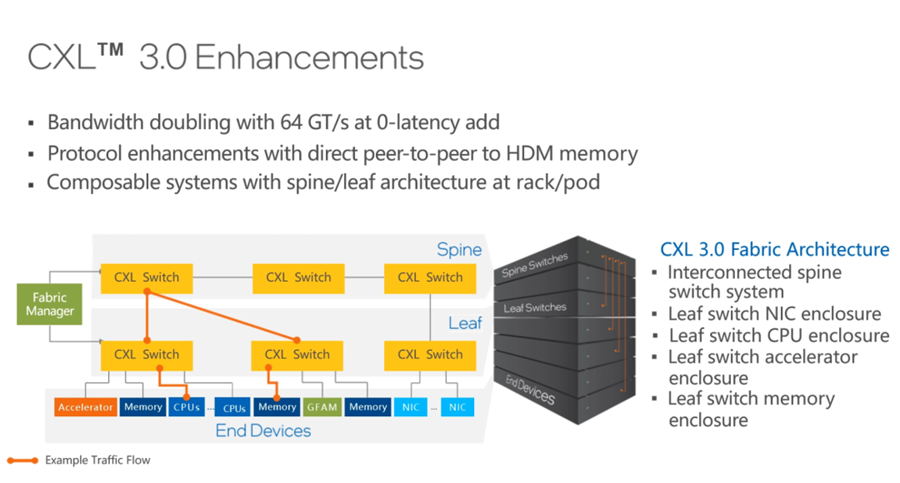

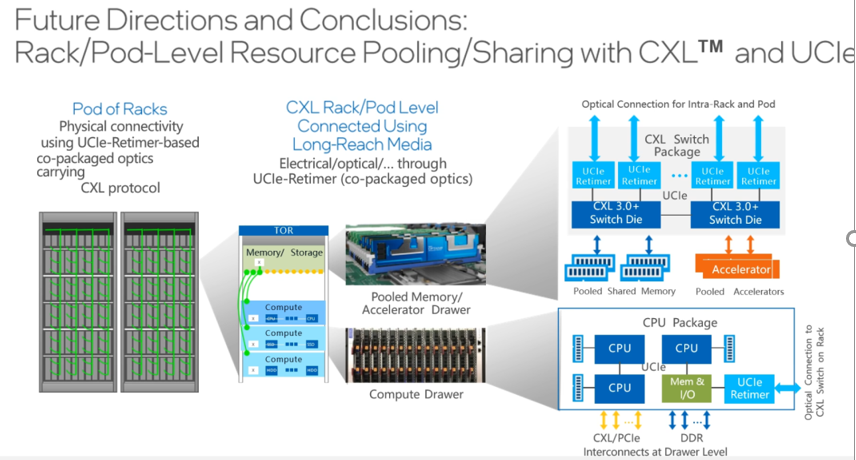

2022年,新发布的CXL 3.0规范又新增很多特性。

首先,CXL 3.0 PCIe 6.0规范,它的速率从32GT提升到了64GT,在相同的链路时,带宽翻倍。并且,Latency也没有任何变化。

第二,CXL 3.0新增了对二层交换机的支持,也就是Leaf spine网络架构,如此便可以更好地对资源进行解耦和池化,做更多的资源池,比如CPU资源池、内存资源池、网卡资源池和加速器资源池等,Leaf与Spine之间通过Fabric manager软件构建各种拓扑和各种路由方式。

CXL 3.0不但可以更好地在一个机柜内实现计算资源和存储资源的池化和解耦,而且,可以在多个机柜之间建立更大的资源池,如此一来,对于云计算服务商的资源管理效率和成本优化都会带来很大帮助。

▉CXL的未来发展方向?

说了那么多CXL的优势和好处,那么CXL的未来发展方向如何呢?

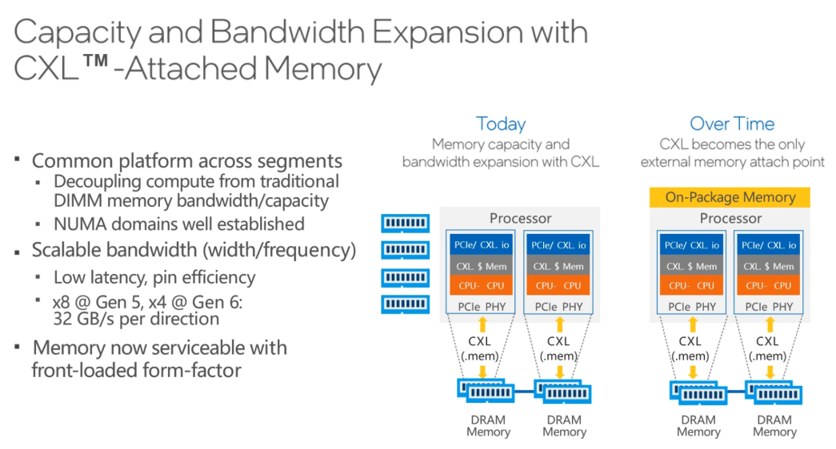

首先,CXL可以用来扩展内存的容量和带宽,这是非常重要的一个方面。在使用服务器本地内存的同时,还可以通过CXL利用远端内存,远端内存的成本和价格相对更低,而且,它能让CPU和内存之间的配比变得更灵活。

进一步发展之后,未来完全可以取消近端本地内存,全部都使用远端内存,这有赖于摩尔定律的作用,让计算芯片和存储芯片都有更进一步的发展。

与此同时,CPU上会有比DRAM更高速的内存,比如可能会把HBM与处理器封装到一个die里,使得CPU有更多的高速内存。

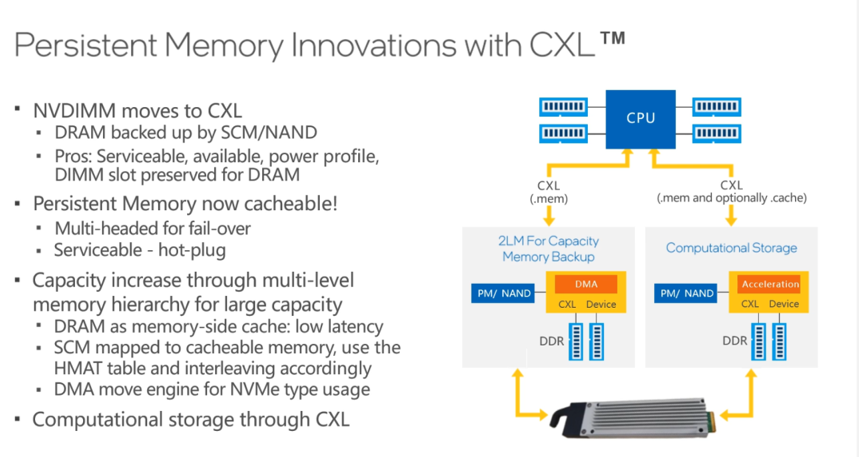

另外,还有一个趋势在于远端内存的持久化。目前,英特尔就有傲腾持久内存,但因为一些原因,英特尔宣布不再继续研发了,不过,业界还有很多替代方案,比如NVDIMM,配合CXL将这些持久内存作为远端内存,还能够提供多种实用功能。

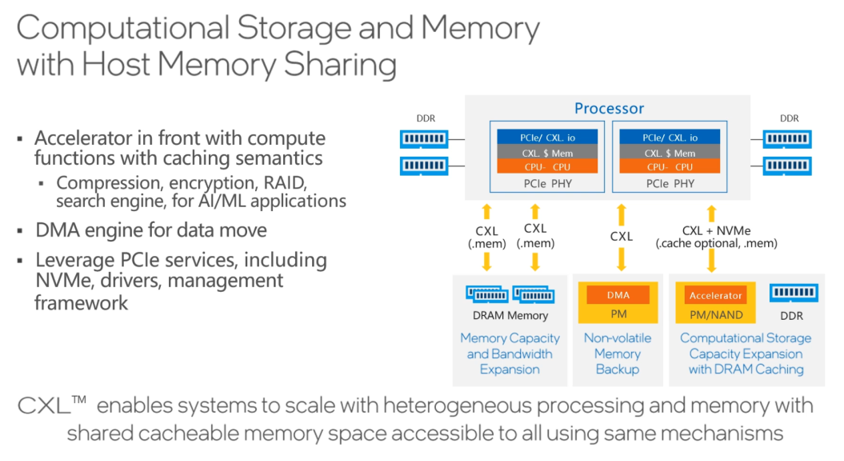

除此之外,还能利用CXL技术实现Computational Storage,通过CXL利用内存资源,在存储上做一些压缩或者解压缩的操作,类似可以在远端实现的功能还有很多。

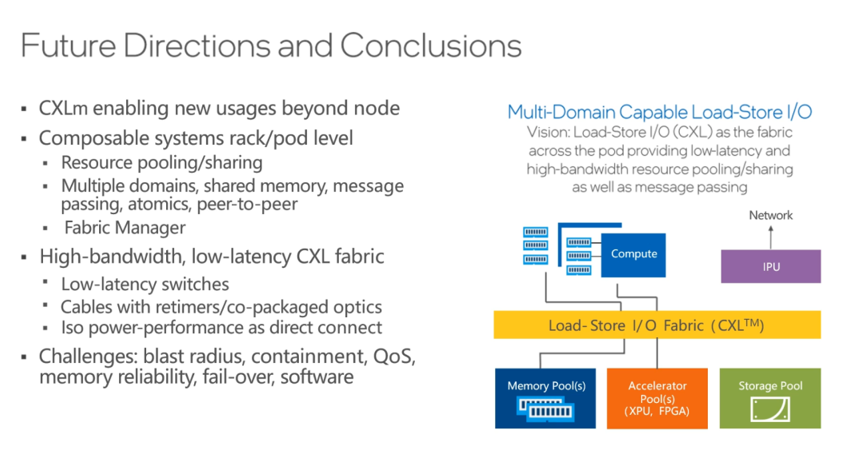

CXL带来的改变从单节点开始,扩展到机架规模,而后是Tor级别,最终会影响到数据中心级别,CXL将要重构未来的数据中心。

数据中心利用CXL做解耦和池化,CXL技术能够让不同的资源从紧耦合变成松耦合,让相同的资源变成池化资源,会形成CPU资源池、GPU资源池以及内存资源池,各个资源池通过CXL连接。

在未来发展中,随着CXL技术的逐步落地,IPU承担的任务也会越来越多,既作为CXL的端点,又作为以太网的端点,会有很多功能和负载卸载到IPU上,架构上会有很多变化,将会有很多新的创新。

比如把存储offload到IPU上,未来还有一些块存储或者其他内存相关服务也都可以用IPU来承载,通过CXL连接到相应的资源池上,总之,未来有非常多的想象空间。

最后,不得不说的是,未来的发展方向中,最终就要实现彻底的解耦和池化,过程是逐步从Rack级别,提升到资源池的级别,甚至是数据中心级别,而这些池化资源之间的共享就靠CXL和UCIe来实现。CXL重构数据中心,并不遥远!

审核编辑:刘清

- 存储器

+关注

关注

38文章

7317浏览量

162886 - 加速器

+关注

关注

2文章

780浏览量

37030 - NVIDIA技术

+关注

关注

0文章

17浏览量

6240 - PCB设计

+关注

关注

394文章

4629浏览量

84267 - FPGA开发板

+关注

关注

10文章

120浏览量

31407

原文标题:一文详解:为什么说CXL能重构数据中心?

文章出处:【微信号:LinuxDev,微信公众号:Linux阅码场】欢迎添加关注!文章转载请注明出处。

发布评论请先登录

相关推荐

一文解析CXL系统架构

CXL事务层的结构是由哪些部分组成的

CXL内存协议介绍

一文详解CXL链路层格式的定义

Intel宣布联合多家厂商推出全新互联协议 并发布CXL1.0规范

Astera Labs推出业界首个CXL™ 2.0 Memory Accelerator SoC Platform

Cadence推出新一代CXLVIP和系统VIP工具

SMART世迈科技推出首款XMMCXL内存模块

CXL协议和标准介绍,CXL2.0和3.0有什么新功能?

IPU和CXL如何提高数据中心的电源效率?

什么是CXL技术?CXL的三种模式、类型、应用

内存扩展CXL加速发展,繁荣AI存储

推出CXL,Intel是为了什么?聊聊数据中心另一个新技术CXL

推出CXL,Intel是为了什么?聊聊数据中心另一个新技术CXL

评论