问题:

请简述锁存器与触发器的概念,并分析二者的区别。

简答:

1. 锁存器与触发器的概念

锁存器和触发器都是具有记忆功能的二进制存储器件,是组成数字电路的基本器件之一:

1.1 锁存器(Latch)

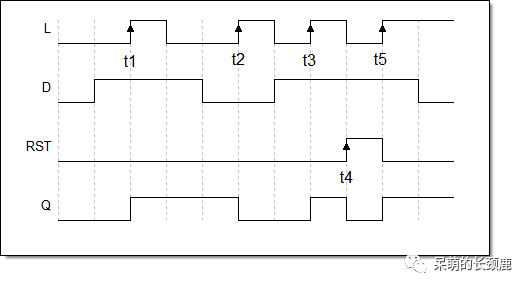

锁存器是由电平触发的存储单元,数据存储操作取决于使能信号的电平值。在有效电平下,当且仅当锁存器处于使能状态时,输出信号随输入信号发生变化,此时不进行锁存操作,类似于缓冲器操作;当锁存器不处于使能状态时,输出信号不随输入信号发生变化,输出数据一直处于锁存状态。常见的锁存器包括SR锁存器、D锁存器和JK锁存器等。

1.2 触发器(Flip-Flop)

触发器是由时钟边沿触发的存储单元,数据存储操作取决于时钟信号的边沿。输出信号仅在时钟沿(上升沿或下降沿)到来时,才随输入信号的改变而改变。常见的触发器包括SR触发器、JK触发器、D触发器和T触发器等。

2. 锁存器与触发器的区别

锁存器和触发器都具备记忆功能,即输出信号不仅与当前输入相关,同时还与上一时刻的输出相关。锁存器与触发器的区别主要体现在以下几个方面:

锁存器由使能端电平触发,属于异步控制;触发器由时钟沿触发,属于同步控制;

锁存器对电平敏感,受布线延迟影响较大,输出信号容易产生毛刺;触发器不易产生毛刺;

对于ASIC而言,由于锁存器消耗的门资源小于触发器,所以锁存器的集成度比触发器高;对于FPGA而言,由于FPGA中没有标准的Latch单元,但有多种FF单元,所以锁存器需要用多个逻辑单元(LE, Logic Element)实现;

锁存器无法过滤毛刺,容易导致设计时序混乱,不利于设计的静态时序分析(STA, Static Timing Analysis);触发器可以保证设计的时序稳定,在很多情况下无法用锁存器替代。

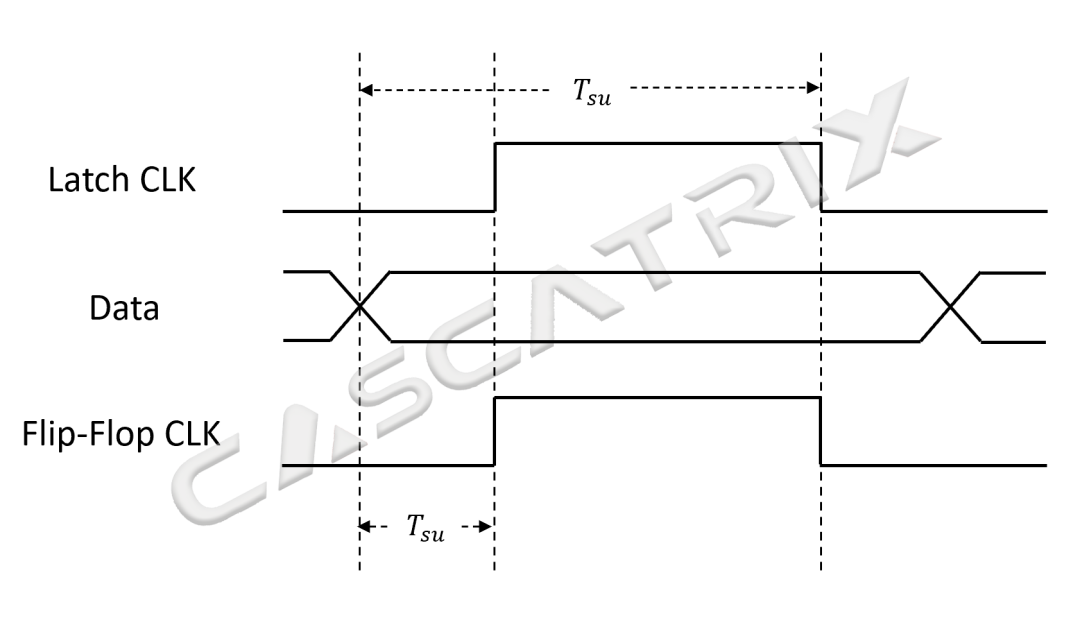

对于上升沿触发的触发器而言,建立时间是时钟上升沿之前所需要的时间;当将时钟信号接入锁存器使能端时,若锁存器为高电平使能,建立时间是时钟下降沿之前所需要的时间。因此,在数据信号晚于控制信号到来的情况下,只能采用锁存器,这种情况被称为Latch timing borrow,即建立时间借去一个高电平的时间。

审核编辑:汤梓红

-

FPGA

+关注

关注

1629文章

21729浏览量

602964 -

锁存器

+关注

关注

8文章

906浏览量

41494 -

数字电路

+关注

关注

193文章

1605浏览量

80578 -

触发器

+关注

关注

14文章

2000浏览量

61130

原文标题:FPGA逻辑题目003——锁存器与触发器的区别

文章出处:【微信号:Carlinx FPGA,微信公众号:Carlinx FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

锁存器与触发器的概念及其区别

锁存器与触发器的概念及其区别

评论