直播问答整理如下,供大家参考。

现场来不及提问、或错过直播的观众可以在后台留言提问,我们会转给相关技术人员进行解答。

也欢迎大家就培训本身的改进意见给我们留言,我们会根据大家的反馈调整今后的培训计划。

Q

PCB中如何控制阻抗,阻抗的控制和哪些因素相关?

答:

PCB 布局和层堆叠:阻抗受到 PCB 布局和层堆叠的影响。例如,信号线与地平面之间的距离、信号线周围的引脚和铜填充等都会影响阻抗。因此,在进行 PCB 布局时,需要考虑这些因素来控制阻抗。

传输线特性阻抗:阻抗与传输线的特性参数有关,如传输线的宽度、间距、高度、介电常数等。根据所使用的 PCB 材料和设计要求,可以使用 Allegro 软件提供的工具来计算和设置传输线的特性阻抗。

差分线和匹配阻抗:对于差分信号线,需要保持差分阻抗的匹配,以确保信号的平衡和抑制共模噪声。在 Allegro 软件中,可以使用差分线约束来设置差分阻抗的要求。

Q

Allegro X 和 Allegro 17.4、Allegro 22.1 的区别?

答:Allegro X 是新一代的 Allegro PCB 设计软件,是集合了前端、后端设计,库、数据管理、EE 分析等为一体的综合性平台(PCB Deisgner、System Capture、Pulse、PCB Librarian、Design Workbench...)。

而 Allegro 17.4 只是 Allegro 软件的一个版本号。目前的版本已经更新到 22.1。

Allegro X 是在 22.1 版本下发布的,因此对比 17.4 版本,除了提供整合的平台之外,更提供了更多高效、进阶的功能,例如 Convert、In-Design Analysis、Void spacing control 等。

如果要了解详细特性,请联系我们:spb_china@cadence.com。

Q

在 Allegro 软件中,如何针对 DDR4 的设计进行规则设置以及如何使用规则约束布线?

答:首先,打开 Allegro 软件并加载 DDR4 设计文件:

在菜单栏中选择 Constraints -> Physical -> Constraint Manager,打开规则管理器件,创建约束规则。对于DDR4 设计,一些常见的约束规则包括时序规则、布局规则和信号完整性规则。

时序规则:在 “Timing” 选项卡下,可以设置时钟和数据信号的时序规则,如时钟频率、时钟延迟、数据传输时序等

布局规则:在 “Placement” 选项卡下,可以设置DDR4芯片的布局规则,如芯片位置、引脚分配等

信号完整性规则:在 "Signal Integrity“ 选项卡下,可以设置信号的电气特性规则,如信号幅度、传输线特性阻抗等。

根据 DDR4 的规格和设计要求,逐个设置所需的约束规则。可以通过点击"Add"按钮来添加新的约束规则,并根据需要进行设置。

在设置约束规则时,可以使用Allegro提供的约束模板或自定义约束,具体根据 DDR4 的规格和设计要求来决定。

完成约束规则的设置后,可以对设计进行布线规则。在布线过程中,Allegro 会根据设置的约束规则进行布线,确保设计满足约束要求。

需要注意的是,DDR4 设计的约束规则设置需要根据具体的设计要求和 DDR4 的规格来确定,建议参考DDR4 产品手册和 Allegro 软件的相关文档来了解更多详细信息和操作步骤。

Q

如何在 Allegro 软件中对阻抗进行设置?

答:打开 Allegro 软件并加载 PCB 设计文件:

在菜单栏中选择 Constraints -> Physical -> Constraint Manager,打开规则管理器。

在规则管理器中,选择 “Signal Integrity“ 选项卡。在该选项卡下,可以设置信号的电气特性规则,包括阻抗。

点击“Add”按钮,添加新的信号规则。在弹出的对话框中,选择"Net",然后选择要设置阻抗的信号线。

在规则设置中,可以指定信号线的阻抗规格。可以选择固定阻抗值,也可以选择通过定义传输线参数来计算阻抗。

完成阻抗设置后,可以进行布线和仿真,Allegro 会根据设置的阻抗规则来布线并进行信号完整性分析。

需要注意的是,阻抗的设置需要根据具体的设计要求和所使用的 PCB 材料来确定,建议参考 PCB 材料的规格和 Allegro 软件的相关文档来了解更多详细信息和操作步骤。

Q

一份原理图下如果有多份 .dsn 文件,如何分别导出网表?

答:打开原理图设计工程,在 OrCAD Capture 中选择要导出网表的 .dsn 文件:

在菜单栏中选择 Tools -> Create Netlist。

在 "Output Options" 部分,选择 "Create a new netlist file",然后为每个.dsn文件指定不同的导出网表文件名和路径。

在 "Output File" 部分,点击 "Browse" 按钮选择导出网表的文件名和路径。

点击 "OK" 开始导出网表。重复以上步骤为每个.dsn文件进行网表导出。

通过以上步骤,可以为每个.dsn文件分别导出网表,确保每个文件都有对应的网表文件。请注意,确保每个.dsn文件在导出网表时都使用不同的文件名和路径,以避免混淆或覆盖。

-

原理图

+关注

关注

1296文章

6338浏览量

233754 -

pcb

+关注

关注

4319文章

23080浏览量

397456 -

阻抗

+关注

关注

17文章

957浏览量

45912 -

RK3588

+关注

关注

6文章

325浏览量

4311

发布评论请先 登录

相关推荐

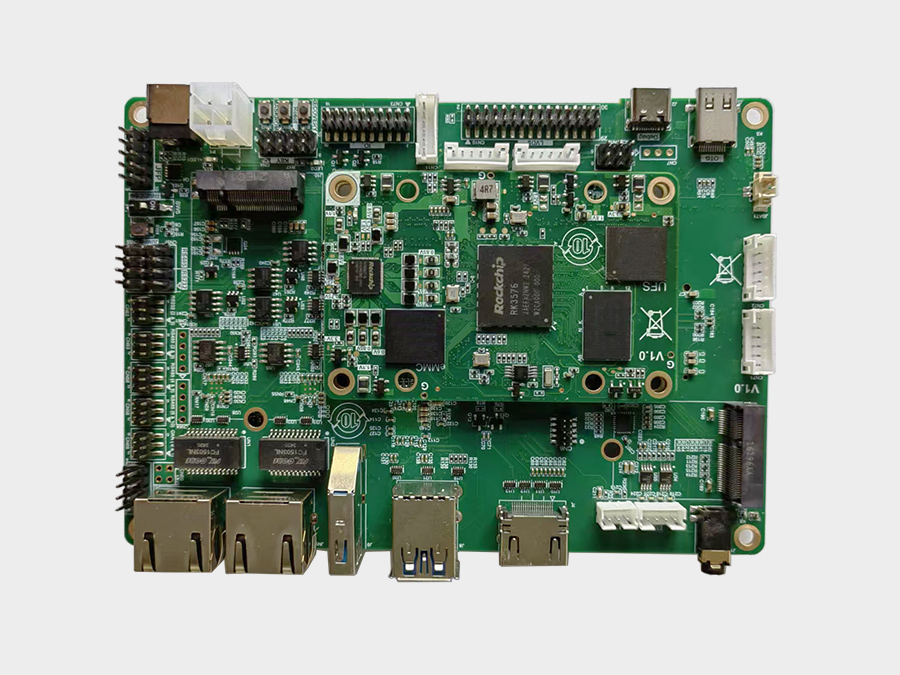

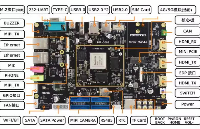

RK3588与RK3576区别解析

三分钟快速上手RK3588开发板

RK3588 SDK入门之编译使用篇

RK3588 从原理图迁移同步到 PCB 的关键操作及技巧

RK3588 从原理图迁移同步到 PCB 的关键操作及技巧

![[<b class='flag-5'>RK3588</b><b class='flag-5'>从</b>入门<b class='flag-5'>到</b>精通]系列内容专栏目录及介绍](https://file1.elecfans.com/web2/M00/89/71/wKgZomSD4l6AF1pHAERebsBrF3M34.jpeg)

评论