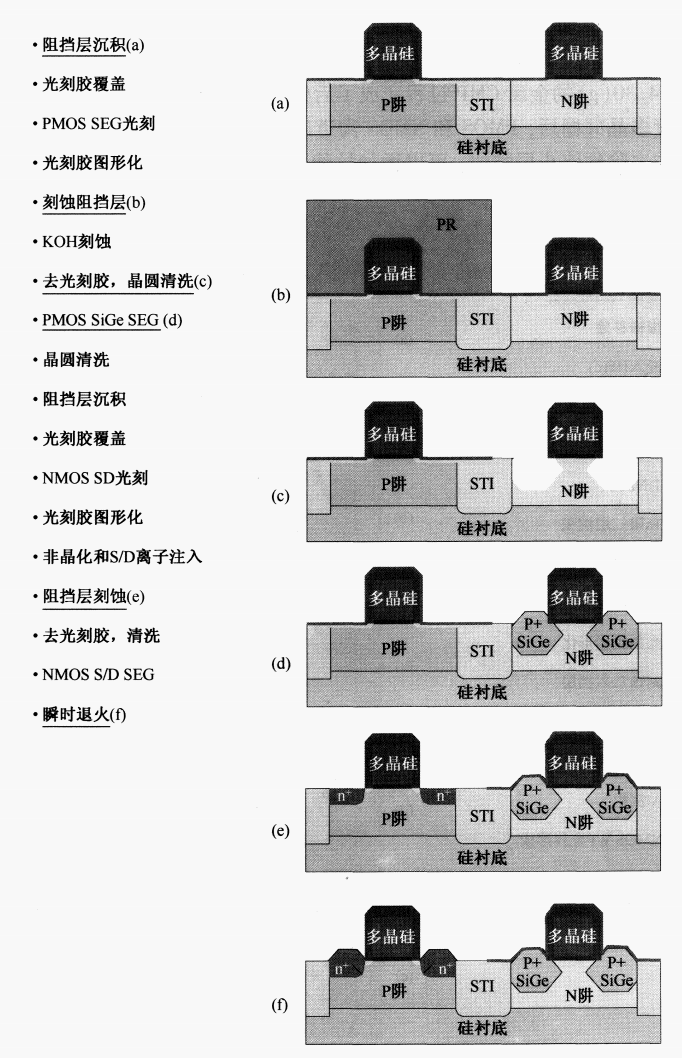

下图(a)中的沉积块状层是必需的,这是为了SEG可以生长在设计的区域。下图(c)显示了KOH硅刻蚀,这种刻蚀对<111>晶体硅具有高的选择性。通过使用KOH刻蚀,设计者可以精确地控制硅刻蚀轮廓并实现优化的器件性能,这是由于优化的沟道应变所致。如下图(d)所示,PMOS的源/漏极掺杂通过SEG过程中的临场掺杂实现。

NMOS源/漏掺杂仍然是传统的低能量、高电流离子注入和热退火过程,如下图(e)和下图(f)所示。进行非晶硅深离子注入和瞬间NMOS源/漏退火,设计者可以增强NMOS沟道的拉伸应变,进而增加电子迁移率并提高NMOS速度。由于拉应变在SD形成后会一直保持,所以这种技术称为应力记忆技术(SMT)。由于微小尺寸器件有限的热积存,退火必须使用瞬间退火、激光退火或两者的结合。

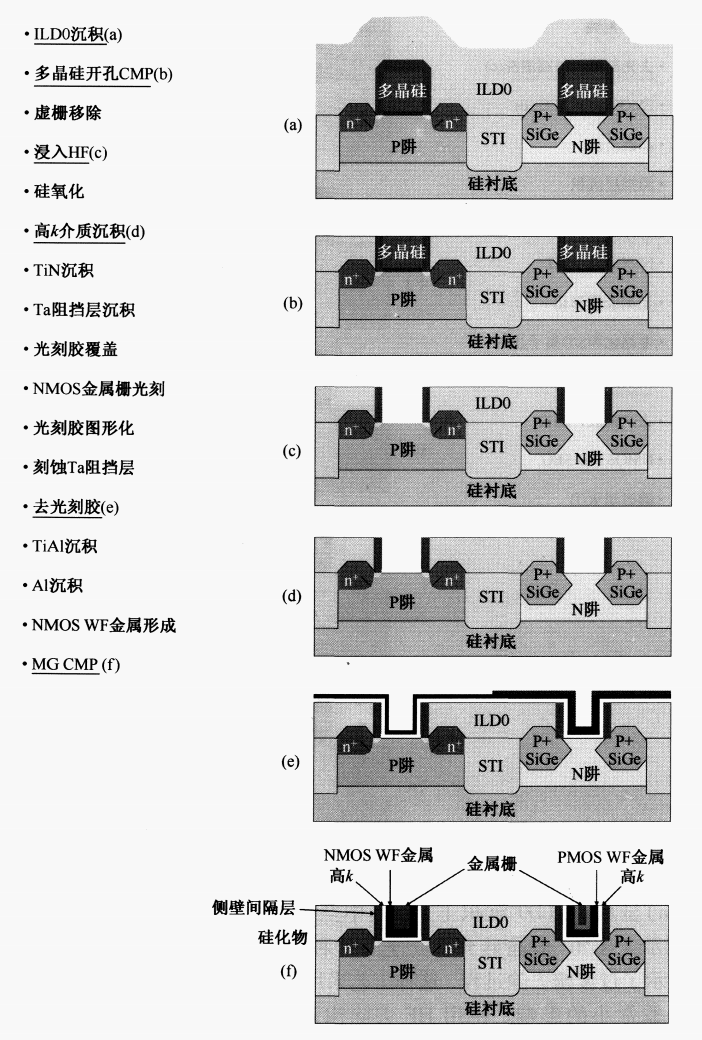

下图显示了高k金属栅(HKMG)工艺过程。

下图(a)显示了ILD0沉积工艺,其中至少有氮化物衬垫/ESL和氧化层两层材料。下图(b)显示了CMP多晶硅开孔工艺,这种工艺是ILD0过抛光并暴露出多晶硅栅。下图(c)显示了过渡栅去除过程,这种工艺采用高选择性刻蚀去除多晶硅,然而对ILD0和侧壁间隔层有非常小的影响。使用HF去除沟道上的氧化层后,形成一层薄氧化硅,如下图(d)所示,接着沉积铪基高为介质。

HF通常使用原子层沉积(ALD)工艺实现。ALD工艺也可以沉积氮化钛(TiN)和钮(Ta)层。TiN常用于PMOS金属,而NMOS需要不同的功函数金属,而且将在后续的工艺中形成。Ta作为PMOS中的阻挡层可以保护TiN。利用图形化从NMOS中去除Ta后,如下图(e)所示,沉积钛铝合金(TiAl),并利用大量铝(Al)填充间隙。退火工艺过程中,TiAl与TiN发生反应生成TiAlN,并作为NMOS的金属栅功函数调节层。显示于下图(g)的金属CMP过程完成了后栅HKMG工艺。

当去除过渡多晶硅栅后,PMOS和NMOS沟道应力显著增加,这使得载流子迁移率增加,速度提高。这与去除硬停止层类似,可以增加拉伸应变或压缩应变。这是后栅HKMG比先栅方法优越的地方之一。

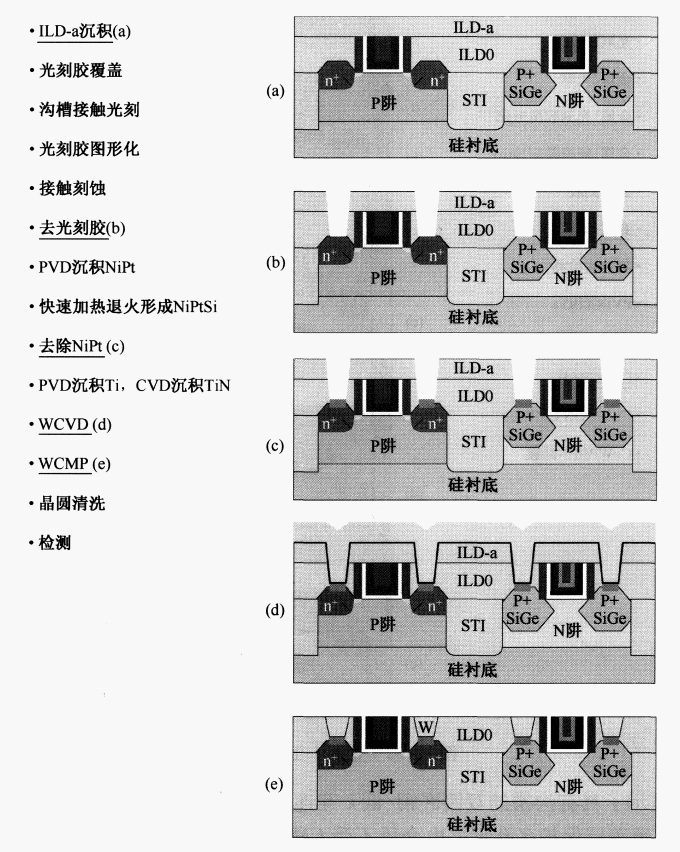

下图显示了MEoL工艺。与之前的接触工艺有许多不同,首先是沟槽金属硅化物。沟槽金属硅化物在沟槽刻蚀后形成,而自对准金属硅化物在源/漏极形成后、ILD0沉积前形成。

沟槽金属硅化物仅仅在接触沟槽的底部,如下图(c)所示。因为栅极由金属组成,所以栅极并不需要形成金属硅化物。掺杂少量钳的镣硅化物,NiPtSi,比NiSi要稳定。填充了接触沟槽的钧被研磨到金属栅极的同一平面,如下图e)所示。由于接触沟槽只与凸起的源/漏极接触,所以接触沟槽深度很潜,这样使得过刻蚀的控制简单。从版图的角度考虑,代替了圆形和椭圆形接触孔的沟槽式接触,简化了光刻胶图形化过程。但这会在接触刻蚀中,过刻蚀到STI氧化层而导致W尖刺问题。由于钨栓塞的长度显著缩短,所以栓塞的电阻大大降低。

审核编辑:刘清

-

控制器

+关注

关注

112文章

16332浏览量

177798 -

CMP

+关注

关注

6文章

150浏览量

25978 -

ICT技术

+关注

关注

0文章

44浏览量

10144 -

NMOS管

+关注

关注

2文章

121浏览量

5407

原文标题:半导体行业(一百九十九)之ICT技术(九)

文章出处:【微信号:FindRF,微信公众号:FindRF】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

高k金属栅(HKMG)工艺详解

GLOBALFOUNDRIES德累斯顿工厂出货第25万枚32纳米HKMG晶圆

深入赛灵思Kintex-7 FPGA内部:透视HKMG技术

高介电常数栅电介质/金属栅极的FA CMP技术

专访格罗方德Subramani Kengeri:28nm量产致胜关键在于HKMG

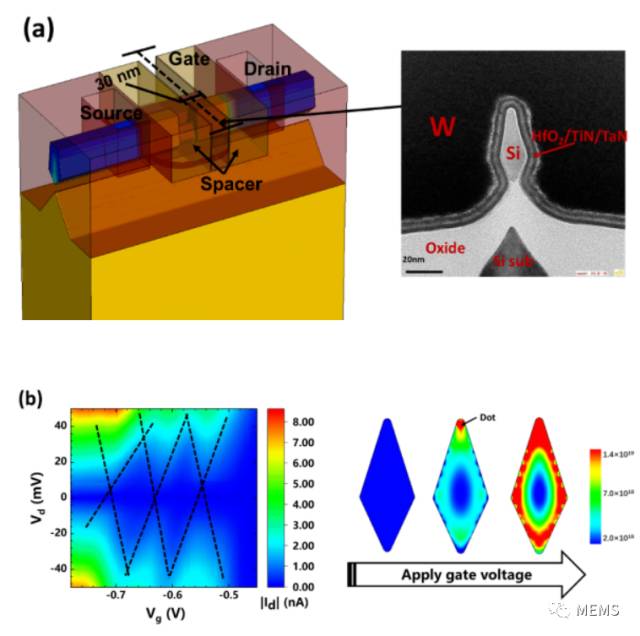

基于主流的体硅高κ/金属栅FinFET工艺,提出了一种利用拐角效应

ICT技术高k金属栅(HKMG)的工艺过程简析

ICT技术高k金属栅(HKMG)的工艺过程简析

评论