前言

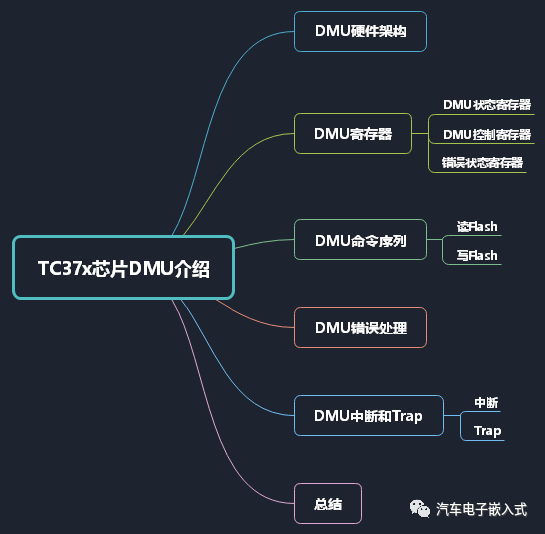

AUTOSAR架构图下的Fls模块对上(Fee)模块提供统一的标准接口,但是具体的实现因不同的芯片而不一样,Infineon公司的Fls模块通过操作TC3xx芯片的DMU模块实现Fls的功能。在具体介绍Fls模块的功能之前,有必要先介绍下TC3xx芯片的DMU模块。本文就来详细介绍下TC37x芯片的DMU功能,希望能搞清楚以下问题:

问题1:站在软件实现的角度来看,如何通过DMU实现读,写,擦除DFlash?

问题2:站在软件实现的角度来看,如何通过DMU监控读,写,擦除DFlash等任务完成的?

问题3:站在软件实现的角度来看,如何通过DMU监控读,写,擦除DFlash等任务出现Error的?

问题4:站在软件实现的角度来看,在监控到读,写,擦除DFlash等任务出现Error后如何恢复重来?

Note: 作者对芯片的各种模块的硬件接口或者功能实现也不是很理解(非电子信息专业出身,属于半路出家的半吊子……),但是站在软件开发者的角度来看,个人理解,操作芯片模块基本就是操作芯片模块的控制寄存器来达到想要的功能,轮询芯片的状态寄存器判断控制命令是否完成,监控Error寄存器看是否发生错误(发送错误后一般通知上层后尝试重置芯片模块功能)。对于软件开发者,搞清楚上述四个问题其实就是搞清楚在上述问题的上下文中如何控制和监控寄存器。

缩略词

| 简写 | 全称 |

| DMU | Data Memory Unit |

| DPI | Direct Processor Interface (to Local Flash Bank) |

| FSI | Flash Standard Interface |

| SRI | Shared Resource Interconnect |

| SIF | Slave Interface |

正文

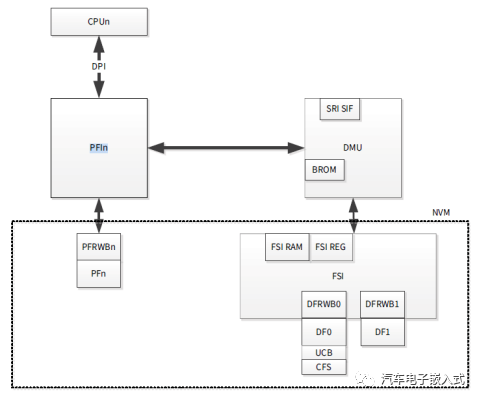

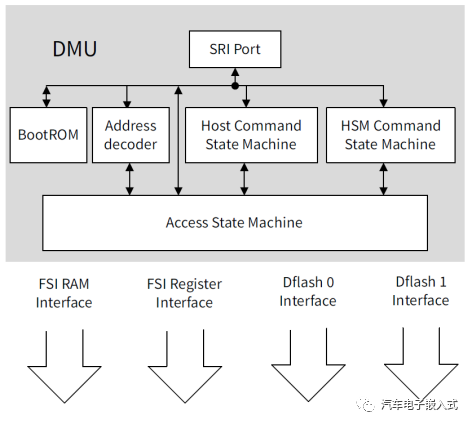

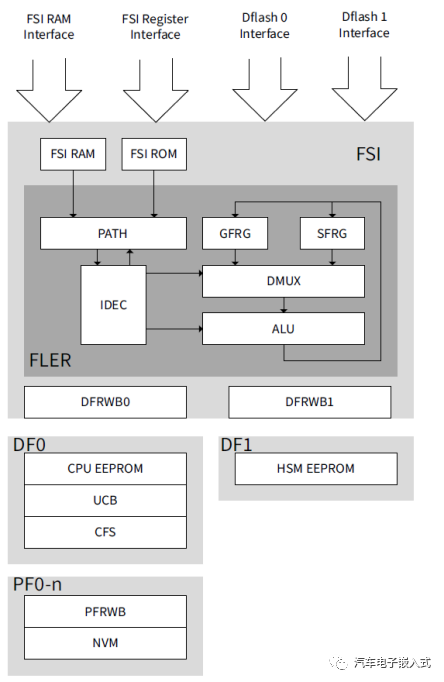

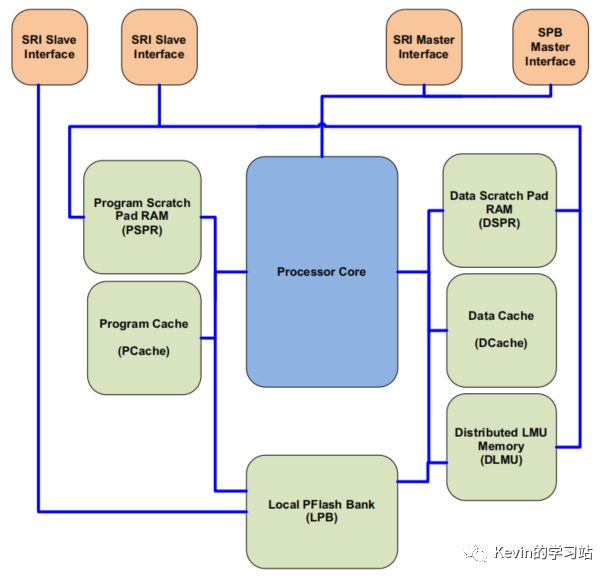

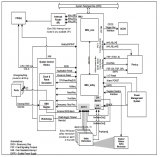

1.DMU硬件架构

CPU通过SRI总线能够访问/控制DMU,DMU通过FSI接口能够控制DFLASH。CPU访问/控制DMU可以通过软件(我们写代码)实现,DMU通过FSI访问/控制DFLASH是硬件实现(软件不不参与,软件发错命令序列后只能轮询DMU的状态寄存器来获取DMU访问/操作DFLASH的结果)。

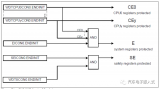

图1:Non Volatile Memory (NVM) Subsystem

图2:Block diagram of DMU module

图3:Block Diagram of the NVM module

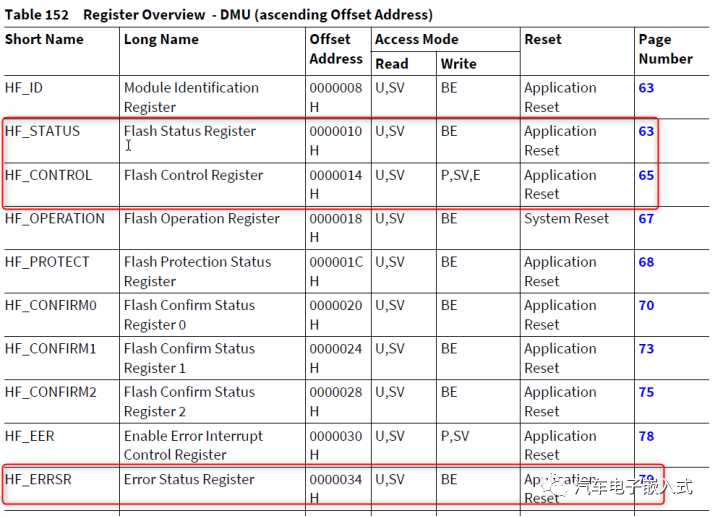

2.DMU寄存器

DMU模块相关的寄存器很多,这里我们只要了解DMU相关的控制,状态,错误状态三个寄存器就能理解绝大部分的功能。

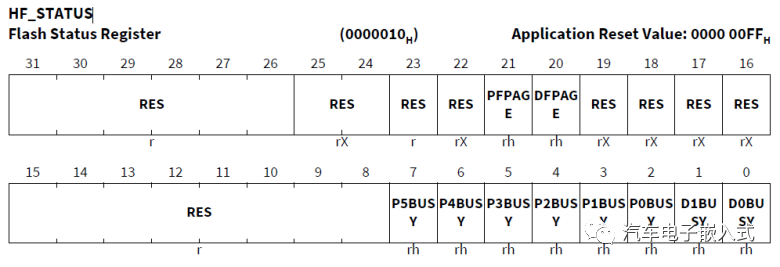

2.1 DMU状态寄存器

HF_STATUS状体寄存器,标识当前Flash的状态。比如,标识当前Flash是否在Page Mode(擦写Flash时必须在这个模式下),Flash当前是否Busy(Flash是否正在处理上一次的擦写任务)。

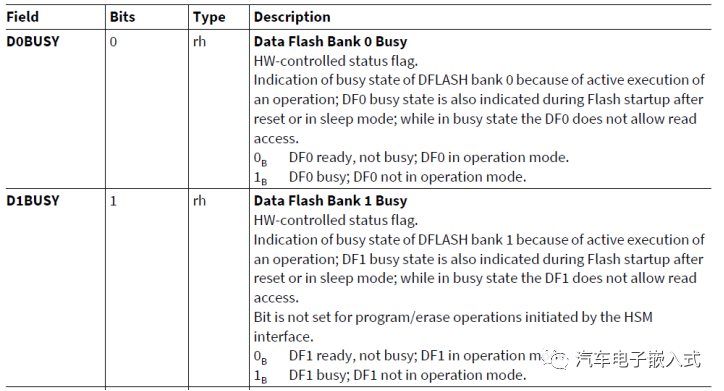

D0BUSY: 标识DFlash0是否处于Busy状态。

D1BUSY:标识DFlash1是否处于Busy状态。

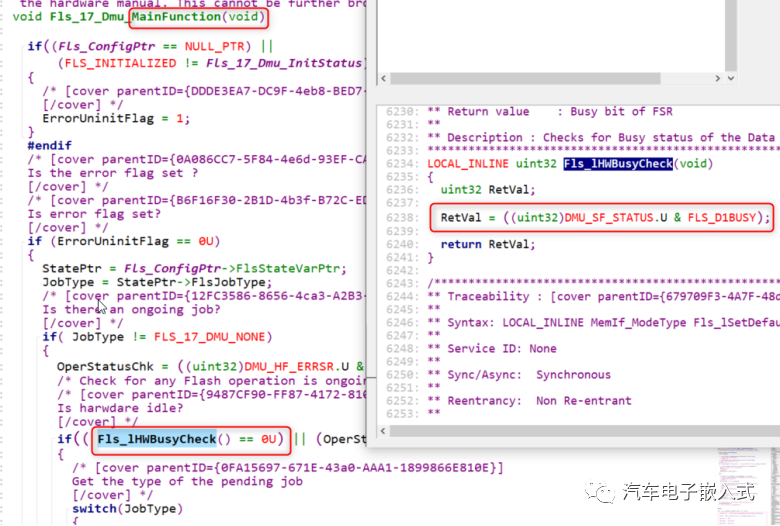

Fls在进行硬件操作前,会检查DFlash是否Busy,如果Busy的话就不进行任何操作。

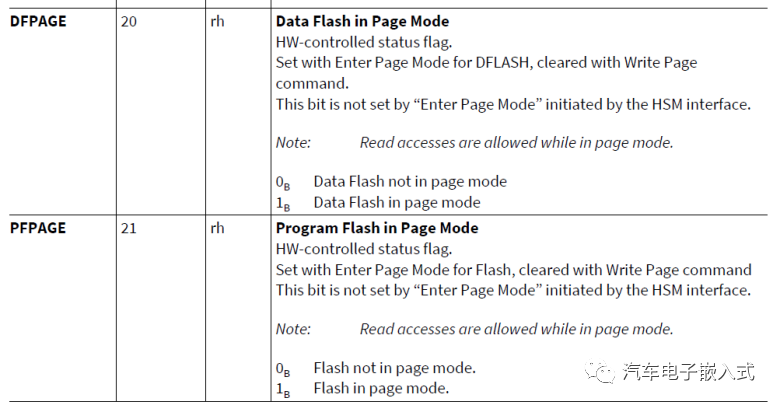

DFPAGE: 标识DFlash是否处于Page Mode

DFPAGE: 标识PFlash是否处于Page Mode

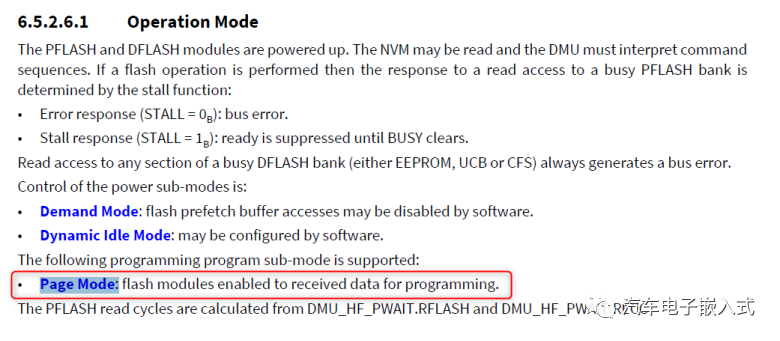

Fls在执行Writesequence前都要先进入到Page Mode

Note: 进入Page Mode后,Flash模块才能够接收写入的数据

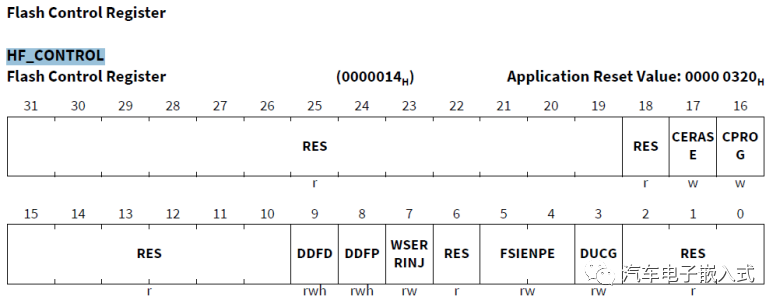

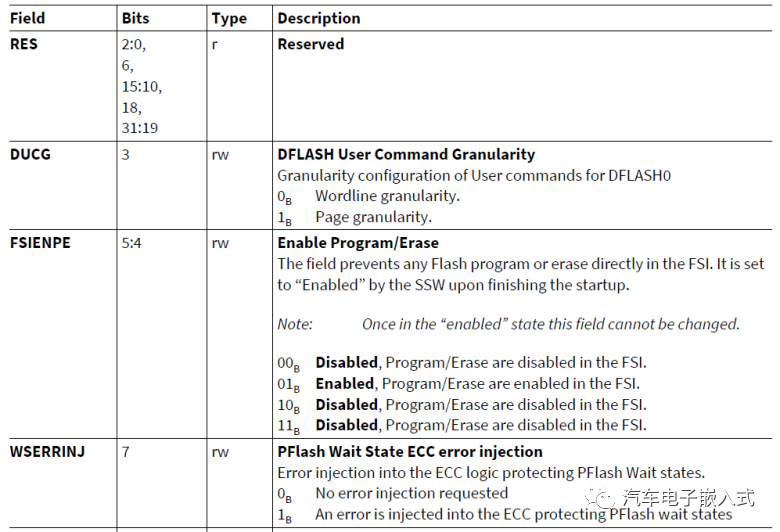

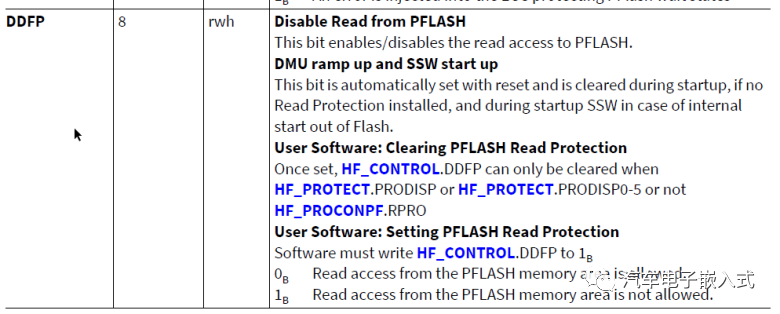

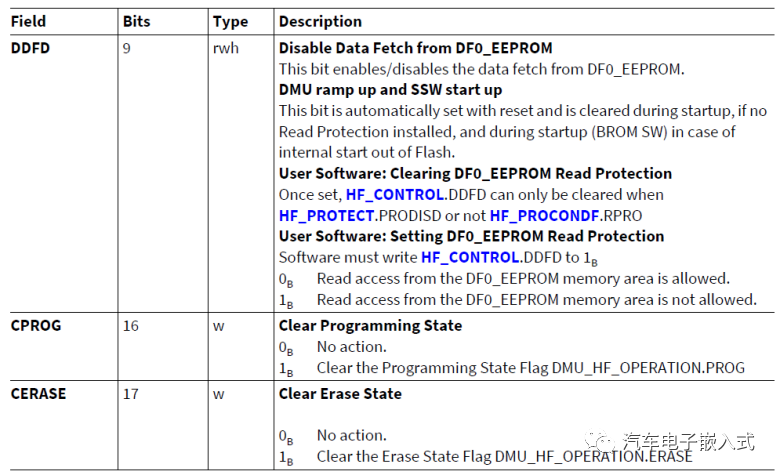

2.2 DMU控制寄存器

DMU控制寄存器HF_CONTROL并不是用来直接操作数据的写入和擦除(数据的写入和擦除由Command Sequence实现,后面章节介绍),而是用来控制/使能一些Flash的全局功能(后面遇到了再展开介绍)。

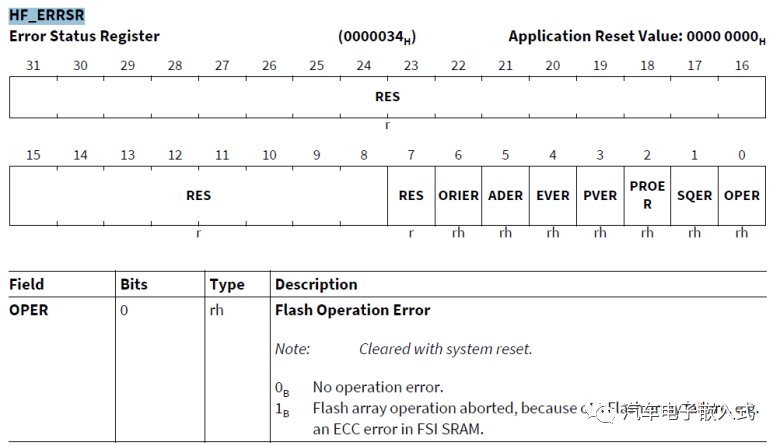

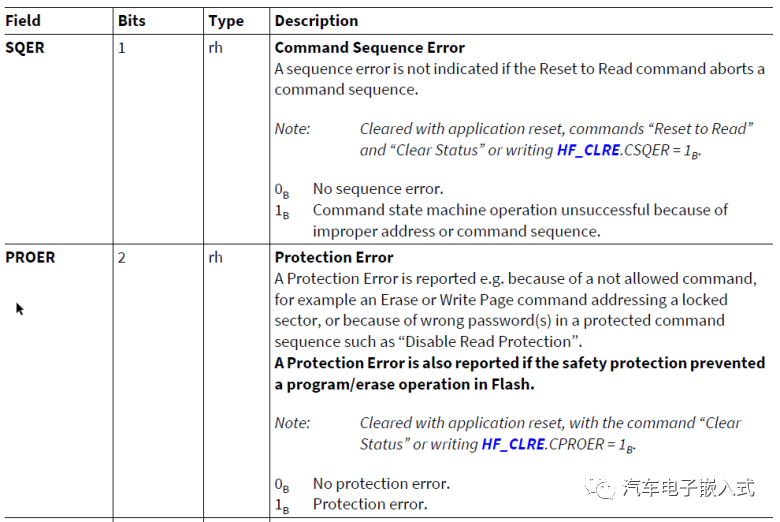

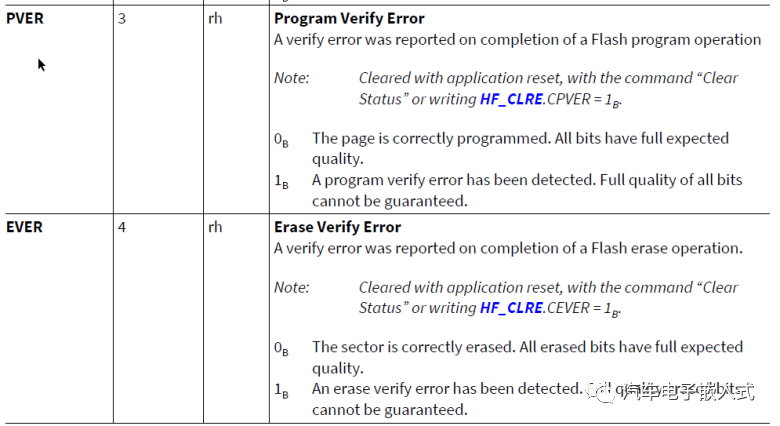

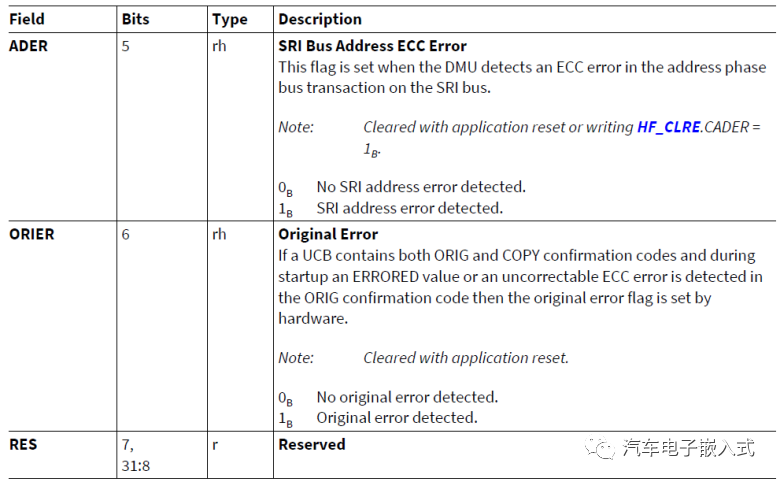

2.3 错误状态寄存器

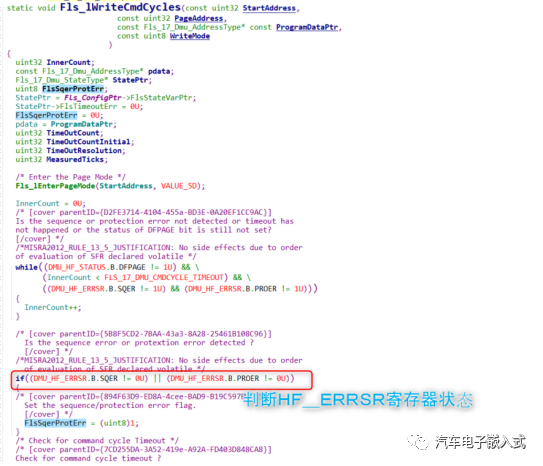

HF_ERRSR错误状态寄存器标识当前Flash有没有发生错误。对每个错误类型的具体解释和检测到错误后建议的软件操作请参考后面的错误处理章节。

Fls模块在执行Flash写操作前也会先检查Flash有没有Error产生,如果有Error产生,则不进行任何操作。

3.DMU命令序列

3.1 读Flash

对Flash的读访问是Memory mapped read,什么意思了?比如我们要读0xAF001234这个起始地址处的一个uint32的数据,我们可以直接操作内存进行读:

uint32 Value = *((uint32 *)0xAF001234);

3.2 写Flash

但是对于Flash的写(Programming)和擦除(Erase)操作不能直接操作内存,需要通过特定的命令序列(Command Sequence),比如以下的操作就是无效的。

*((uint32 *)0xAF001234) = 0xFFFF;

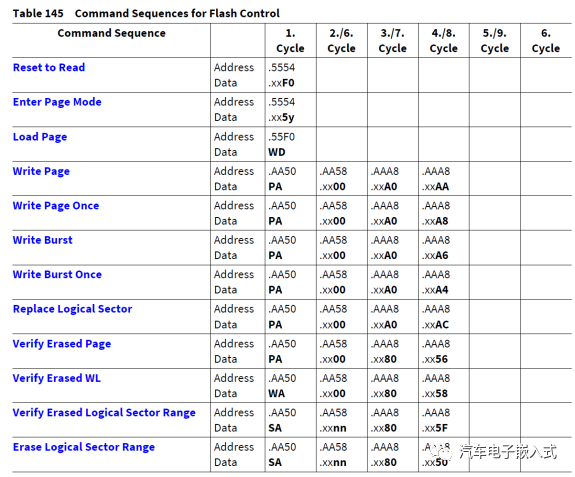

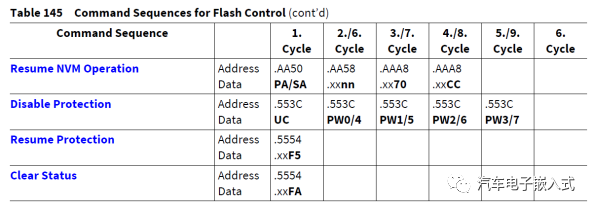

实际对DFlash的写操作需要一组命令序列(Command Sequences)来实现。DMU会把者一组命令序列翻译过来去完成对DFlash的写操作。写的过程中的状态和错误通过HF_STATUS和HF_ERRSR寄存器标识。DMU提供了一些Command Sequence供开发者使用。

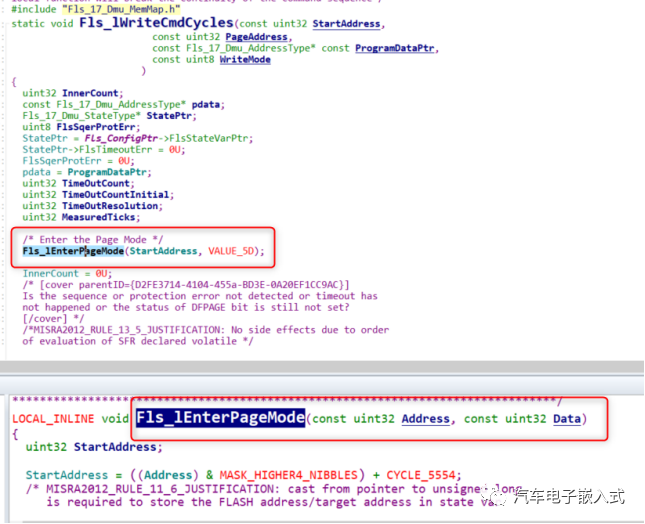

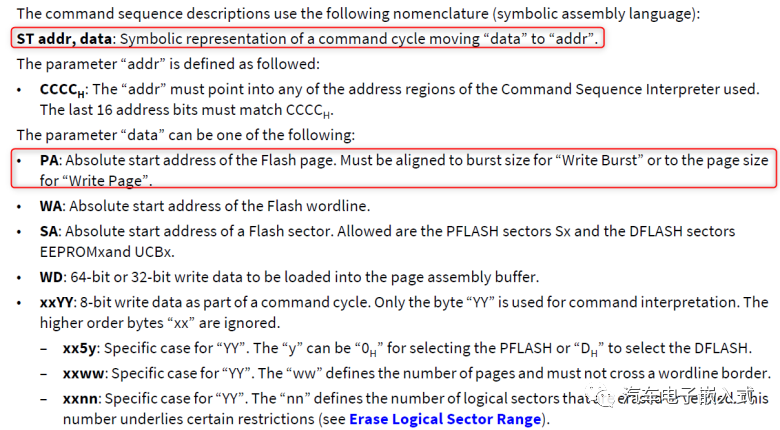

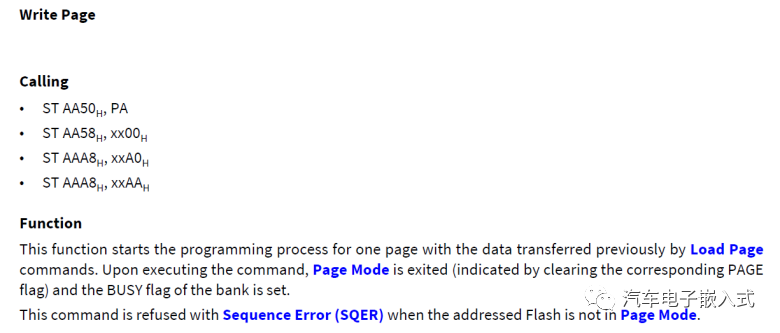

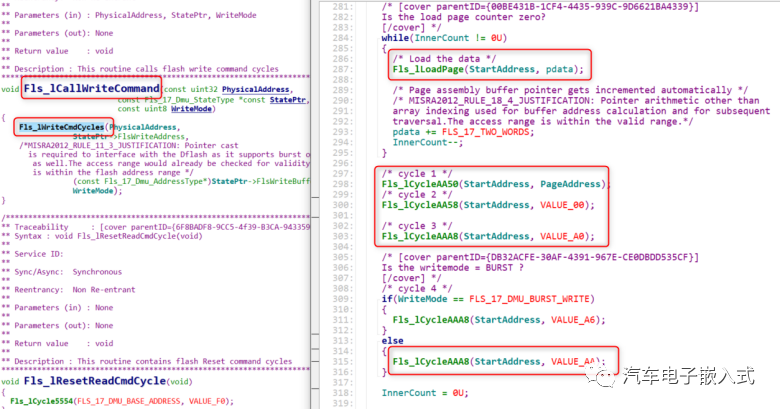

我们来分析一个Write Page的Command Sequence:

第一步:把PA(缓存要写入数据的变量的地址)加载到DFlash Base Address + 0xAA50处

第二步:把xx00H(xx标识的部分被忽略)这个值加载到DFlash Base Address + 0xAA58处

第三步:把xxA0H(xx标识的部分被忽略)这个值加载到DFlash Base Address + 0xAA58处

第四步:把xxAAH(xx标识的部分被忽略)这个值加载到DFlash Base Address + 0xAA58处

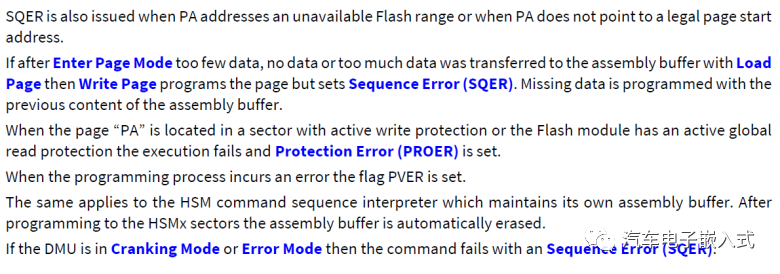

执行Write Page需要注意:

1.Write Page命令序列需要在Load Page命令序列之后执行

2.执行完Write Page命令序列后,PageMode的标志就会在HF_STATUS状态寄存器中被设置

3.如果Flash不在PageMode下执行Write Page操作,那么HF_ERRSR错误状态寄存器的Sequence Error(SQER)标志就会被置位,如果PA地址值不在合肥的地址范围内,SQER标志也会被置位。

4.如果进入Page Mode后数据太少,则没有数据或太多数据通过“LoadPage”传输到程序集缓冲区,“WrtePage”会对页面进行编程,但会设置序列错误 (SQER)。 缺少的数据是使用程序集缓冲区的先前内容进行编程的

5.当页面“ PA ”位于具有有效写入保护的Sector中,或者Flash模块具有有效的全局读取保护时,Write Page就会执行失败并设置保错误 Protection Error(PROER)。

6.当写入(Programming)过程中出现错误,PVER错误标志就会被设置

7.如果DMU处于Cranking Mode或者Error Mode,执行Write Page命令序列就会产生Sequence Error(SQER).

Write Page在代码中的体现:

Note:

1.不要问为什么是这样来实现对DFlash的操作,这是人家芯片厂商规定的,我们照着做就行。

2.命令序列很多,遇到了想了解的话,就按照Write Page这个分析过程去分析就行

4.DMU错误处理

Infineon的芯片手册中对每一种Error产生原因和出现Error后建议的操作都写的非常详细,我们能找到地方并理解就好,这里仅介绍Sequence Error(SQER),其他自己去查手册就好。

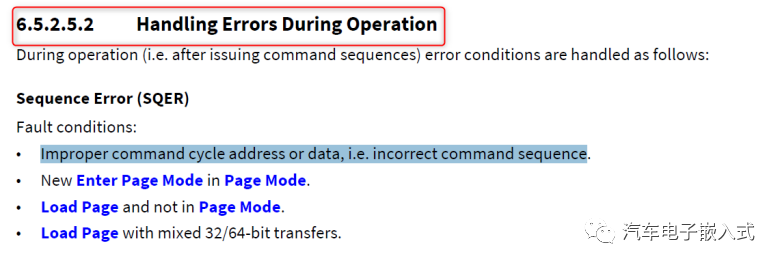

Sequence Error(SQER)产生的原因:

1.Comman的地址或者数据不正确,也就是没有按照规定的CommandSequence来操作Flash

2.DMU处于Page Mode时又尝试进入Page Mode

3.Load Page命令序列不在Page Mode下执行

4.Load Page命令序列混合32/64操作

……太多了,参考<< AURIXTC3XX_um_part1_v2.0.pdf>>以下章节

出现问题后怎么处理:

SQER错误通常就是软件Bug导致的,所有我们把软件写好,这些问题就不会出现。如果出现了这些Error,应该把Error信息通知到应用代码。但是,可以使用“Clear Status”或“Resetto Read”命令序列清除此标志,然后可以再次发出更正后的命令序列。

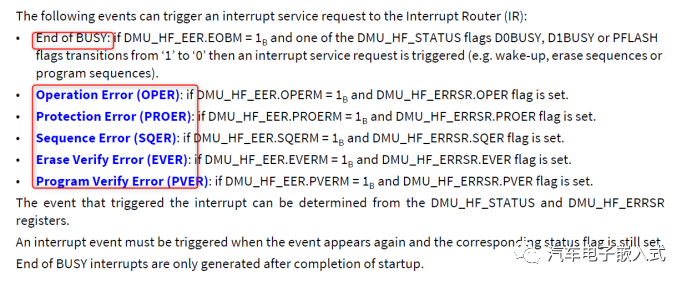

5.DMU中断和Trap

5.1中断

DMU在以下截图的事件触发时可以触发中断,中断使能和中断处理函数需要我们去配置和实现,然后可以通过中断来判断事件完成或错误发生。但是,对Flash操作的状态获取和错误获取一般采用轮询的方式实现。

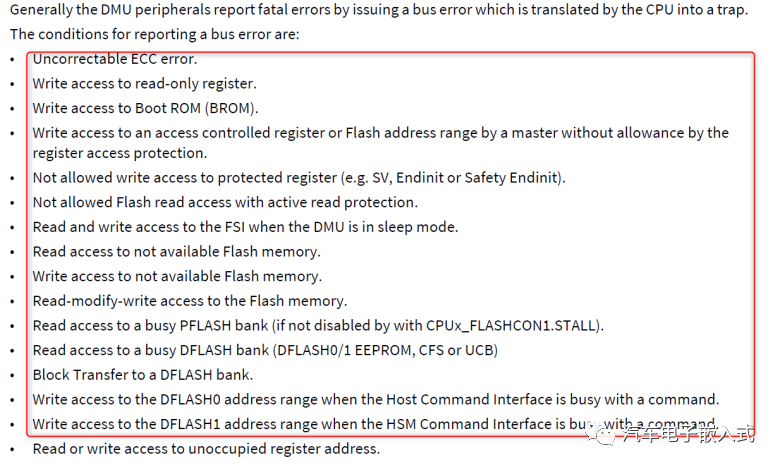

5.2Trap

同样,DMU外设报告以下的Fatal Errors会触发CPU进入Trap。

Note: 这些了解就好,好像在实际工程中没有使用DMU中断,也没去管DMUTrap,回头再仔细研究下。

6.总结

这篇文章的所有内容都可以在Infineon的数据手册中找到,但是对于初学者或者对硬件手册不熟悉的朋友不容易抓到重点(动不动一个章节就是几十上百页的英文,确实看着就头疼…),所以作者结合代码梳理出个人认为对于软件开发者最为重要的内容,希望各位对各位看官有所帮助,也希望对各位新人苦于看数据手册有所启发。

最后,咱们来来回答开头提出的问题结束本文。

问题1:站在软件实现的角度来看,如何通过DMU实现读,写,擦除DFlash?

答:通过Load Page和Write Page命令序列实现写操作;通过Erase Logical Sector Range命令序列实现擦除操作;通过Memory mapped read直接读Flash。

问题2:站在软件实现的角度来看,如何通过DMU监控读,写,擦除DFlash等任务完成的?

答:通过监控HF_STATUS的D0BUSY/D1BUS标志来监控擦写操作,读不用监控,直接读取就行。

问题3:站在软件实现的角度来看,如何通过DMU监控读,写,擦除DFlash等任务出现Error

的?

答:通过监控HF_ERRSR错误状态寄存器的错误标志来监控读,写,擦除DFlash等任务出现Error

类型。

问题4:站在软件实现的角度来看,在监控到读,写,擦除DFlash等任务出现Error后如何恢复重来?

答:太多,这里就不在细讲,具体参考数据手册的Error Handing章节。

审核编辑:汤梓红

-

芯片

+关注

关注

455文章

50711浏览量

423098 -

寄存器

+关注

关注

31文章

5336浏览量

120224 -

接口

+关注

关注

33文章

8573浏览量

151006 -

AUTOSAR

+关注

关注

10文章

360浏览量

21548

原文标题:TC3xx芯片DMU介绍

文章出处:【微信号:汽车电子嵌入式,微信公众号:汽车电子嵌入式】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

英飞凌TC3XX系列多核MCU学习笔记(3)

TC3XX寄存器读写时间过长怎么解决?

TC3xx系列怎么禁用trap?

TC3xx的HSM中有没有单调计数器?

TSIM是否支持TC3xx系列在没有硬件的情况下调试应用程序?

AUTOSAR MCAL-基于Infineon TC3xx芯片的ADC模块

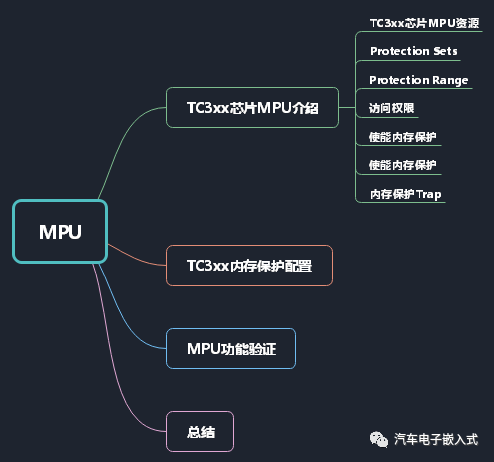

TC3xx芯片的MPU功能详解

TC3xx芯片DMU介绍

TC3xx芯片DMU介绍

评论