本文开源一个FPGA项目:UDP万兆光通信。该项目实现了万兆光纤以太网数据回环传输功能。Vivado工程代码结构和之前开源的《UDP RGMII千兆以太网》类似,只不过万兆以太网是调用了Xilinx的10G Ethernet Subsystem IP核实现。由于该IP核需要付费使用,本文提供完整工程源码。

下面围绕该IP核的使用、用户接口,以及数据传输方案展开介绍。

01软硬件平台

- 软件平台:Vivado 2017.4;

- 硬件平台:XC7Z035FFG676-2;

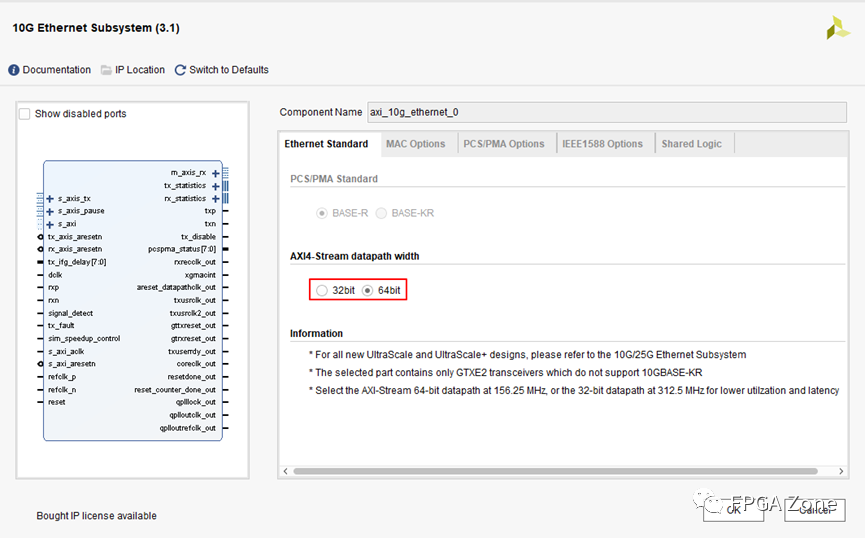

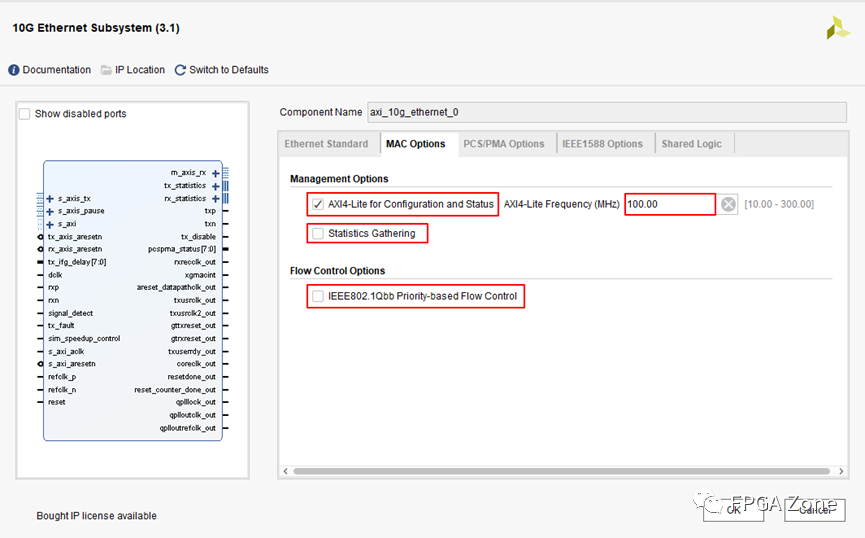

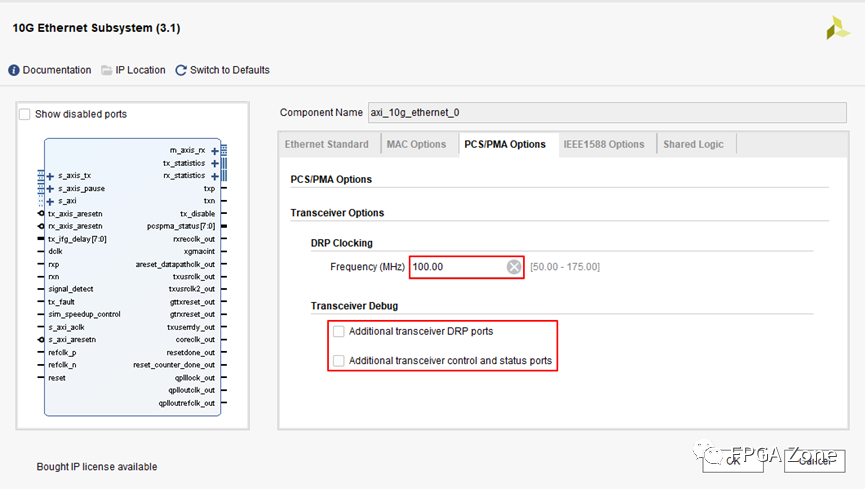

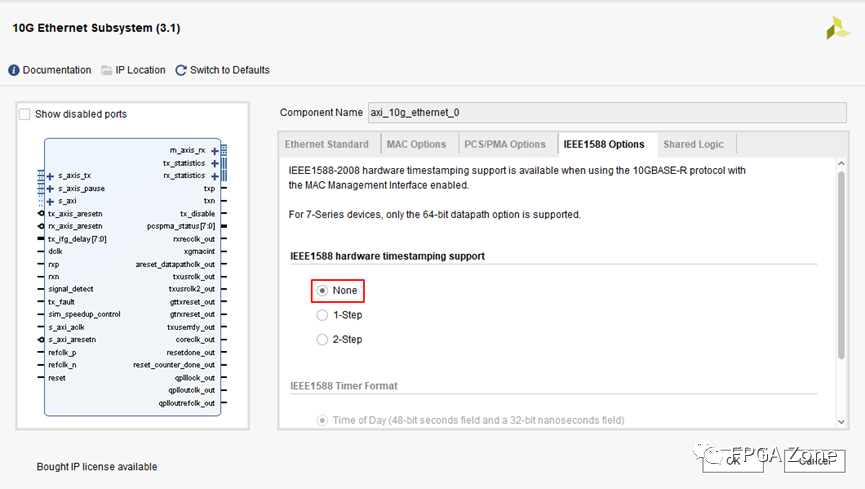

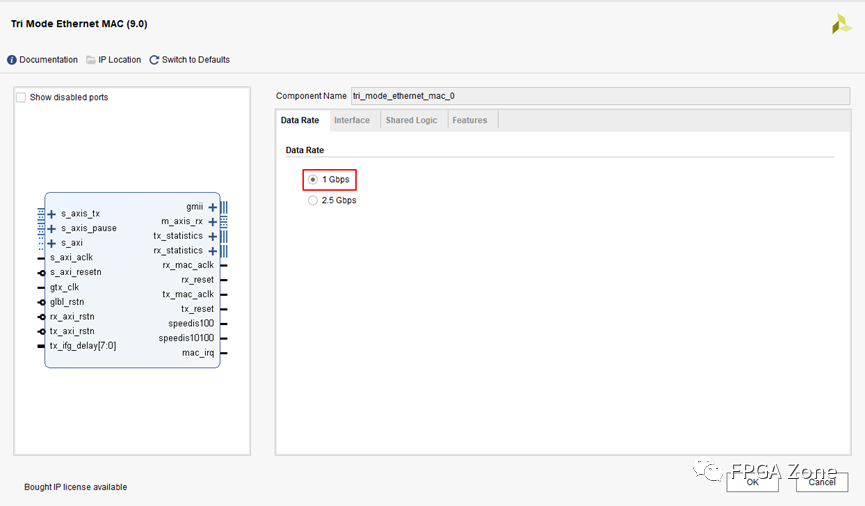

02IP核参数配置

AXI4-Stream数据位宽 : 选择64bits。对应的用户接口时钟频率为156.25MHZ。

MAC Options : 选择使用AXI-Lite接口对IP核寄存器进行配置,同时需要设置时钟频率,这里设置为100MHZ(该设置仅对IP核out-of-context模式的综合有效);不使用参数统计和优先级流量控制功能。

PCS/PMA Options: 配置GTX动态重配置端口DRP时钟为100MHZ(该设置同样仅对IP核out-of-context模式的综合有效);不使用Transceiver Debug功能。

IEEE1588 Options: IEEE1588功能一般用于某些需要进行网络时间同步的场合,例如音(视)频传输。在本项目中只是进行数据传输,因此可以不选择使用。

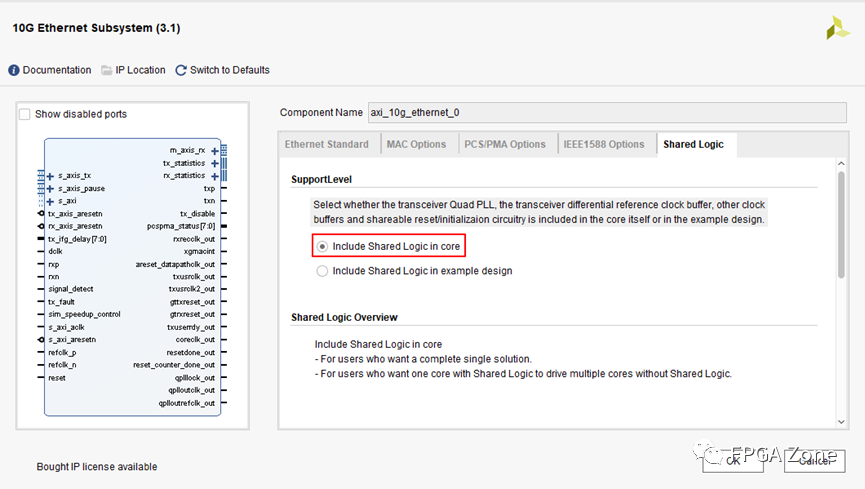

Shared Logic: 由于在此项目Vivado工程中只需例化一个该IP核,因此这里选择Include Shared Logic in core,将共享资源包含在IP内部即可。如果需要例化多个该IP核,只需将其中一个IP核配置为Include Shared Logic in core,其余的都配置为Include Shared Logic in example design。

03用户接口

- AXI-Stream发送接口

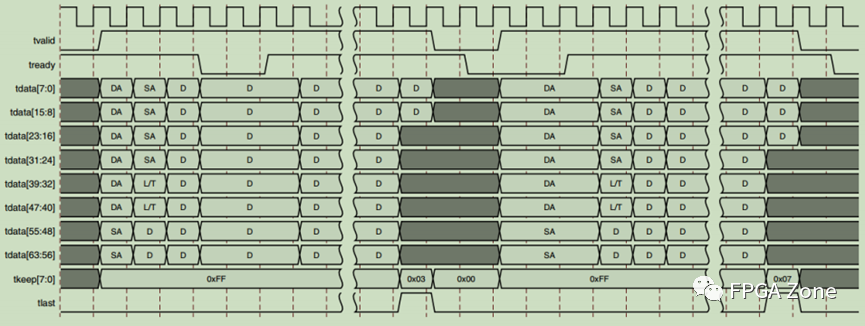

用户通过该接口将要发送的以太网数据包写入IP核。另外,由tx_ifg_delay接口控制发送间隔,将其配置为0即可。AXI-Stream发送接口时序如下图所示。

- AXI-Stream接收接口

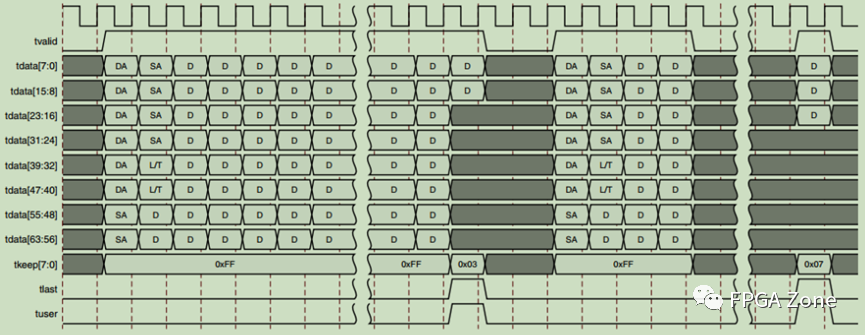

用户通过该接口读取IP核输出的以太网数据包。AXI-Stream接收接口时序如下图所示。

- Pcspma-Status接口

该接口用于输出IP核内部PCS PMA部分工作状态,在该工程中只有第0bit有效,用于指示PCS Block Lock。

- Sim-Speed-Up接口

该接口只在仿真时会用到,用于加快仿真速度,在该工程中将其设置为0即可。

- Optical模块接口

signal_detect:光模块状态指示信号,配置为1;

tx_fault:光模块状态指示信号,配置为0;

tx_disable:输出光模块控制信号。

- Flow-Control接口

在高带宽、大负荷传输场合,一般需要流量控制功能。在该工程不需要发送暂停帧,因此将以下两个信号设置为0。

s_axis_pause_tvalid & s_axis_pause_tdata。

- AXI-Lite接口

该接口用于读写IP核内部寄存器,通过对IP核各参数进行配置,以实现基本的以太网数据包收发功能。

04数据传输方案及测试

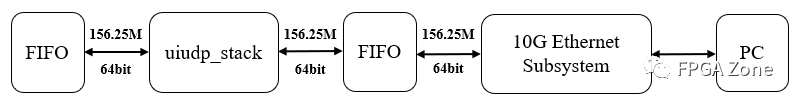

该项目的功能主要用于实现万兆以太网光纤数据回环传输,在电脑端通过网络调试助手向FPGA发送数据包,FPGA端接收、缓存数据包后回传给上位机。以太网数据回环传输方案如下图所示。

其中,时钟为156.25MHZ,数据位宽为64bits。在UDP IP核和10G Ethernet Subsystem IP核之间,通过插入FIFO实现对每包以太网数据流的缓存功能。

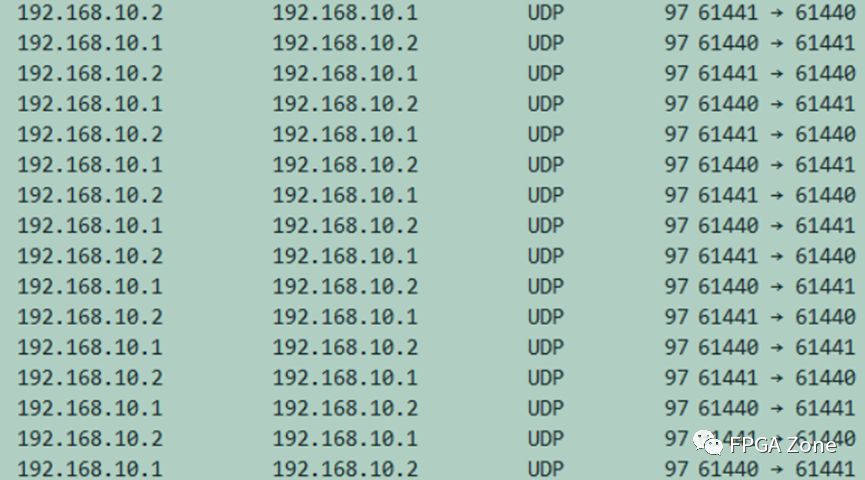

利用wireshark软件抓取PC端和FPGA端之间以太网双向传输数据包,结果如下图所示。

-

FPGA

+关注

关注

1629文章

21729浏览量

602986 -

以太网

+关注

关注

40文章

5419浏览量

171598 -

UDP

+关注

关注

0文章

325浏览量

33931 -

光通信

+关注

关注

19文章

876浏览量

33963 -

IP核

+关注

关注

4文章

327浏览量

49485

发布评论请先 登录

相关推荐

把握光通信行业演变脉动 CIOE2012光通信展即将起航!

FPGA在光通信中的应用

浅析紫外光通信技术

可见光通信 调制解调技术 家庭机器人 可见光通信应用 原理及硬件方案 精选资料分享

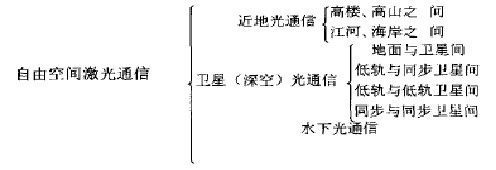

无线光通信

无线光通信技术的应用

无线光通信(FSO),无线光通信(FSO)的特点及原理/前景

光通信芯片的概念以及我国在光通信行业的地位

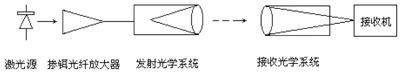

激光通信原理_激光通信的优缺点

光通信的概念 光通信优点与不足

光通信技术应用 光通信的意义

10g gtx光纤通信测试_S03-CH05_UDP万兆光通信

基于FPGA的UDP万兆光通信测试

基于FPGA的UDP万兆光通信测试

评论